A principios de octubre, Xilinx

presentó el nuevo chip Versal, basado en arreglos de compuerta programables (

FPGA ). La lógica del funcionamiento de dicho dispositivo se puede modificar en cualquier momento durante el uso. Se espera que el chip acelere el trabajo de los sistemas de IA y encuentre aplicaciones en redes 5G. El lanzamiento del procesador está programado para finales de 2019.

A continuación, hablamos sobre el dispositivo y cómo ayudará a las redes de próxima generación.

/ Flickr / mike mozart / cc

/ Flickr / mike mozart / ccProblema de red 5G

La tecnología 5G utiliza frecuencias altas (28 GHz y más), por lo que la señal se transmite poco a largas distancias. La ventaja de su propagación se ve fuertemente obstaculizada por las paredes de las casas. En una ciudad, esto puede conducir a una disminución en la calidad de la conexión.

Los expertos

dicen que esto se convertirá en un obstáculo para el trabajo de una gran cantidad de dispositivos IoT, un aumento activo en el número de los cuales se

pronostica a partir de 2020 (justo cuando se desplegarán redes 5G completas).

Los dispositivos conectados, como automóviles o dispositivos médicos portátiles, deben comunicarse en tiempo real. La inestabilidad de la conexión puede evitar que evalúen adecuadamente la situación a su alrededor o transmitan datos vitales (por ejemplo, sobre el estado de la salud humana) a los servidores de la organización en servicio. Las compañías planean resolver este problema organizando sistemas especiales de antenas distribuidas, sin embargo, surgen dificultades con esto.

Por ejemplo, ahora en Nueva York hay más de mil estaciones base instaladas. Para cubrir toda la ciudad con una red 5G,

será necesario instalar otro medio millón . El costo del proyecto será mucho mayor que en el caso de los "estándares G" anteriores.

Cómo Versal ayuda a resolver estos problemas

El dispositivo Xilinx ayudará a resolver los problemas con la estabilidad de la conexión a Internet utilizando sistemas de inteligencia artificial, con los que está "sintonizado" para funcionar. El chip Versal procesará algoritmos de aprendizaje automático en redes 5G que optimizan los patrones de

radiación de las antenas móviles. Esto evitará sectores ciegos y elegirá el modo apropiado de transmisión de datos.

Los sistemas de IA también mejorarán los algoritmos de

transferencia , que son responsables de transferir las sesiones de una estación a otra. Además, las redes se repararán y adaptarán automáticamente, redirigiendo automáticamente los datos si falla algún nodo. Por lo tanto, los usuarios de 5G podrán moverse libremente por un edificio o ciudad sin una falla de conexión.

Xilinx ya tiene clientes para chips AI para 5G. Los procesadores Versal se utilizarán para la creación de redes en los Juegos Olímpicos de 2020.

Características de la arquitectura del chip.

Xilinx introdujo el concepto Versal en octubre. El nuevo microcircuito es

heterogéneo , es decir, utiliza varias unidades informáticas a la vez. Estas unidades pueden ser procesadores, coprocesadores, circuitos integrados ASIC y FPGA.

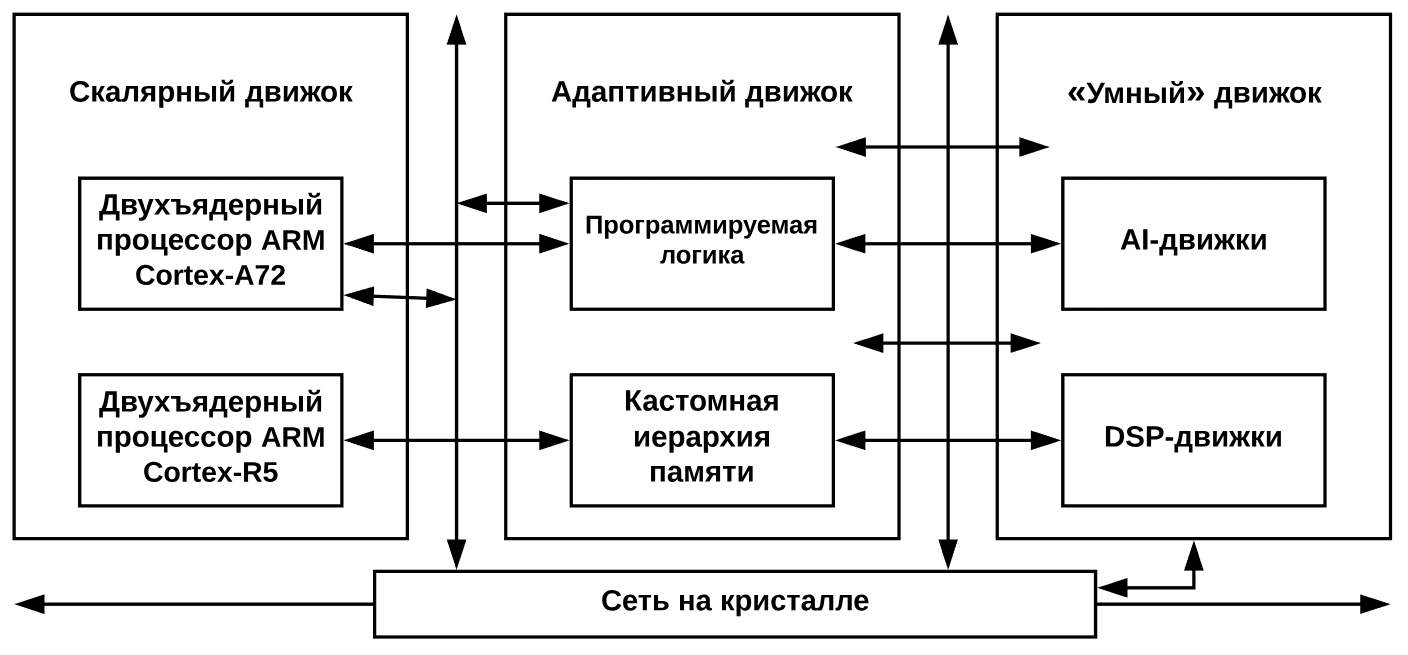

El nuevo chip Xilinx se basa en una versión mejorada de FPGA: la arquitectura Adaptive Computer Accelerator Platform (ACAP). Consta de cuatro componentes básicos: un motor

escalar , un motor adaptativo, aceleradores

vectoriales (motor "inteligente") y una red en un chip (NoC - Network-on-Chip) para conectar elementos del sistema.

El motor escalar está representado por los procesadores ARM Cortex-A72 y Cortex-R5 de doble núcleo. La lógica programable se basa en

elementos lógicos configurables con

tablas de búsqueda ,

disparadores , memoria y bloques especiales para vincular componentes. Todo esto le permite construir una

jerarquía de memoria , agudizada para una tarea computacional específica.

El motor "inteligente" se basa en la

arquitectura VLIW , que es necesaria para la ejecución paralela de varias operaciones en una sola instrucción. El principio de los cálculos

SIMD también se aplica. Dicha estructura ayuda a resolver problemas de MO y procesar señales de 5 a 10 veces más rápido que los sistemas clásicos. En cuanto a NoC, su ancho de banda declarado es de 1 Tbps.

El diagrama de arquitectura ACAP se ve así.

La familia de chips Versal se producirá en TSMC utilizando una tecnología de proceso de

7 nm . Se pueden encontrar otras características arquitectónicas en los documentos PDF oficiales:

resumen de la arquitectura ASAP y

revisión del chip Versal .

El sistema está programado en C, C ++ y Python. Según los desarrolladores, optaron por estos PL, ya que según

TIOBE , C, C ++ y Python son los más populares después de Java.

Además, estos idiomas se complementan entre sí. C y C ++ están compilados, lo que significa que el código puede ejecutarse en metal desnudo (en particular, en FPGA). Python es mejor que nadie para analizar datos y trabajar con sistemas de inteligencia artificial. Otras razones para elegir Xilinx se encuentran en un estudio separado sobre el tema (

PDF ).

Soluciones similares

Los chips basados en FPGA también están siendo desarrollados por otras compañías, como Intel. Entre los últimos productos de la compañía, se puede distinguir el

dispositivo híbrido Arria . El desarrollo es una plataforma de dos chips: Xeon E5-2600 v4 y

Altera Arria 10 .

Según Intel, el dispositivo es adecuado para servidores, centros de datos y servicios en la nube, donde la carga a menudo aumenta espasmódicamente. Un procesador en el FPGA ayudará a procesar los datos en paralelo, lo que aumentará el rendimiento general del sistema. Fujitsu, por ejemplo,

planea suministrar su línea de servidores Primergy con este chip para fin de año.

Otros actores del mercado, AMD, ARM, Qualcomm, Samsung y otros, crearon la organización sin fines de lucro

HSA Foundation en 2012. Allí se popularizan los cálculos heterogéneos: desarrollan estándares industriales, ayudan a los desarrolladores a ingresar al mercado y patrocinan programas educativos.

Xilinx

cree que con el desarrollo de sistemas de IA y la difusión de redes 5G, la demanda de plataformas FPGA aumentará. El CEO de Xilinx, Victor Peng,

señala que el único obstáculo para la producción en masa de chips es la competencia de la CPU y la GPU, que impide que las soluciones FPGA "capturen" el mercado. Pero, probablemente, no se debe esperar un salto en la demanda (si sucede)

antes de 2020 .

PD Materiales adicionales del blog corporativo de expertos en VAS:

PPS Un par de artículos nuevos de nuestro blog sobre Habré: