En la

parte anterior, examinamos la evolución de la entrega de interrupciones desde dispositivos en sistemas x86 (PIC → APIC → MSI), una teoría general y todos los términos necesarios.

En esta parte práctica, veremos cómo volver a usar los métodos de entrega de interrupción de Linux heredados, a saber, considere las opciones de arranque del kernel:

También veremos el orden en que el sistema operativo mira las tablas de enrutamiento de interrupción (ACPI / MPtable / $ PIR) y qué efecto tendrá al agregar opciones de arranque:

- pci = noacpi

- acpi = noirq

- acpi = apagado

Quizás haya intentado combinaciones de todas estas opciones cuando un dispositivo no funcionó debido a un problema de interrupción. Veamos qué hacen exactamente y cómo cambian la salida de / proc / interrupts.

Descargar sin opciones adicionales

Observaremos interrupciones en este artículo en una placa personalizada con Intel Haswell i7 con el chipset lynxPoint-LP en el que se ejecuta

coreboot .

Emitiremos información sobre las interrupciones a través del comando

cat /proc/interrupts

Salida en el arranque sin opciones adicionales:

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 0 1 0 1 IO-APIC-edge i8042 8: 0 0 0 1 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-fasteoi acpi 12: 0 0 0 1 IO-APIC-edge 23: 16 247 7 10 IO-APIC-fasteoi ehci_hcd:usb1 56: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 57: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 58: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 59: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 60: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 61: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 62: 3118 1984 972 3454 PCI-MSI-edge ahci 63: 1 0 0 0 PCI-MSI-edge eth59 64: 2095 57 4 832 PCI-MSI-edge eth59-rx-0 65: 6 18 1 1309 PCI-MSI-edge eth59-rx-1 66: 13 512 2 1 PCI-MSI-edge eth59-rx-2 67: 10 61 232 2 PCI-MSI-edge eth59-rx-3 68: 169 0 0 0 PCI-MSI-edge eth59-tx-0 69: 14 14 4 205 PCI-MSI-edge eth59-tx-1 70: 11 491 3 0 PCI-MSI-edge eth59-tx-2 71: 20 19 134 50 PCI-MSI-edge eth59-tx-3 72: 0 0 0 0 PCI-MSI-edge eth58 73: 2 1 0 152 PCI-MSI-edge eth58-rx-0 74: 3 150 2 0 PCI-MSI-edge eth58-rx-1 75: 2 34 117 2 PCI-MSI-edge eth58-rx-2 76: 153 0 2 0 PCI-MSI-edge eth58-rx-3 77: 4 0 2 149 PCI-MSI-edge eth58-tx-0 78: 4 149 2 0 PCI-MSI-edge eth58-tx-1 79: 4 0 117 34 PCI-MSI-edge eth58-tx-2 80: 153 0 2 0 PCI-MSI-edge eth58-tx-3 81: 66 106 2 101 PCI-MSI-edge snd_hda_intel 82: 928 5657 262 224 PCI-MSI-edge i915 83: 545 56 32 15 PCI-MSI-edge snd_hda_intel NMI: 0 0 0 0 Non-maskable interrupts LOC: 4193 3644 3326 3499 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 290 233 590 111 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1339 2163 2404 1946 Rescheduling interrupts CAL: 607 537 475 559 Function call interrupts TLB: 163 202 164 251 TLB shootdowns TRM: 48 48 48 48 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 3 3 3 3 Machine check polls ERR: 0 MIS: 0

El archivo / proc / interrupts proporciona una tabla sobre el número de interrupciones en cada procesador en la siguiente forma:

- Primera columna: número de interrupción

- Altavoces CPUx: interruptores de contadores en cada procesador

- Siguiente columna: tipo de interrupción:

- IO-APIC-edge - interrupción de borde al controlador I / O APIC

- IO-APIC-fasteoi - interrupción de nivel por controlador I / O APIC

- PCI-MSI-edge - interrupción de MSI

- XT-PIC-XT-PIC - interrupción en el controlador PIC (ver más adelante)

- Última columna: dispositivo asociado con esta interrupción

Entonces, como debería ser en un sistema moderno, se usan para dispositivos y controladores que admiten interrupciones MSI / MSI-X. Las interrupciones restantes se enrutan a través del I / O APIC.

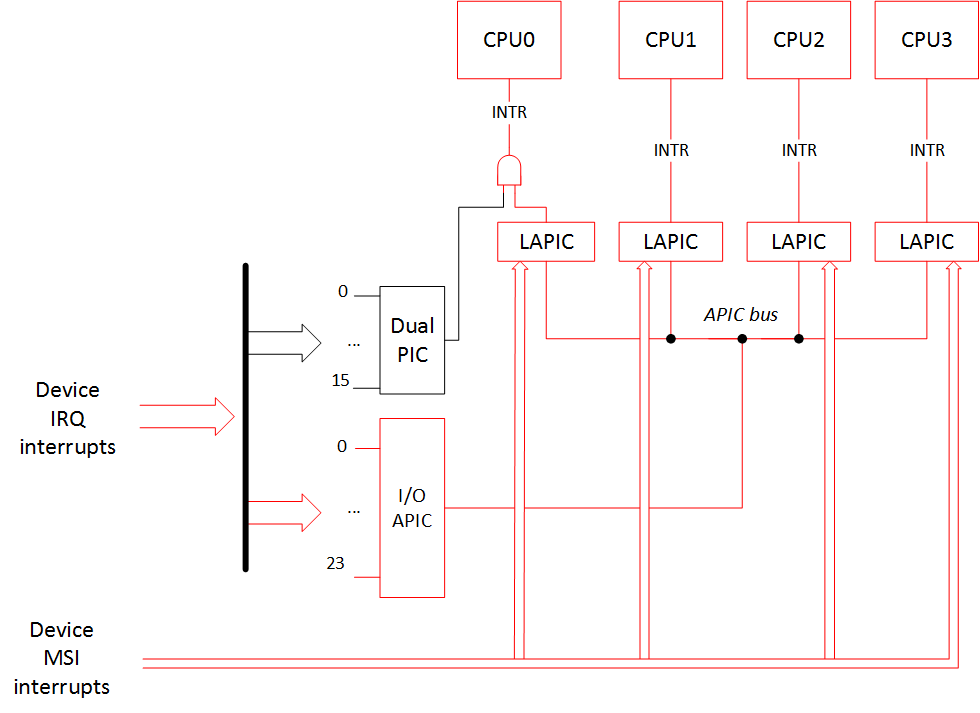

El esquema de enrutamiento de interrupción simplificado se puede dibujar de esta manera (rutas activas marcadas en rojo, rutas no utilizadas en negro).

El soporte para un dispositivo MSI / MSI-X debe etiquetarse como Capacidad correspondiente en su espacio de configuración PCI.

En confirmación, damos un pequeño fragmento de la salida lspci para dispositivos para los que se indica que usan MSI / MSI-X. En nuestro caso, es un controlador SATA (interrupción ahci), 2 controladores de ethernet (interrupciones eth58 * y eth59 *), un controlador gráfico (i915) y 2 controladores de audio HD (snd_hda_intel).

lspci -v

00:02.0 VGA compatible controller: Intel Corporation Haswell-ULT Integrated Graphics Controller (rev 09) (prog-if 00 [VGA controller]) ... Capabilities: [90] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [d0] Power Management version 2 Capabilities: [a4] PCI Advanced Features Kernel driver in use: i915 00:03.0 Audio device: Intel Corporation Haswell-ULT HD Audio Controller (rev 09 ... Capabilities: [60] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [70] Express Root Complex Integrated Endpoint, MSI 00 Kernel driver in use: snd_hda_intel 00:1b.0 Audio device: Intel Corporation 8 Series HD Audio Controller (rev 04) ... Capabilities: [60] MSI: Enable+ Count=1/1 Maskable- 64bit+ Capabilities: [70] Express Root Complex Integrated Endpoint, MSI 00 Capabilities: [100] Virtual Channel Kernel driver in use: snd_hda_intel 00:1f.2 SATA controller: Intel Corporation 8 Series SATA Controller 1 [AHCI mode] (rev 04) (prog-if 01 [AHCI 1.0]) ... Capabilities: [80] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [70] Power Management version 3 Capabilities: [a8] SATA HBA v1.0 Kernel driver in use: ahci 05:00.0 Ethernet controller: Intel Corporation I350 Gigabit Network Connection (rev 01) ... Capabilities: [50] MSI: Enable- Count=1/1 Maskable+ 64bit+ Capabilities: [70] MSI-X: Enable+ Count=10 Masked- Capabilities: [a0] Express Endpoint, MSI 00 Kernel driver in use: igb 05:00.1 Ethernet controller: Intel Corporation I350 Gigabit Network Connection (rev 01) ... Capabilities: [50] MSI: Enable- Count=1/1 Maskable+ 64bit+ Capabilities: [70] MSI-X: Enable+ Count=10 Masked- Capabilities: [a0] Express Endpoint, MSI 00 Kernel driver in use: igb

Como podemos ver, estos dispositivos tienen la línea "MSI: Enable +" o "MSI-X: Enable +"

Comencemos a degradar el sistema. Primero, arranque con la opción pci = nomsi.

pci = nomsi

Con esta opción, las interrupciones de MSI se convertirán en IO-APIC / XT-PIC dependiendo del controlador de interrupción utilizado.

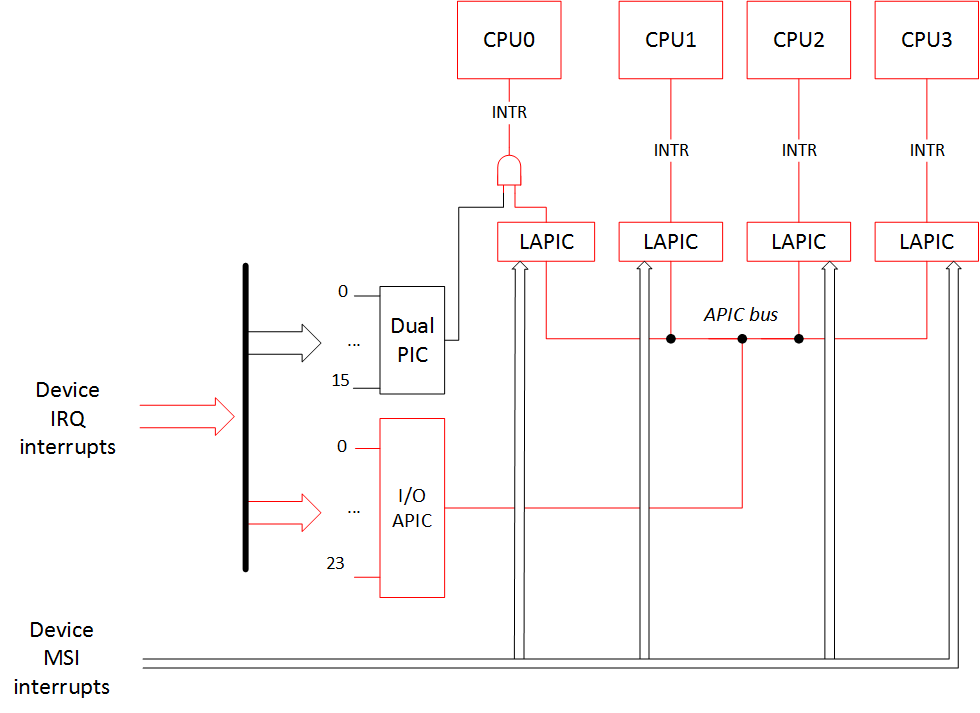

En este caso, todavía tenemos el controlador de interrupción APIC prioritario, por lo que la imagen será la siguiente:

La salida de / proc / interrumpe:

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 0 1 0 1 IO-APIC-edge i8042 8: 0 0 1 0 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-fasteoi acpi 12: 0 0 0 1 IO-APIC-edge 16: 1314 5625 342 555 IO-APIC-fasteoi i915, snd_hda_intel, eth59 17: 5 0 1 34 IO-APIC-fasteoi eth58 21: 2882 2558 963 2088 IO-APIC-fasteoi ahci 22: 26 81 2 170 IO-APIC-fasteoi snd_hda_intel 23: 23 369 8 8 IO-APIC-fasteoi ehci_hcd:usb1 NMI: 0 0 0 0 Non-maskable interrupts LOC: 3011 3331 2435 2617 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 197 228 544 85 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1708 2349 1821 1569 Rescheduling interrupts CAL: 520 554 509 555 Function call interrupts TLB: 187 181 205 179 TLB shootdowns TRM: 102 102 102 102 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Se espera que todas las interrupciones MSI / MSI-X desaparezcan. En cambio, los dispositivos ahora usan interrupciones IO-APIC-fasteoi.

¡Tenga en cuenta que antes de incluir esta opción, eth58 y eth59 tenían 9 interrupciones cada una! Y ahora solo uno a la vez. De hecho, como recordamos, sin MSI una función PCI, ¡solo hay una interrupción disponible!

Alguna información de dmesg sobre la inicialización de controladores de ethernet:

- Descargar sin la opción pci = nomsi:

igb: Intel(R) Gigabit Ethernet Network Driver - version 5.0.5-k igb: Copyright (c) 2007-2013 Intel Corporation. acpi:acpi_pci_irq_enable: igb 0000:05:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16 igb 0000:05:00.0: irq 63 for MSI/MSI-X igb 0000:05:00.0: irq 64 for MSI/MSI-X igb 0000:05:00.0: irq 65 for MSI/MSI-X igb 0000:05:00.0: irq 66 for MSI/MSI-X igb 0000:05:00.0: irq 67 for MSI/MSI-X igb 0000:05:00.0: irq 68 for MSI/MSI-X igb 0000:05:00.0: irq 69 for MSI/MSI-X igb 0000:05:00.0: irq 70 for MSI/MSI-X igb 0000:05:00.0: irq 71 for MSI/MSI-X igb 0000:05:00.0: irq 63 for MSI/MSI-X igb 0000:05:00.0: irq 64 for MSI/MSI-X igb 0000:05:00.0: irq 65 for MSI/MSI-X igb 0000:05:00.0: irq 66 for MSI/MSI-X igb 0000:05:00.0: irq 67 for MSI/MSI-X igb 0000:05:00.0: irq 68 for MSI/MSI-X igb 0000:05:00.0: irq 69 for MSI/MSI-X igb 0000:05:00.0: irq 70 for MSI/MSI-X igb 0000:05:00.0: irq 71 for MSI/MSI-X igb 0000:05:00.0: added PHC on eth0 igb 0000:05:00.0: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.0: eth0: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2a igb 0000:05:00.0: eth0: PBA No: 106300-000 igb 0000:05:00.0: Using MSI-X interrupts. 4 rx queue(s), 4 tx queue(s) acpi:acpi_pci_irq_enable: igb 0000:05:00.1: PCI INT B -> GSI 17 (level, low) -> IRQ 17 igb 0000:05:00.1: irq 72 for MSI/MSI-X igb 0000:05:00.1: irq 73 for MSI/MSI-X igb 0000:05:00.1: irq 74 for MSI/MSI-X igb 0000:05:00.1: irq 75 for MSI/MSI-X igb 0000:05:00.1: irq 76 for MSI/MSI-X igb 0000:05:00.1: irq 77 for MSI/MSI-X igb 0000:05:00.1: irq 78 for MSI/MSI-X igb 0000:05:00.1: irq 79 for MSI/MSI-X igb 0000:05:00.1: irq 80 for MSI/MSI-X igb 0000:05:00.1: irq 72 for MSI/MSI-X igb 0000:05:00.1: irq 73 for MSI/MSI-X igb 0000:05:00.1: irq 74 for MSI/MSI-X igb 0000:05:00.1: irq 75 for MSI/MSI-X igb 0000:05:00.1: irq 76 for MSI/MSI-X igb 0000:05:00.1: irq 77 for MSI/MSI-X igb 0000:05:00.1: irq 78 for MSI/MSI-X igb 0000:05:00.1: irq 79 for MSI/MSI-X igb 0000:05:00.1: irq 80 for MSI/MSI-X igb 0000:05:00.1: added PHC on eth1 igb 0000:05:00.1: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.1: eth1: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2b igb 0000:05:00.1: eth1: PBA No: 106300-000 igb 0000:05:00.1: Using MSI-X interrupts. 4 rx queue(s), 4 tx queue(s)

- arranque con la opción pci = nomsi

igb: Intel(R) Gigabit Ethernet Network Driver - version 5.0.5-k igb: Copyright (c) 2007-2013 Intel Corporation. acpi:acpi_pci_irq_enable: igb 0000:05:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16 igb 0000:05:00.0: added PHC on eth0 igb 0000:05:00.0: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.0: eth0: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2a igb 0000:05:00.0: eth0: PBA No: 106300-000 igb 0000:05:00.0: Using legacy interrupts. 1 rx queue(s), 1 tx queue(s) acpi:acpi_pci_irq_enable: igb 0000:05:00.1: PCI INT B -> GSI 17 (level, low) -> IRQ 17 igb 0000:05:00.1: added PHC on eth1 igb 0000:05:00.1: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.1: eth1: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2b igb 0000:05:00.1: eth1: PBA No: 106300-000 igb 0000:05:00.1: Using legacy interrupts. 1 rx queue(s), 1 tx queue(s)

Debido a la reducción en el número de interrupciones por dispositivo, habilitar esta opción puede limitar significativamente el rendimiento del controlador (esto no tiene en cuenta el hecho de que según Intel

Reducción de la latencia de interrupción mediante el uso de interrupciones señalizadas por mensaje, las interrupciones a través de MSI son 3 veces más rápidas que a través de IO -APIC y 5 veces más rápido que a través de PIC).

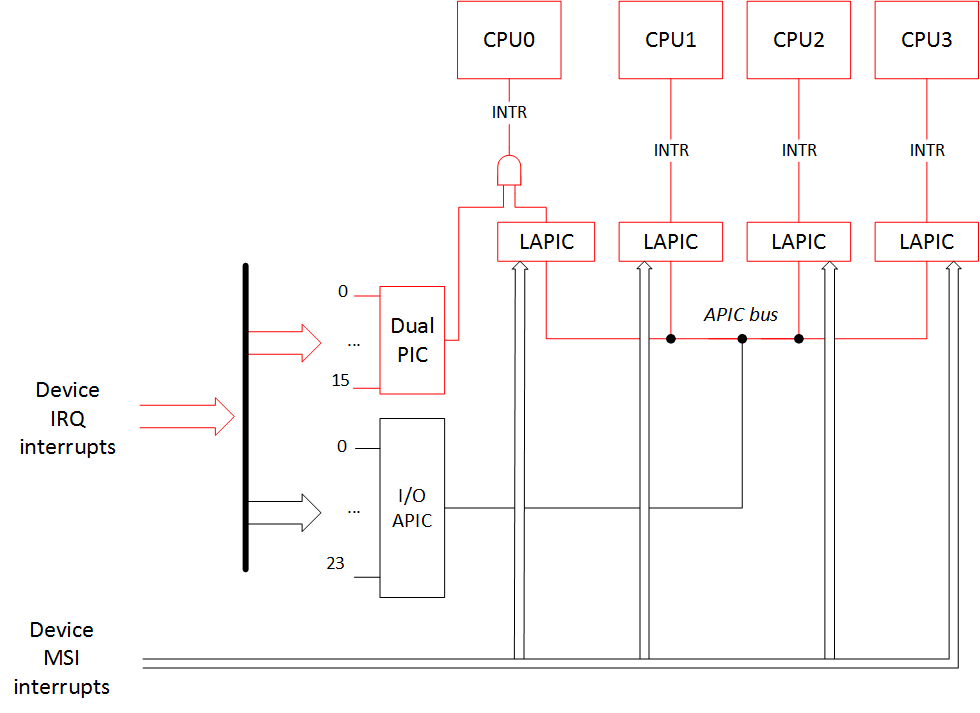

noapic

Esta opción deshabilita I / O APIC. Las interrupciones de MSI aún pueden ir a todas las CPU, pero las interrupciones de los dispositivos solo pueden ir a la CPU0, ya que el PIC solo está conectado a la CPU0. Pero LAPIC funciona y otras CPU pueden funcionar y manejar interrupciones.

CPU0 CPU1 CPU2 CPU3 0: 5 0 0 0 XT-PIC-XT-PIC timer 1: 2 0 0 0 XT-PIC-XT-PIC i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 8: 1 0 0 0 XT-PIC-XT-PIC rtc0 9: 0 0 0 0 XT-PIC-XT-PIC acpi 12: 172 0 0 0 XT-PIC-XT-PIC ehci_hcd:usb1 56: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 57: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 58: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 59: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 60: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 61: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 62: 2833 2989 1021 811 PCI-MSI-edge ahci 63: 0 1 0 0 PCI-MSI-edge eth59 64: 301 52 9 3 PCI-MSI-edge eth59-rx-0 65: 12 24 3 178 PCI-MSI-edge eth59-rx-1 66: 14 85 6 2 PCI-MSI-edge eth59-rx-2 67: 17 24 307 1 PCI-MSI-edge eth59-rx-3 68: 70 18 8 10 PCI-MSI-edge eth59-tx-0 69: 7 0 0 23 PCI-MSI-edge eth59-tx-1 70: 15 227 2 2 PCI-MSI-edge eth59-tx-2 71: 18 6 27 2 PCI-MSI-edge eth59-tx-3 72: 0 0 0 0 PCI-MSI-edge eth58 73: 1 0 0 27 PCI-MSI-edge eth58-rx-0 74: 1 22 0 5 PCI-MSI-edge eth58-rx-1 75: 1 0 22 5 PCI-MSI-edge eth58-rx-2 76: 23 0 0 5 PCI-MSI-edge eth58-rx-3 77: 1 0 0 27 PCI-MSI-edge eth58-tx-0 78: 1 22 0 5 PCI-MSI-edge eth58-tx-1 79: 1 0 22 5 PCI-MSI-edge eth58-tx-2 80: 23 0 0 5 PCI-MSI-edge eth58-tx-3 81: 187 17 70 7 PCI-MSI-edge snd_hda_intel 82: 698 1647 247 129 PCI-MSI-edge i915 83: 438 135 16 59 PCI-MSI-edge snd_hda_intel NMI: 0 0 0 0 Non-maskable interrupts LOC: 1975 2499 2245 1474 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 132 67 429 91 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1697 2178 1903 1541 Rescheduling interrupts CAL: 561 496 534 567 Function call interrupts TLB: 229 254 170 137 TLB shootdowns TRM: 78 78 78 78 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Como puede ver, todas las interrupciones IO-APIC- * se convirtieron en XT-PIC-XT-PIC, y estas interrupciones se enrutan solo en la CPU0. Las interrupciones de MSI permanecen sin cambios y van a todas las CPU0-3.

nolapic

Inhabilita LAPIC. Las interrupciones de MSI no pueden funcionar sin LAPIC, I / O APIC no puede funcionar sin LAPIC. Por lo tanto, todas las interrupciones de los dispositivos irán al PIC, y solo funciona con CPU0. Y sin LAPIC, otras CPU ni siquiera funcionarán en el sistema.

La salida de / proc / interrumpe:

CPU0 0: 6416 XT-PIC-XT-PIC timer 1: 2 XT-PIC-XT-PIC i8042 2: 0 XT-PIC-XT-PIC cascade 3: 5067 XT-PIC-XT-PIC aerdrv, aerdrv, PCIe PME, PCIe PME, i915, snd_hda_intel, eth59 4: 32 XT-PIC-XT-PIC aerdrv, aerdrv, PCIe PME, PCIe PME, eth58 5: 0 XT-PIC-XT-PIC aerdrv, PCIe PME 6: 0 XT-PIC-XT-PIC aerdrv, PCIe PME 8: 1 XT-PIC-XT-PIC rtc0 9: 0 XT-PIC-XT-PIC acpi 11: 274 XT-PIC-XT-PIC snd_hda_intel 12: 202 XT-PIC-XT-PIC ehci_hcd:usb1 15: 7903 XT-PIC-XT-PIC ahci NMI: 0 Non-maskable interrupts LOC: 0 Local timer interrupts SPU: 0 Spurious interrupts PMI: 0 Performance monitoring interrupts IWI: 0 IRQ work interrupts RTR: 0 APIC ICR read retries RES: 0 Rescheduling interrupts CAL: 0 Function call interrupts TLB: 0 TLB shootdowns TRM: 0 Thermal event interrupts THR: 0 Threshold APIC interrupts MCE: 0 Machine check exceptions MCP: 1 Machine check polls ERR: 0 MIS: 0

Combinaciones:

De hecho, solo hay uno para la nueva versión: "noapic pci = nomsi". Todas las interrupciones de los dispositivos solo pueden pasar a la CPU0 a través del PIC. Pero LAPIC funciona y otras CPU pueden funcionar y manejar interrupciones.

Uno, porque no se puede combinar nada con "nolapic", porque esta opción hará que I / O APIC y MSI no estén disponibles. Entonces, si alguna vez prescribió las opciones de arranque "noapic nolapic" (o la opción más común "acpi = off noapic nolapic"), aparentemente escribió letras adicionales.

Entonces, ¿qué pasará con las opciones "noapic pci = nomsi":

La salida de / proc / interrumpe:

CPU0 CPU1 CPU2 CPU3 0: 5 0 0 0 XT-PIC-XT-PIC timer 1: 2 0 0 0 XT-PIC-XT-PIC i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 3: 5072 0 0 0 XT-PIC-XT-PIC i915, snd_hda_intel, eth59 4: 32 0 0 0 XT-PIC-XT-PIC eth58 8: 1 0 0 0 XT-PIC-XT-PIC rtc0 9: 0 0 0 0 XT-PIC-XT-PIC acpi 11: 281 0 0 0 XT-PIC-XT-PIC snd_hda_intel 12: 200 0 0 0 XT-PIC-XT-PIC ehci_hcd:usb1 15: 7930 0 0 0 XT-PIC-XT-PIC ahci NMI: 0 0 0 0 Non-maskable interrupts LOC: 2595 2387 2129 1697 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 159 90 482 135 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1568 1666 1810 1833 Rescheduling interrupts CAL: 431 556 549 558 Function call interrupts TLB: 124 184 156 274 TLB shootdowns TRM: 116 116 116 116 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Tablas y opciones de enrutamiento de interrupción "acpi = noirq", "pci = noacpi", "acpi = off"

¿Cómo recibe el sistema operativo la información de enrutamiento de interrupción de los dispositivos? El BIOS prepara información para el sistema operativo en forma de:

- Tablas ACPI (métodos _PIC / _PRT)

- _MP_ tablas (MPtable)

- $ Mesas PIR

- Registra el espacio de configuración del dispositivo PCI 0x3C / 0x3D

Cabe señalar que el BIOS no necesita hacer nada adicional para indicar interrupciones al MSI; toda la información anterior es necesaria solo para las líneas de interrupción APIC / PIC.

Las tablas en la lista anterior se indican en orden de prioridad. Consideremos con más detalle.

Supongamos que el BIOS proporciona todos estos datos y arrancamos sin ninguna opción adicional:

- OS encuentra tablas ACPI

- El sistema operativo ejecuta el método ACPI "_PIC", le pasa el argumento de que necesita cargarse en modo APIC. Aquí el código del método generalmente guarda el modo seleccionado en una variable (digamos PICM = 1)

- Para obtener datos sobre las interrupciones, el sistema operativo llama al método ACPI "_PRT". Comprueba la variable PICM internamente y devuelve el enrutamiento para el caso APIC

En caso de que arranquemos con la opción

noapic :

- OS encuentra tablas ACPI

- El sistema operativo ejecuta el método ACPI "_PIC", le pasa el argumento de que es necesario arrancar en modo PIC. Aquí el código del método generalmente guarda el modo seleccionado en una variable (digamos PICM = 0)

- Para obtener datos sobre las interrupciones, el sistema operativo llama al método ACPI "_PRT". Comprueba la variable PICM internamente y devuelve el enrutamiento para el caso PIC

Si falta la tabla ACPI o la funcionalidad de enrutamiento de interrupciones a través de ACPI está deshabilitada usando las

opciones acpi = noirq o

pci = noacpi (o el ACPI está completamente apagado usando

acpi = off ), el sistema operativo busca la tabla MPtable (_MP_) para las interrupciones de enrutamiento:

- El sistema operativo no encuentra / no mira las tablas ACPI

- El SO encuentra MPtable (_MP_)

Si falta la tabla ACPI o la funcionalidad de enrutamiento de interrupción a través de ACPI está deshabilitada usando las

opciones acpi = noirq o

pci = noacpi (o el ACPI está completamente apagado usando

acpi = off ) y si falta la tabla MPtable (_MP_) (o se

pasa la opción de arranque

noapic o

nolapic ):

- El sistema operativo no encuentra / ve la tabla ACPI

- El sistema operativo no encuentra / no mira la tabla MPtable (_MP_)

- OS encuentra la tabla $ PIR

Si no hay una tabla $ PIR, o no está completa, entonces el sistema operativo para adivinar las interrupciones observará los valores de los registros 0x3C / 0x3D en el espacio de configuración de los dispositivos PCI.

Resumimos todo lo anterior con la siguiente imagen:

Debe recordarse que no todos los BIOS proporcionan las 3 tablas (ACPI / MPtable / $ PIR), por lo que si pasó la opción al cargador para negarse a usar ACPI o ACPI y MPtable para las interrupciones de enrutamiento, está lejos del hecho de que su sistema se iniciará.

Nota 1 : si intentamos arrancar en modo APIC con la opción acpi = noirq y sin MPtable, la imagen de las interrupciones será la misma que en el caso del arranque normal con la única opción noapic. El sistema operativo en sí entrará en modo de interrupción PIC.

Si intentamos arrancar sin tablas ACPI (acpi = off) y sin proporcionar MPtable, la imagen será así:

CPU0 0: 6 XT-PIC-XT-PIC timer 1: 2 XT-PIC-XT-PIC i8042 2: 0 XT-PIC-XT-PIC cascade 8: 0 XT-PIC-XT-PIC rtc0 12: 373 XT-PIC-XT-PIC ehci_hcd:usb1 16: 0 PCI-MSI-edge PCIe PME 17: 0 PCI-MSI-edge PCIe PME 18: 0 PCI-MSI-edge PCIe PME 19: 0 PCI-MSI-edge PCIe PME 20: 0 PCI-MSI-edge PCIe PME 21: 0 PCI-MSI-edge PCIe PME 22: 8728 PCI-MSI-edge ahci 23: 1 PCI-MSI-edge eth59 24: 1301 PCI-MSI-edge eth59-rx-0 25: 113 PCI-MSI-edge eth59-tx-0 26: 0 PCI-MSI-edge eth58 27: 45 PCI-MSI-edge eth58-rx-0 28: 45 PCI-MSI-edge eth58-tx-0 29: 1280 PCI-MSI-edge snd_hda_intel NMI: 2 Non-maskable interrupts LOC: 24076 Local timer interrupts SPU: 0 Spurious interrupts PMI: 2 Performance monitoring interrupts IWI: 2856 IRQ work interrupts RTR: 0 APIC ICR read retries RES: 0 Rescheduling interrupts CAL: 0 Function call interrupts TLB: 0 TLB shootdowns TRM: 34 Thermal event interrupts THR: 0 Threshold APIC interrupts MCE: 0 Machine check exceptions MCP: 2 Machine check polls ERR: 0 MIS: 0

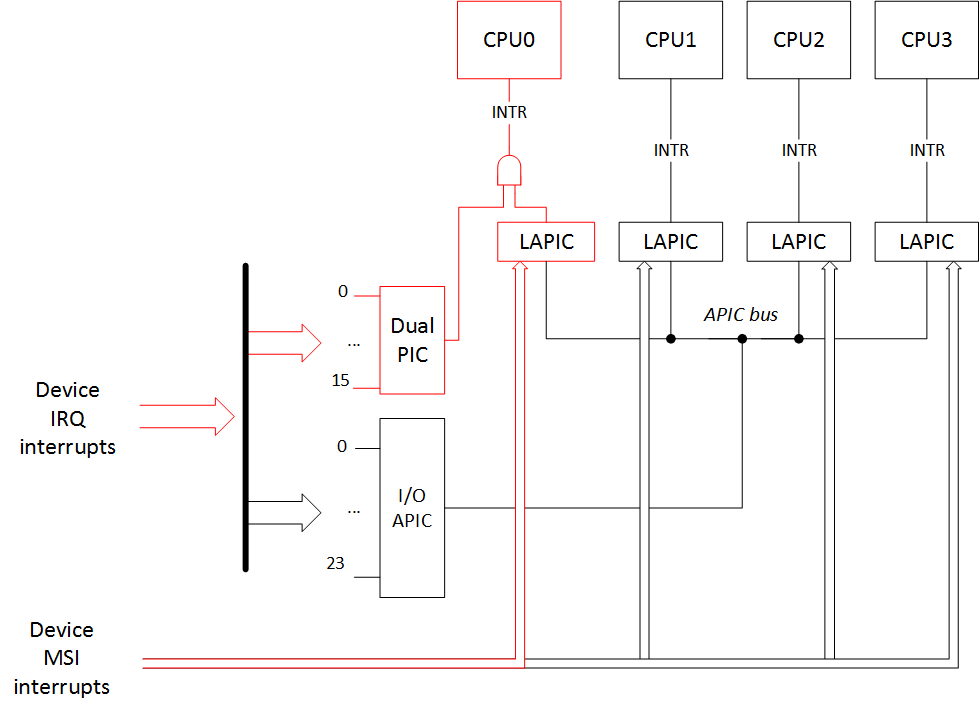

Esto sucede porque sin el ACPI de la tabla MADT (

Tabla de descripción APIC múltiple ) y la información necesaria de MPtable, el sistema operativo no conoce los identificadores APIC (ID APIC) para otros procesadores y no puede trabajar con ellos, pero el LAPIC del procesador principal funciona. ya que no prohibimos esto, y las interrupciones de MSI pueden llegar a eso. Es decir, será así:

Nota 2

Nota 2 : en general, el enrutamiento de interrupción cuando se usa ACPI en el caso de APIC es lo mismo que el enrutamiento de interrupción a través de MPtable. Y el enrutamiento de interrupción de ACPI en el caso de PIC es lo mismo que el enrutamiento de interrupción a través de $ PIR. Por lo tanto, las conclusiones de / proc / interrupts no deberían diferir. Sin embargo, en el proceso de investigación, noté una extraña. Al enrutar a través de MPtable, por alguna razón, la salida contiene una interrupción en cascada "cascada XT-PIC-XT-PIC".

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 2 0 0 0 IO-APIC-edge i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 8: 0 1 0 0 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-edge acpi ...

Es un poco extraño que esto suceda, pero la

documentación del

kernel parece decir que esto es normal.

Conclusión

En conclusión, denotamos una vez más las opciones analizadas.

Opciones de selección del controlador de interrupción:

- pci = nomsi : las interrupciones de MSI se convertirán en IO-APIC / XT-PIC dependiendo del controlador de interrupción utilizado

- noapic : deshabilita I / O APIC. Las interrupciones de MSI aún pueden ir a todas las CPU, otras interrupciones de dispositivos solo pueden ir a PIC, y solo funciona con CPU0. Pero LAPIC funciona y otras CPU pueden funcionar y manejar interrupciones

- noapic pci = nomsi : todas las interrupciones de los dispositivos solo pueden ir al PIC, y solo funciona con CPU0. Pero LAPIC funciona y otras CPU pueden funcionar y manejar interrupciones

- nolapic : deshabilita LAPIC. Las interrupciones de MSI no pueden funcionar sin LAPIC, I / O APIC no puede funcionar sin LAPIC. Todas las interrupciones de los dispositivos irán al PIC, y solo funciona con CPU0. Y sin LAPIC, el resto de la CPU no funcionará.

Opciones para elegir la tabla de prioridad para el enrutamiento de interrupción:

- sin opciones : enrutamiento a través de APIC utilizando tablas ACPI

- noapic - enrutamiento a través de PIC usando tablas ACPI

- acpi = noirq ( pci = noacpi / acpi = off ) - enrutamiento a través de APIC usando MPtable

- acpi = noirq ( pci = noacpi / acpi = off ) noapic ( nolapic ) - enrutamiento a través de PIC utilizando la tabla $ PIR

En la siguiente parte, veremos cómo coreboot configura el conjunto de chips para las interrupciones de enrutamiento.