En los comentarios a mi

artículo sobre el control de LED RGB utilizando el bloque de microcontrolador UDB de Cypress PSoC, se sugirió que sería bueno decir brevemente al comienzo del artículo qué es UDB. Como ya señalé en el artículo, no puedo escribir sobre UDB brevemente, pero simplemente puede transferirle la documentación de la compañía para familiarizar al lector doméstico con una herramienta tan poderosa para implementar funciones de firmware.

Pero primero, veamos de qué se trata PSoC. PSoC es una familia de chipsets de Cypress para implementar sistemas en chip. Las diferentes familias tienen un núcleo de procesador diferente (para PSoC 3 es MCS-51, para PSoC 4 es Cortex M0, para PSoC 5LP es Cortex M3 y para PSoC 6 son dos a la vez: Cortex M0 + y Cortex M4) y un conjunto de lógica programable. Además, esta lógica no es puramente digital; hay cosas analógicas allí. Además de un conjunto de ADC diferentes, también hay conmutadores analógicos. Incluso puede conectar programáticamente las patas a través de circuitos analógicos, sin embargo, la resistencia del circuito se medirá en kilogramos. Hay amplificadores operacionales dentro de PSoC que se pueden cambiar mediante programación, lo que significa que puede construir diferentes bloques analógicos en ellos.

Por cierto, los PSoC pueden ser alimentados por cualquier voltaje de 2.7 a 5.5 voltios. Es decir, no necesita pensar en ningún tipo de estabilizadores con batería o con USB.

Pero escribí sobre cosas analógicas simplemente por una palabra roja. Ahora nos centraremos en las cosas digitales. La mayoría de los controladores modernos tienen potentes unidades periféricas que proporcionan una gran variedad de funciones. Pero en la práctica, en cada desarrollo de software específico, estos bloques no se usan completamente, sino solo parcialmente. Y en PSoC, en lugar de muchos buenos, se implementa la lógica del programa, similar a la lógica de los FPGA clásicos. En consecuencia, es posible implementar exactamente aquellos bloques que se necesitan en él, incluyéndolos en los modos que se requieren. Y los recursos no deben gastarse en modos no utilizados, regalándolos para la implementación de algún tipo de cosas propias.

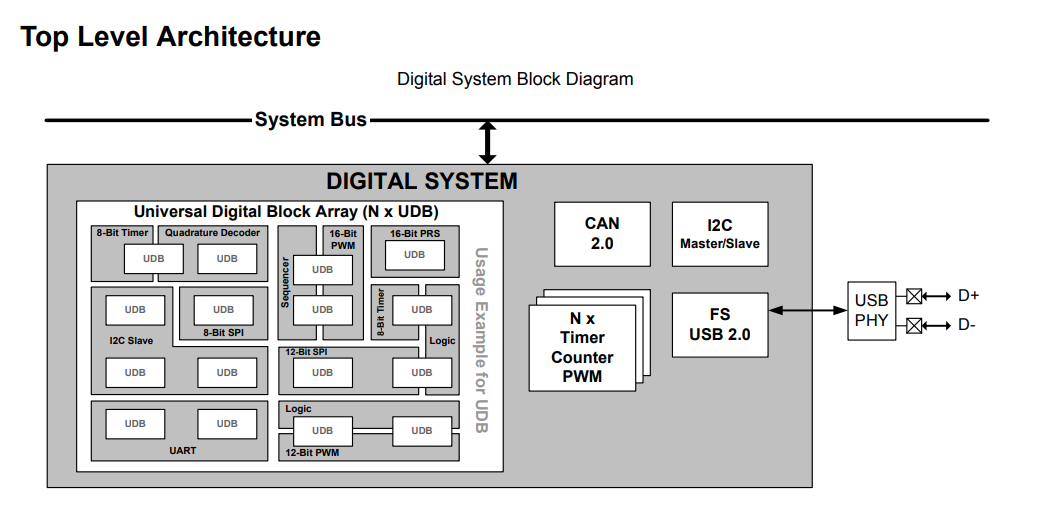

Y aquí a menudo surge algún malentendido. Muchos desarrolladores están acostumbrados al hecho de que hay dos tipos de circuitos integrados lógicos programables (FPGA): CPLD y FPGA. Por lo tanto, muchos de los que han escuchado acerca de PSoC creen que existe una especie de caja CPLD que se puede programar en Veriolg. De hecho, sí y no. Un cierto número de PLD (sin "C", solo PLD) realmente están allí, y realmente puede programarlos en Verilog. Pero realmente, estos PLD son parte de los bloques UDB. Y es UDB el elemento principal de la lógica programable implementada en PSoC. Este bloque es extremadamente original y ofrece simplemente las oportunidades más amplias para el desarrollador. Considere la figura de la documentación patentada que explica la esencia del uso de bloques UDB.

Como estudié todo utilizando la familia PSoC 5LP como ejemplo, traduciré la documentación a la misma. Pero antes de comenzar, diré algunas palabras sobre el precio de estos controladores. Si vas a Ali Express y miras la tabla para ellos, tienes una sensación triste. Hablando francamente, en comparación con STM32-DISCOVERY todavía no son nada, pero en comparación con los prototipos STM32F103C8T6, son un poco caros. En primer lugar, esto se debe al hecho de que las maquetas corporativas siempre tienen no uno, sino dos controladores de este tipo. Las funciones JTAG se implementan en el PSoC 5LP, incluso si el controlador de destino y el PSoC 4 (este último generalmente no tiene un puerto USB).

Pero al dividir el precio por dos, aún obtenemos que es más alto que el del STM32F103, que es similar en el núcleo del procesador. Sin embargo, si agregamos incluso el CPLD más simple al mismo STM32 desde el exterior, entonces el precio total saldrá a favor de PSoC. Y agregaremos las patas perdidas a la conexión de estos dos casos (PSoC tiene todas las conexiones dentro). Y también el precio de centímetros cuadrados del tablero. Resulta que si necesita trabajar solo con el núcleo del procesador, PSoC realmente no es necesario. Si necesita aportar alguna funcionalidad al nivel de firmware o hardware, entonces necesita PSoC. En él, el sistema saldrá más barato y más fácil.

De hecho, tengo una idea maníaca para tratar de hacer soporte de hardware para el núcleo de nuestro RTOS MAX. Para hacer esto, estudié la metodología para desarrollar aplicaciones de Bare Metal para Altera V SoC (por desgracia, resultó que la característica de la arquitectura es tal que el sistema operativo puede ralentizarse, pero no puede acelerarlo: las solicitudes individuales al hardware vienen con una latencia loca). Para esto, comencé a dominar PSoC. No he alcanzado el overclocking del kernel (solo hay pensamientos generales), pero realmente me gustó la idea de la programación UDB. Por supuesto, ahora estoy interesado en llevar esta idea al máximo número de programadores nacionales. Por lo tanto, procedemos a la traducción de la parte correspondiente de la documentación propietaria de Cypress en UDB. La numeración de capítulos y figuras se mantiene de acuerdo con el documento original.

El contenido general del ciclo “UDB. ¿Qué es esto?

Parte 1. Introducción. Pld. (Artículo actual)

Parte 2. Ruta de datos.Parte 3. Datapath FIFO.Parte 4. Datapath ALU.Parte 5. Ruta de datos. Pequeñas cosas útiles.Parte 6. Módulo de gestión y estado.Parte 7. Módulo de control de temporización y reinicioParte 8. Abordar UDBUDB Que es esto Parte 1

21. bloques digitales universales

En este capítulo, veremos cómo los bloques digitales universales (UDB) permiten el desarrollo de funciones periféricas digitales programables. La arquitectura UDB logra un equilibrio entre granularidad de configuración e implementación eficiente. Los UDB consisten en una combinación de lógica no conmutada similar a una matriz lógica programable (PLM, PLD en inglés), lógica estructurada (máquinas operativas, en lo sucesivo denominadas Datapath) y un esquema de rastreo flexible.

21.1 Características

- Para una flexibilidad óptima, cada UDB contiene los siguientes componentes:

• Ruta de datos de 8 bits basada en ALU (Unidad aritmética y lógica, ALU) con repositorio de instrucciones de 8 palabras, varios registros y memorias intermedias FIFO;

• dos PLD, cada uno de los cuales tiene 12 entradas, ocho términos conjuntivos (Términos del producto, PT) y cuatro salidas de macroceldas;

• registros de gestión y estado;

• reloj y módulos de reinicio. - PSoC 5LP contiene una matriz de hasta 24 UDB de tamaño.

- Seguimiento flexible entre elementos de matriz UDB.

- Los elementos UDB se pueden dividir o encadenar para crear funciones más grandes.

- Implementación flexible de una serie de funciones digitales, incluidos temporizadores, contadores, moduladores de ancho de pulso (incluido PWM con un generador de banda muerta), UART, bus I2C, bus SPI y verificación / generación de CRC.

21.2 Diagrama de bloques

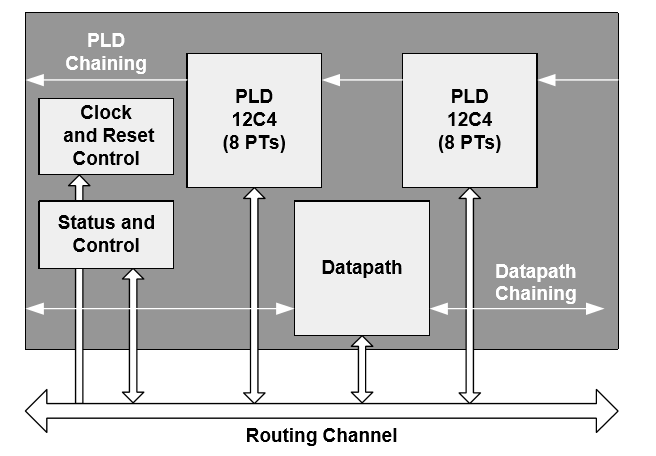

La Figura 21-1 muestra la UDB como una construcción que contiene dos bloques lógicos básicos, PLD, Datapath y las funciones de control, estado, reloj y reinicio.

Figura 21-1. Diagrama de bloques de UDB.

Figura 21-1. Diagrama de bloques de UDB.21.3 Cómo funciona

Los componentes principales de UDB son:

- PLD (2). Los datos de los recursos de rastreo se envían a las entradas de estos bloques. Implementan lógica combinacional y ajuste de datos, lo que le permite implementar máquinas de estados finitos, controlar las operaciones del bloque Datapath, configurar las condiciones de entrada y controlar las salidas.

- Datapath. Este bloque contiene ALU programables dinámicamente, cuatro registros, dos memorias intermedias FIFO, comparadores y generación de condiciones.

- Gestión y estado (Estado y Control). Estos módulos proporcionan un mecanismo para la interacción de los microprogramas del procesador central (CPU) y la sincronización con las operaciones UDB. Los registros de control actúan sobre elementos internos, y los registros de estado leen el estado de los elementos externos.

- Reloj y control de reinicio Estos módulos proporcionan selección y habilitación de temporización, así como restablecer selección dentro de UDB.

- Encadenamiento de señales. PLD y Datapath tienen señales que le permiten encadenar bloques adyacentes en una cadena para crear funciones de bits más altos.

- Canal de rastreo Los UDB se conectan al canal de rastreo a través de matrices de conmutación programables para la comunicación entre bloques dentro del mismo UDB y para la comunicación con otros UDB en la matriz.

- Interfaz del bus del sistema (interfaz del bus del sistema). Todos los registros y RAM en cada UDB se proyectan en el espacio de direcciones del sistema, y se puede acceder a ellos utilizando el procesador central o mediante el acceso directo a la memoria (Acceso directo a la memoria en inglés, DMA) en forma de 8 bits y 16 bits. datos

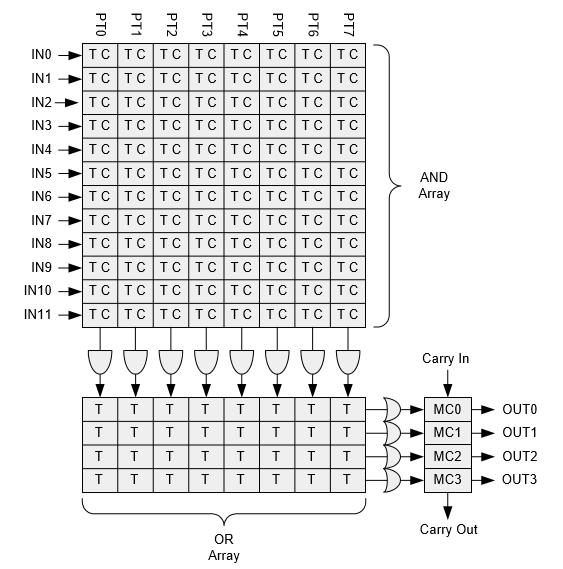

21.3.1. Pld

Cada UDB tiene dos PLD 12C4. Los bloques PLD que se muestran en la Figura 21-1 se pueden usar para implementar máquinas de estado, procesar datos de E / S y crear una lógica de tabla (Tabla de búsqueda de ing. Además, PLD se puede configurar para realizar funciones aritméticas, establecer la secuencia de Datapath y generar estado. La lógica general se puede sintetizar y proyectar en bloques PLD. Esta sección proporciona una descripción general de la arquitectura PLD.

PLD tiene 12 entradas que transmiten información en 8 términos conjuntivos en una matriz AND. En cada término conjuntivo, puede elegir una entrada directa (verdadera, T) o inversa (complemento, C). La salida de los términos conjuntivos va a la entrada de la matriz OR. La letra 'C' en 12C4 indica que los términos OR son constantes para todas las entradas, y cada entrada OR puede obtener acceso programático a cualquier término conjuntivo. Esta estructura proporciona la máxima flexibilidad y garantiza que todas las entradas y salidas se puedan mover.

Figura 21-2. La estructura de PLD 12C4.

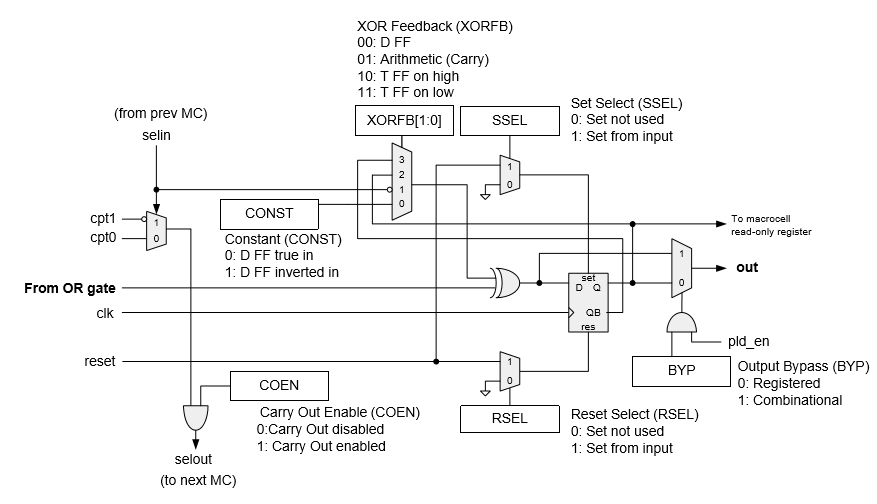

Figura 21-2. La estructura de PLD 12C4.21.3.1.1 Macro PLD

La arquitectura de las macrocélulas se muestra en la figura 21-3. La salida controla la matriz de rastreo y puede enclavarse o Raman. Para el enclavamiento, se utiliza un disparador D con entrada directa o inversa o un disparador T con un nivel de entrada alto o bajo. El disparador de salida se puede configurar o restablecer durante la inicialización o de forma asíncrona durante el funcionamiento normal, mediante una señal externa del canal de rastreo.

Figura 21-3. Arquitectura de macrocélulas.Registro de celda macro de PLD de solo lectura

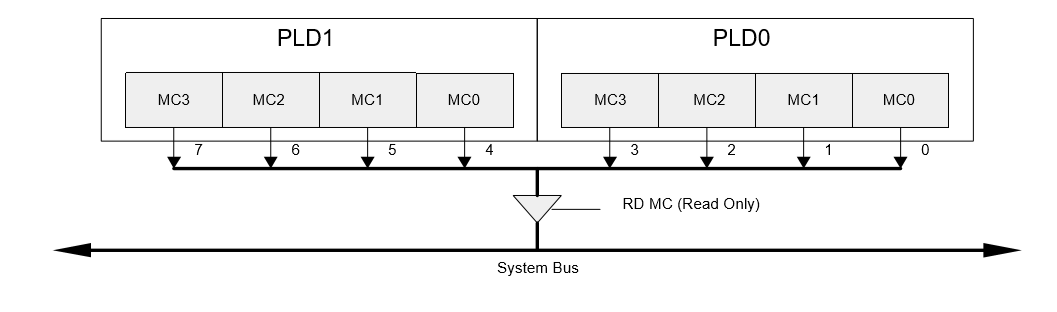

Figura 21-3. Arquitectura de macrocélulas.Registro de celda macro de PLD de solo lecturaAdemás de controlar la matriz de rastreo, las salidas de macroceldas de ambos PLD se proyectan en el espacio de direcciones en forma de un registro de solo lectura de 8 bits, al que se puede acceder utilizando la CPU o DMA.

Figura 21-4. El registro de macroceldas PLD de solo lectura.

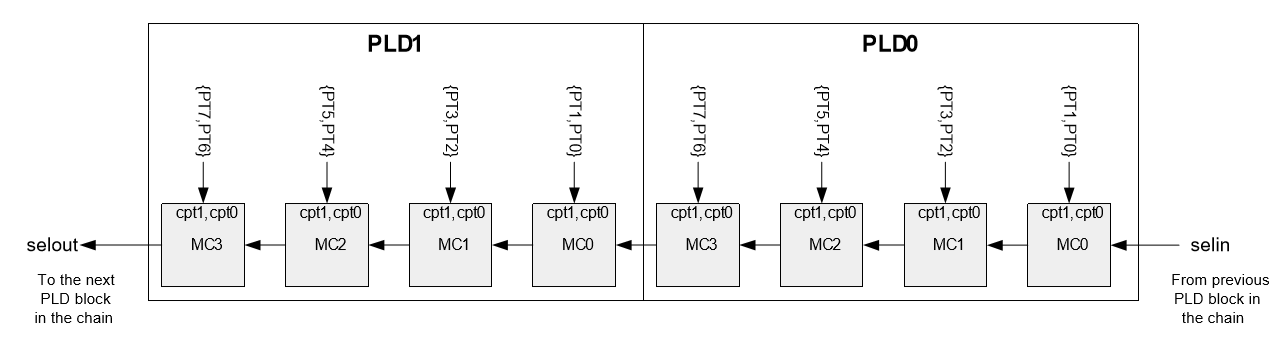

Figura 21-4. El registro de macroceldas PLD de solo lectura.21.3.1.2 cadena de separación de palabras PLD

Los PLD están unidos en el direccionamiento UDB. Como se muestra en la Figura 21-5, la entrada de la cadena de transporte de selin se reenvía desde el UDB anterior al circuito, a través de cada macrocélula en ambos PLD, luego se reenvía al siguiente UDB como la salida de la cadena de transporte de selout. Para apoyar la colocación eficiente de las funciones aritméticas, se generan términos conjuntivos especiales (PT), que se utilizan en macrocélulas junto con una cadena de separación silábica.

Figura 21-5. Cadena de separación silábica PLD y entradas de términos conjuntivos especiales.

Figura 21-5. Cadena de separación silábica PLD y entradas de términos conjuntivos especiales.21.3.1.3 Configuración PLD

Cada PLD aparece antes de la CPU o DMA en forma de RAM con acceso de 16 bits. La matriz AND tiene 12 × 8 × 2 bits o 24 bytes para la programación, y la matriz OR tiene 4 × 8 bits o 4 bytes para la programación. Además, cada macrocelda tiene un byte de configuración, totalizando 32 bytes de configuración por PLD. Como cada UDB tiene 2 PLD, la configuración total de cada UDB es de 64 bytes.

La próxima vez consideraremos los autómatas operativos (rutas de datos).