Continuamos traduciendo la documentación patentada de Cypress a bloques UDB. Además, todo coincide muy bien. Para continuar el

artículo práctico sobre UDB, necesitará usar FIFO, y en la parte teórica llegamos a la descripción de ellos. Por lo tanto, comenzamos a estudiarlos en detalle.

El contenido general del ciclo “UDB. ¿Qué es esto?

Parte 1. Introducción. Pld.Parte 2. Ruta de datos.Parte 3. Datapath FIFO. (Artículo actual)

Parte 4. Datapath ALU.Parte 5. Ruta de datos. Pequeñas cosas útiles.Parte 6. Módulo de gestión y estado.Parte 7. Módulo de control de temporización y reinicioParte 8. Abordar UDB21.3.2.2 Ruta de datos FIFO

Modos y configuraciones FIFO

Cada búfer FIFO tiene varios modos operativos y configuraciones disponibles:

Tabla 21-2. Modos y configuraciones FIFO.

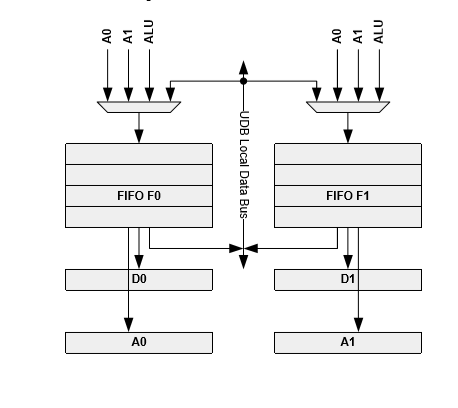

La Figura 21-7 muestra las posibles opciones de configuración para el par FIFO, dependiendo de los modos de Entrada / Salida seleccionados para cada uno de ellos. Si un FIFO está en el modo de entrada y el otro en el modo de salida, obtenemos la configuración RX / TX. Un ejemplo típico donde se necesita dicha configuración es el controlador de bus SPI. La configuración de

captura dual (ambos FIFO están configurados para la salida) proporciona una captura independiente del par A0 y A1 o dos capturas independientes de los registros A0 o A1. Finalmente, en el modo

Dual Buffer (ambos en la entrada), es posible usar un par de registros o dos registros independientes para cargar o comparar.

Figura 21-7. Configuraciones FIFO.

La figura 21-8 muestra en detalle las fuentes y los receptores para FIFO.

Figura 21-8. Fuentes FIFO y receptores.

Cuando FIFO funciona en el modo de búfer de entrada, la fuente es el bus del sistema y los receptores son los registros Dx y Ax. Cuando se trabaja en el modo de búfer de salida, las fuentes son los registros Ax y ALU, y el receptor es el bus del sistema. La selección del multiplexor se establece estáticamente en el registro de configuración UDB CFG15, como se muestra en la tabla para F0_INSEL [1: 0] o F1_INSEL [1: 0]:

Tabla 21-3. Un conjunto de multiplexores FIFO en el registro de configuración UDB.

Estado FIFO

Cada FIFO genera dos señales de estado, "bus" y "bloque", que se transmiten a los recursos de rastreo UDB a través del multiplexor de salida Datapath. El estado del bus se puede usar para interrumpir o solicitar una lectura / escritura de DMA al FIFO. El estado de "bloque" está destinado principalmente a pasar el estado FIFO a entidades UDB internas. El propósito de los bits de estado depende de la dirección configurada (Fx_INSEL [1: 0]) y de los bits de nivel FIFO. Los bits de nivel FIFO (Fx_LVL) se establecen en el registro de control auxiliar en el espacio de registro de trabajo. Las opciones de estado se muestran en la siguiente tabla:

Tabla 21-4. Opciones de estado FIFO.

Ilustración de trabajo FIFO

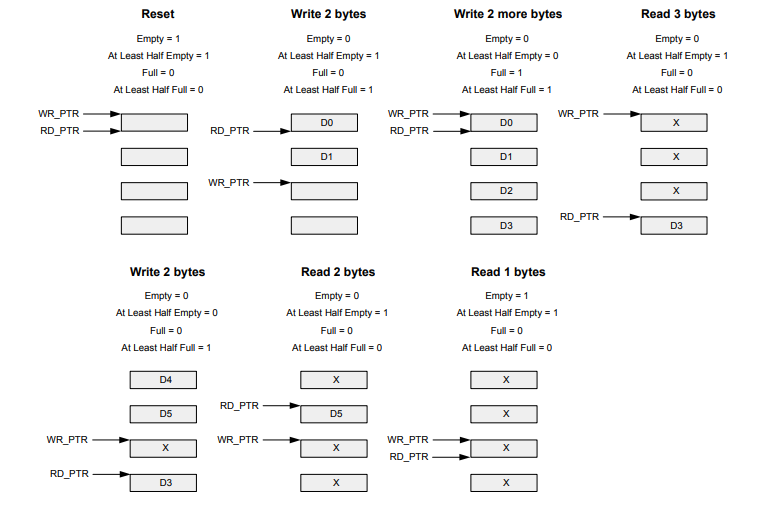

La figura 21-9 muestra una secuencia típica de lectura y escritura, así como la generación de estados asociados con estas operaciones. En la figura, la lectura y la escritura ocurren en diferentes momentos, pero pueden realizarse simultáneamente.

Figura 21-9 Funcionamiento de los receptores FIFO.

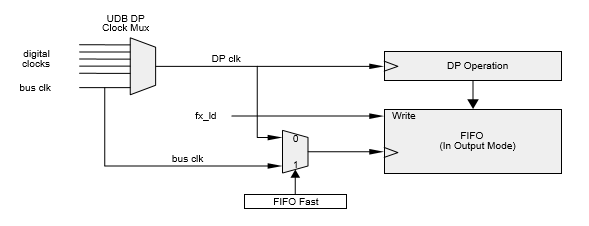

Modo rápido FIFO (FIFO FAST)

Cuando FIFO está en modo de búfer de salida, la operación de arranque FIFO generalmente usa la frecuencia de reloj del Datapath seleccionado para registrar la señal de escritura. Como se muestra en la Figura 21-10, al seleccionar el modo rápido FIFO (FIFO FAST), puede seleccionar la frecuencia del bus para esta operación en particular. Cuando se usa junto con el modo

Nivel / Borde = Borde , esta operación reduce el retraso de transmisión de la batería al FIFO desde el período del reloj Datapath al período del reloj del bus, ya que la frecuencia del bus puede ser mucho mayor. Esto permite que la CPU o el DMA lean el resultado FIFO recibido con un retraso mínimo.

Como se muestra en la Figura 21-10, la operación de arranque rápido se realiza independientemente del reloj Datapath actual, sin embargo, el uso de la velocidad del reloj del bus puede aumentar el consumo de energía.

Figura 21-10. FIFO receptores de configuración rápida.

Modo de grabación FIFO Edge / Level (diferencial / nivel)

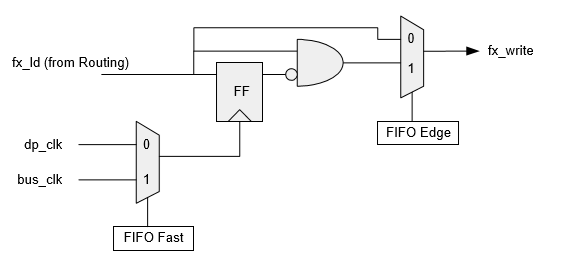

Hay dos modos de grabación en FIFO desde Datapath. En el primer modo, los datos se transfieren sincrónicamente desde las baterías al FIFO. La señal de control de este registro (FX_LD) generalmente es generada por una máquina de estado o por una condición sincronizada con el reloj Datapath. La escritura en FIFO se realizará en cualquier ciclo en el que la señal de control de carga de entrada sea '1'. En el segundo modo, FIFO se utiliza para capturar los valores de la batería en respuesta a un borde positivo de la señal FX_LD. En este modo, el formato de la señal de la señal es arbitrario (sin embargo, su período debe ser igual a al menos un ciclo de reloj Datapath). Un ejemplo de este modo es capturar el valor de la batería utilizando la entrada del pie externo como disparador. Una limitación de este modo es que el parámetro de entrada debe volver al valor '0' al menos un ciclo antes de que se detecte otra diferencia positiva.

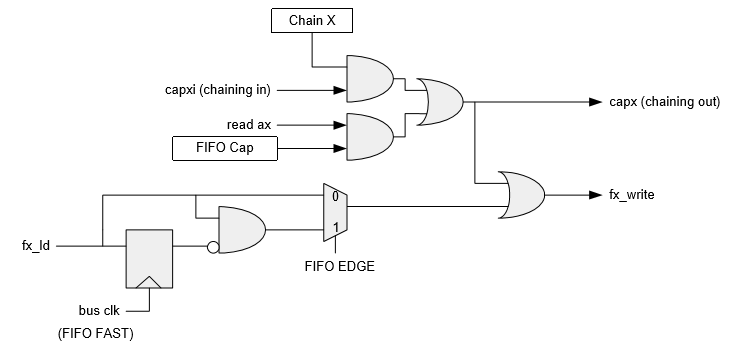

La figura 21-11 muestra la implementación del modo de detección diferencial en la entrada FX_LD. El modo de ambos FIFO en UDB está controlado por el mismo bit, alternando esta opción. Tenga en cuenta que la detección diferencial se sincroniza a una frecuencia igual a la frecuencia del FIFO seleccionado.

Figura 21-11. Detección diferencial para receptores de grabación FIFO internos.

Modo de captura de software FIFO

Un requisito común e importante es permitir que la CPU y el DMA lean de manera confiable el contenido de la batería durante el funcionamiento normal. Esto se realiza mediante la captura de software y se habilita mediante el bit de configuración FIFO Cap. Este bit se aplica a ambos FIFO en UDB, pero solo funciona cuando el FIFO está en modo de búfer de salida. Cuando se utiliza la captura de software, F0 debe leer de A0 y F1 de A1.

Como se muestra en la Figura 21-12, la lectura de la batería inicia la escritura en el FIFO desde la batería. La señal está vinculada en una cadena para que al leer un byte específico al mismo tiempo capture los valores de batería de todos los UDB en la cadena. Esto permite que el procesador de 8 bits lea con éxito 16 bits o más al mismo tiempo. Los datos devueltos al leer la batería deben ignorarse, y el valor capturado puede leerse inmediatamente desde FIFO.

La señal rastreada FX_LD, que genera la carga FIFO, se envía al término OR junto con la señal de captura del programa. Cuando se utiliza la captura de hardware y software al mismo tiempo, el resultado puede ser impredecible. Como regla general, estas funciones deben ser mutuamente excluyentes, sin embargo, la captura de hardware y software puede usarse simultáneamente bajo las siguientes condiciones:

- El modo de reloj de captura FIFO está configurado en FIFO FAST.

- El modo de grabación FIFO está configurado en FIFO EDGE.

En las condiciones descritas anteriormente, la captura de hardware y software funciona esencialmente de la misma manera, y durante cualquier ciclo de reloj del bus, cualquiera de estas señales puede desencadenar una captura.

También se recomienda que borre el FIFO de destino en el código del programa (registro ACTL) antes de que comience la captura del programa. Gracias a esto, los punteros de lectura y escritura FIFO se establecerán en un estado conocido.

Figura 21-12. Configuración de captura de software.

Nota del traductor:

Durante mucho tiempo no pude entender el significado de esta sección. Luego, durante mucho tiempo, estuve seguro de que la sección fue escrita para PSoC3, cuyo núcleo de ocho bits no puede acceder más que un byte. Pero al crear la octava parte de la traducción , resultó que incluso en PSoC5LP, para todos los núcleos de procesador ARM de 32 bits, el acceso a los registros UDB en funcionamiento se puede llevar a cabo en modo de ocho o dieciséis bits. A juzgar por el documento, no más. Aquí es donde la funcionalidad descrita resulta útil.

Bits de control FIFO

El registro de control auxiliar, que puede usarse para controlar FIFO durante el funcionamiento normal, contiene 4 bits.

Los bits FIFO0 CLR y FIFO1 CLR se utilizan para restablecer o borrar FIFOs. Cuando a uno de estos bits se le asigna el valor '1', el FIFO asociado se restablece. El bit debe restaurarse a su valor original ('0') para que FIFO continúe funcionando. Si el valor del bit permanece igual a uno, el FIFO correspondiente se desactivará y funcionará como un búfer de un solo byte sin estado. Los datos se pueden escribir en FIFO, los datos se pueden leer de inmediato y se pueden sobrescribir en cualquier momento. La dirección de datos con los bits de configuración FX INSEL [1: 0] aún se puede establecer.

Los bits FIFO0 LVL y FIFO1 LVL determinan el nivel en el que FIFO activará el bit de estado

"bus" (cuando el bus lee o escribe en FIFO). Es decir, el estado del

"bus" depende de la dirección dada, como se muestra en la tabla a continuación.

Tabla 21-5. Bits de control de nivel FIFO

Operación asincrónica FIFO

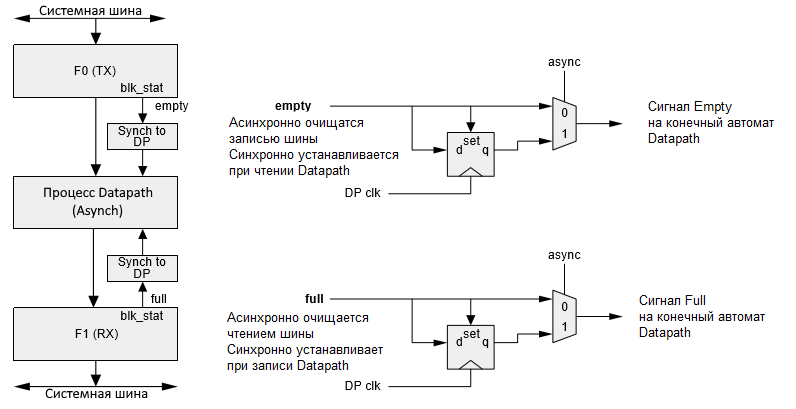

La figura 21-13 muestra el principio del funcionamiento asincrónico de FIFO. Como ejemplo, imagine que F0 opera en el modo de búfer de entrada y F1 en el modo de búfer de salida, que es una configuración típica de los registros TX y RX.

Figura 21-13. Operación asincrónica FIFO.

En el lado de TX, la máquina de estado de Datapath utiliza el indicador

Vacío para determinar si hay bytes disponibles para recibir. El valor de

Vacío se establece sincrónicamente con la máquina de estado Datapath, y se borra de forma asincrónica debido a la escritura desde el bus. Después de la limpieza, el estado se sincroniza nuevamente con la máquina de estado Datapath.

En el lado RX, la máquina de estado RX usa

Full para determinar si hay espacio libre para escribir en el FIFO. El valor

Completo se establece de forma sincrónica con la máquina de estado Datapath, y se borra de forma asincrónica debido a la lectura del bus. Después de la limpieza, el estado se sincroniza nuevamente con la máquina de estado Datapath.

Se utiliza un bit FIFO ASYNCH para habilitar este método de sincronización, después de la activación, este método se aplica a ambos FIFO.

Se aplica solo al estado de

Bloque , ya que se supone que el estado de

Bus está naturalmente sincronizado por el proceso de interrupción.

Cuadro 21-6.

Bloquee las opciones de sincronización de estado FIFO.

FIFO desbordamiento durante la operación

Para la implementación segura de operaciones de lectura y escritura internas (Datapath) y externas (CPU o DMA), se deben usar señales de estado FIFO. No hay protección incorporada contra condiciones de vaciado y desbordamiento. Si la FIFO está llena y se realizan operaciones de escritura posteriores (desbordamiento), los nuevos datos sobrescriben el comienzo de la FIFO (los datos que se emiten actualmente son los siguientes en la cola de lectura). Si el FIFO está vacío y se realizan lecturas posteriores (vaciado o agotamiento), el valor de lectura no está definido. Los punteros FIFO siguen siendo precisos independientemente del subdesbordamiento y desbordamiento.

Inversión de reloj FIFO

Cada FIFO tiene un bit de control Fx CK INV, que es responsable de la polaridad del reloj FIFO con respecto a la polaridad del reloj Datapath. Por defecto, FIFO funciona con la misma polaridad que el reloj Datapath. Cuando este bit es 1, FIFO funciona con polaridad inversa en relación con Datapath. Esto proporciona soporte de protocolo para intercambiar datos en ambos frentes, como SPI.

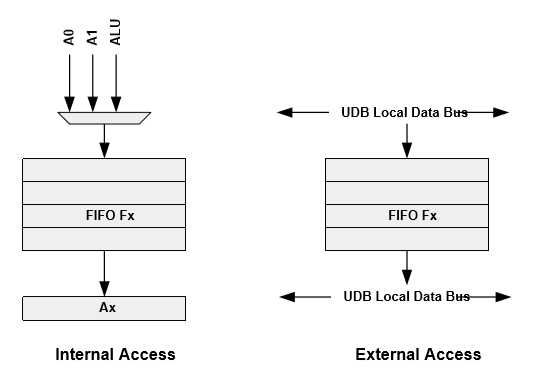

Control dinámico FIFO

Normalmente, los FIFO se configuran estáticamente en el modo de búfer de entrada o en el modo de búfer de salida. Alternativamente, cada FIFO puede configurarse para operar en un modo en el que la dirección se controla dinámicamente (bajo la influencia de señales externas). Un bit de configuración por FIFO (Fx DYN) es responsable de activar este modo. La Figura 21-14 muestra las configuraciones disponibles en el modo dinámico FIFO.

Figura 21-14. Modo dinámico FIFO.

En el modo de acceso interno, Datapath puede leer y escribir en FIFO. En esta configuración, para seleccionar la fuente de operaciones de escritura en FIFO, los bits Fx INSEL deben establecerse en 1. Fx INSEL = 0 (fuente del bus de CPU) en este modo es incorrecto, solo puede tomar los valores 1, 2 o 3 (A0, A1 o ALU ) Vale la pena señalar que la lectura solo tiene acceso a la batería adecuada, la dirección de los registros de datos en este modo no está disponible.

En el modo de acceso externo, la CPU o el DMA pueden leer o escribir en FIFO.

La configuración cambia dinámicamente entre acceso externo e interno mediante el reenvío de señales de Datapath. Para esto, se utilizan las señales de entrada Datapath d0_load y d1_load. Vale la pena señalar que en el modo de control dinámico, d0_load y d1_load no están disponibles para su uso normal al cargar registros D0 / D1 desde F0 / F1. Las señales Dx_load pueden ser activadas por cualquier señal de rastreo, incluidas las constantes.

Considere un ejemplo en el que, comenzando con el acceso externo (dx_load == 1), la CPU o el DMA pueden escribir uno o más bytes de datos en la FIFO. Luego, al cambiar al acceso interno (dx_load == 0), Datapath puede realizar operaciones en los datos. Después de eso, al cambiar a acceso externo, la CPU o DMA puede leer el resultado de los cálculos.

Como Fx INSEL siempre debe ser 01, 10 u 11 (A0, A1 o ALU), que corresponde al "modo de búfer de salida" durante el funcionamiento normal, las señales de estado FIFO tienen las siguientes definiciones (según el parámetro Fx LVL):

Cuadro 21-7. Estado FIFO.

Dado que tanto Datapath como la CPU pueden escribir y leer desde FIFO, estas señales ya no se consideran estados de bloque y bus. La señal blk_stat se usa para el estado de escritura y la señal bus_stat para el estado de lectura

21.3.2.3 Estado FIFO

Hay cuatro señales de estado FIFO, dos para cada FIFO: fifo0_bus_stat, fifo0_blk_stat, fifo1_bus_stat y fifo1_blk_stat. El significado de estas señales depende de la dirección de la FIFO particular, que está determinada por la configuración estática. El estado FIFO se describe en detalle en la sección 21.3.2.2 Datapath FIFO .En la siguiente parte, pasaremos al análisis de la Unidad de lógica aritmética (ALU).