El tamaño de las características del transistor está disminuyendo a pesar de los constantes rumores sobre la muerte de la ley de Moore y el hecho de que la industria está realmente cerca de los límites físicos de la miniaturización (o incluso los atravesó con algunos trucos tecnológicos inteligentes). Sin embargo, la ley de Moore creó el apetito de los usuarios por la innovación, que es difícil de manejar para la industria. Es por eso que los productos microelectrónicos modernos no son solo escalas de tamaño de características, sino que también emplean una serie de otras características, a menudo incluso más complicadas que la escala de chips.

Descargo de responsabilidad: este artículo es una traducción ligeramente actualizada de mi propia pieza publicada en este mismo sitio aquí . Si habla ruso, es posible que desee verificar el original. Si habla inglés, vale la pena señalar que el inglés no es mi lengua materna, por lo que le agradeceré sus comentarios si encuentra algo extraño en el texto. He dicho intencionalmente "producto microelectrónico" en lugar de solo "chip", porque este artículo trata sobre la tecnología System in Package (SiP) que permite conectar muchos chips dentro de un solo paquete.

El término Sistema en paquete es mucho menos popular que el término Sistema en chip (SoC), que es utilizado habitualmente por todas las compañías de semiconductores, y por una buena razón, ya que casi cualquier chip moderno es de alguna manera un sistema con muchas funciones fusionadas. Los tiempos de los abundantes conjuntos de chips han quedado atrás, ya que las ventajas de SoC son claras: menos paquetes en la PCB, menos área (leer "más barato"), menos capacitancias e inductancias parásitas (leer "más rápido"), más fáciles de implementar y usar, Es más económico diseñar y fabricar un solo chip complejo que un montón de chips más específicos.

Pero nada es gratis, y los SoC obviamente tienen algunas desventajas.

Primero, al intentar juntar todas las piezas, corre el riesgo de obtener un chip demasiado grande para caber en cualquier paquete o, lo que es peor, en la ventana del fotolitógrafo. La última restricción puede ser superada, pero casi siempre es excesivamente costosa (siendo las cámaras fotográficas la exclusión más notable).

Aquí está el sensor de imagen Kodak Kaf39000, tiene un área de 2000 milímetros cuadrados y utiliza costuras de máscara. El chip sin costura más grande es NVIDIA Volta de 815 milímetros cuadrados, que es solo 20 milímetros menos que el tamaño más grande posible.

En segundo lugar, cuanto más grande es el chip, menor es el rendimiento, ya que cualquier mota de polvo puede arruinar tu día. ¿Y adivina qué? Menor rendimiento significa mayor precio.

En tercer lugar, si su sistema contiene componentes heterogéneos, como el núcleo del procesador, la DRAM y el módulo de RF, combinarlos juntos puede ser tecnológicamente imposible o, una vez más, irrazonablemente costoso. Por ejemplo, las células DRAM requieren condensadores específicos de alta densidad, y los circuitos de RF basados en silicio pueden ser peores que sus equivalentes producidos en varios materiales A3B5 (GaAs y Me gusta). Incluso la combinación simple de procesamiento digital y acondicionamiento de señal analógica en el mismo chip crea problemas de ruido significativos. Y ni siquiera digo sobre el hecho de que el ADC de 180 nm sería fácilmente dos órdenes de magnitud más barato que agregar su análogo de 14 nm al chip MCU de 14 nm.

La combinación de todos los factores anteriores condujo al cambio de tendencia de “empacaremos todo en un solo chip” a un enfoque más pragmático y al rápido desarrollo de varias tecnologías de empaque.

Rendimiento y rendimiento

El primer ejemplo que viene a la mente es el reciente renacimiento de AMD, ampliamente reconocido como el resultado de su éxito con los sistemas de múltiples chips (también ayudado por los problemas de Intel con el rendimiento en enormes chips de 10 nm).

La imagen de arriba es el Xeon de 28 núcleos de Intel. El área de chips de estos procesadores puede alcanzar 456 milímetros cuadrados, mientras que el tamaño máximo de los chips AMD es de solo 200 milímetros cuadrados para ocho núcleos, sus productos de muchos núcleos son en realidad PCB de dos capas con hasta cuatro dados dentro del paquete.

Esta figura muestra la PCB dentro de los procesadores EPYC y Threadripper. En el caso de Threadripper de 16 núcleos, todavía tenemos cuatro chips, pero la mitad de los núcleos están desactivados. ¿Por qué no solo usar dos dados en su lugar? ¿O usar dados más pequeños de cuatro núcleos?

Primero, tener un solo chip para todos los propósitos es obviamente mucho más barato que diseñar una familia.

Segundo, lo mismo es cierto para PCB, paquetes, etc. Es más fácil desactivar partes excesivas que diseñar una familia de productos.

Tercero y probablemente el más importante, rendimiento de 200-sq.mm. morir aún está lejos del 100%, y deshabilitar algunos núcleos que ya no funcionan es una buena manera de usar estos dados defectuosos. Intel hace lo mismo con sus dados defectuosos, pero sus problemas de rendimiento son más graves debido al área de chip más grande.

Aquí tenemos un ejemplo aún más interesante, nuevamente de AMD. Fiji es una GPU con memoria integrada de alta velocidad colocada dentro del paquete. Porque las líneas de señal más cortas permiten lograr una mayor velocidad y, por lo tanto, un mayor rendimiento. Poner diferentes chips juntos hace la diferencia entre este y el ejemplo anterior. Por cierto, no hay cinco dados en el interior como uno podría haber sugerido, ¡sino veintidós! Veamos la sección transversal:

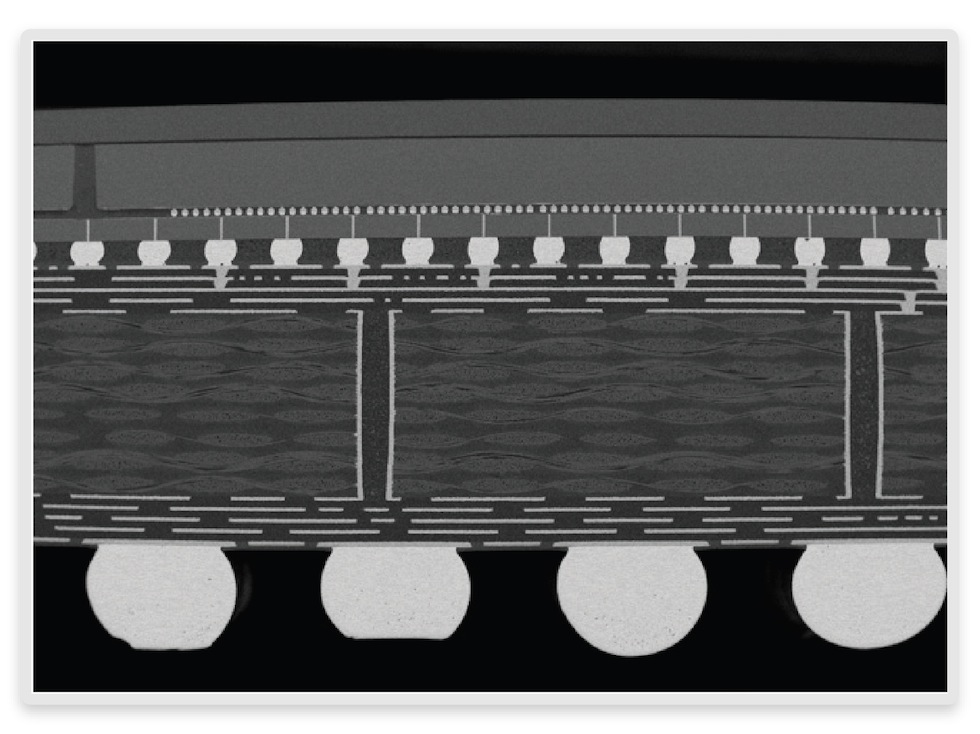

El nivel superior es la matriz de GPU y una pila de cuatro dados de memoria conectados por el llamado TSV (a través de vías de silicio) - contactos conductores que perforan todo el chip.

Así es como se ve TSV.

La tecnología TSV fue creada para la memoria (uno no puede tener demasiada memoria, ¿verdad?), Pero ahora está muy extendida, en parte gracias a la matriz colocada bajo GPU y memoria.

El troquel se llama Silicon Interposer y es un sustituto de PCB hecho de silicio con unos pocos (o muchos) niveles de metalización y con TSV. Estos intercaladores existen para conectar múltiples chips por encima de ellos con un sustrato del paquete. La tecnología de silicio permite tener un tamaño de característica más pequeño que cualquier PCB (hasta unas pocas micras), pero se consideraría muy simple y barato para una tecnología de silicio. Un tamaño de característica más pequeño y TSV significan un mejor rendimiento que cualquier PCB puede proporcionar, mientras que el rendimiento será muy alto. Los intercaladores (junto con MEMS) son un mercado muy interesante e importante, especialmente porque también permiten la reutilización de equipos viejos para obleas de 200, 150 e incluso 100 mm.

Por cierto, ¿puedes detectar un error en la figura de arriba?Xilinx es otro pionero de la integración 3D. Sus productos están cerca de los de AMD (especialmente los productos que llevan cantidades significativas de memoria), y por la misma razón. FPGA es un mercado donde el cambio temprano a un nodo de proceso más pequeño puede proporcionar una enorme ventaja sobre la competencia. Se dice que la disminución del tamaño del chip de tres a cuatro veces proporciona un aumento de rendimiento de dos o tres veces en las primeras etapas de la vida útil del nodo del proceso, de 20 por ciento a más de la mitad. Además, FPGA es una estructura compleja pero regular, casi ideal para investigar un amplio espectro de problemas de fabricación. Esto convierte a los vendedores de FPGA en los mejores clientes madrugadores para fabs, porque dicha colaboración es fructífera para ambas partes. Fab obtiene un excelente chip de prueba, mientras que el proveedor puede superar a la competencia durante unos meses.

Aquí podemos ver un FPGA de Xilinx. El troquel superior es una parte FPGA con toneladas de contactos de 40 micrómetros para troquel intermedio llamado interpositor. El más bajo es un paquete, que tiene una docena de sus propias capas de metal.

Enorme troquel Altera FPGA para la comparación. ¡Quinientos sesenta milímetros cuadrados! Si ve a ingenieros de procesos cerca, cuídelos, existe el riesgo de sufrir un infarto.

Intel / Altera obviamente no solo mira el progreso de la competencia. Aquí está su nueva solución SiP llamada EMIB (Embedded Multi-Chip Interconnect Bridge). Un buen ejemplo es Intel Stratix 10 FPGA.

EMIB conecta un dado FPGA (aunque solo uno), dados de memoria y dados de periferia. ¿Qué es EMIB? El intercalador típico es mucho más barato que el troquel "computacional" del mismo tamaño que el intercalador utiliza un nodo de proceso mucho más grande; sin embargo, el intercalador sigue siendo enorme y, por lo tanto, es razonablemente costoso. ¿Se puede hacer más pequeño?

La respuesta de Intel es "sí podemos". La idea detrás de EMIB es usar algunos intercaladores pequeños en lugar de uno grande e integrarlos en el paquete.

Aquí hay una pequeña galería de productos creados con intercaladores. Mira lo enormes que son y cómo Xilinx se crean a partir de piezas.

Más que solo rendimiento

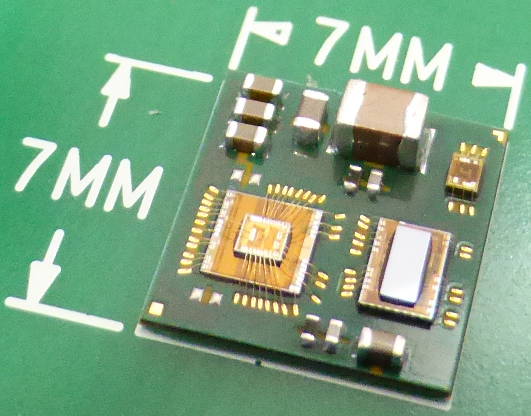

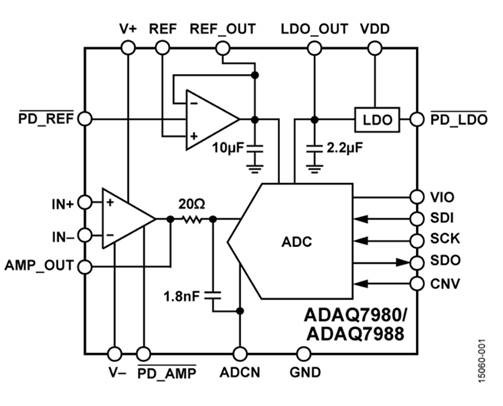

La figura a continuación es el ADC de Analog Devices y un diagrama esquemático. Parece su PCB típico, solo que más pequeño, ¿verdad? Sí, es un PCB, pero el uso de dados desnudos en lugar de paquetes permite disminuir los parásitos y su influencia en el rendimiento. El hecho de que toda la placa fue diseñada en dispositivos analógicos también agrega una capa de protección contra errores de diseño del sistema y conduce a una mejor experiencia del usuario.

También hay un truco: ¿ves dos dados empaquetados uno sobre otro? El superior integra componentes activos (transistores) de ADC y probablemente de un amplificador operacional dual, mientras que el troquel inferior consiste en pasivos (resistencias y condensadores). Colocar pasivos en troqueles separados permite hacerlos mucho más grandes y, por lo tanto, disminuir la variación de parámetros sin hacer que el troquel principal sea más grande y más caro. La disminución de la variación de parámetros es un gran problema para los circuitos analógicos, y se logra a bajo precio aquí.

Todo se podría hacer en un solo dado (y a menudo se hace, especialmente en ADC integrados), pero dicho dado será más grande (lo que podría significar "más caro" y "con menor rendimiento"), y la tecnología debe admitir todos los opciones necesarias (que también significa "más caro" debido a la mayor cantidad de máscaras). Además, cuando combina muchos bloques heterogéneos en el mismo chip, debe lidiar con su influencia cruzada. La influencia del ruido digital en las partes analógicas es probablemente la más importante, pero no la única.

Funcionalidad adicional del paquete

Como hemos visto antes, el embalaje puede hacer que el producto sea más barato e incluso mejorarlo. Pero, ¿qué pasa si usamos el paquete como una parte significativa del producto?

Intel implementó el llamado FIVR (regulador de voltaje totalmente integrado) en sus microprocesadores Haswell. El objetivo de FIVR es convertir un voltaje de entrada relativamente alto (1.8 V) en voltaje de suministro de núcleo controlable bajo y en tiempo real. Los componentes activos están en chip, mientras que los pasivos (condensadores e inductancias) se incorporan al paquete del procesador.

La inductancia integrada es un dolor de cabeza para los diseñadores de chips, porque es mala, grande y con baja inductancia. Se usa en chips de radiofrecuencia, pero casi no hay posibilidad de transferencia de energía. Intel resolvió el problema integrando docenas de pequeños inductores en el paquete del procesador. Estos inductores funcionan a 160 MHz sin núcleos ferromagnéticos. Al hacerlo, Intel simplificó significativamente los requisitos de suministro para su dispositivo.

Sin embargo, Intel finalmente desechó el FIVR y volvió a un enfoque de suministro más tradicional para las nuevas generaciones. Hubo algunos rumores de que FIVR puede volver, pero al final solo fueron rumores.

Una de las otras opciones para integrar pasivos en el paquete es LTCC (cerámica cofiada a baja temperatura). Existen algunas limitaciones y problemas (como valores nominales limitados y precisión), pero esta tecnología se desarrolla activamente. El paquete LTCC multicapa tiene este aspecto:

Aquí se representan todos los tipos de componentes pasivos, incluso el disipador de calor de metal (es un paquete para alimentación de IC de RF). Se puede decir que no es solo un paquete, sino una combinación de paquete y PCB de cerámica, estas cosas son muy populares para los circuitos de RF y relativamente baratas en pequeñas cantidades.

Que mas

Hay muchas aplicaciones potenciales para sistemas en paquete, y es imposible enumerarlas todas. También vale la pena señalar que son significativamente más baratos que los nuevos nodos de proceso, lo que impulsa su atractivo comercial.

Los sistemas optoelectrónicos son el último pero no menos importante ejemplo de este artículo. La capacidad de combinar receptor / transmisor óptico (a menudo construido en semiconductores compuestos) con chips de suministro y control de silicio es muy prometedora. La imagen a continuación es un prototipo de enlace óptico de 400 Gbit / s (y se promete 1 Tbit / s para el futuro) diseñado en IMEC.

También hay innumerables otras aplicaciones, como intercaladores con capilares integrados para refrigeración por agua (no solo para juegos y minería, sino también para interruptores y láseres), MEMS integrados y solo Dios sabe qué más. Y, obviamente, no podemos escapar de la ubicua Internet de las cosas, donde el tamaño pequeño, las bajas pérdidas y la capacidad de integrar la radio y los bloques computacionales son muy importantes.

Muchos creen que el paquete de chips es el próximo gran paso en microelectrónica, y es probable que veamos muchas ideas brillantes en el futuro cercano.