Cadence présentera Genus lors de séminaires sur le développement de puces à Saint-Pétersbourg et à Zelenograd

Nouvelles d'organisations amies (Cadence, MIET, ITMO, NPC Elvis et autres):Cadence Design Systems, l'une des deux plus grandes sociétés mondiales dans le domaine de l'automatisation du développement de micropuces, organisera des séminaires du 15 au 16 octobre à l'Institut de technologie électronique de Moscou (MIET) à Zelenograd et à Saint-Pétersbourg Université ITMO, où (selon l'expérience de mon voyage en 2012), les étudiants comprennent très bien Verilog et les systèmes sur puce.Trois sociétés russes Elekropribor, NIIMA Progress et SPC Elvis participeront également aux séminaires. Voir l' article sur la coopération avec Imagination Technologies du centre de recherche et de développement Elvis de l'organisation Elvis-Neotech sur le site Web de Rusnano.Parmi les présentations, je recommande personnellement de regarder le nouvel outil de synthèse Genus - J'ai vu et tourné sa présentation en juin à la Design Automation Conference à San Francisco:

L'annonce que j'ai reçue au sujet du séminaire russe est ci-dessous. Sur la photo de droite, je suis dans le contexte du bâtiment MIET à Zelenograd lors d'un voyage sur MIPS Technologies en 2011. Là-bas, des gens de Cadence tiendront l'un des ateliers:

Cadence Technology Days 15- 16- . : kustarev@yandex.ru. : dsd@miee.ru.

: , .. 14 « »

:

Technology day at ITMO – Seminar Title:

Virtual Model Prototyping, High Level Synthesis, Synthesis and Digital Implementation by Cadence

9:15 – 9:45 Welcome and Cadence Overview

9:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 -11:30 Break

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 Lunch

13:30 – 14:30 Cadence: Genus the new synthesis solution

14:30 – 15:30 Cadence: Innovus – state of the art digital implementation

15:30 – 15:45 Break

15:45 – 16:45 “» — experience with Cadence tools

16:45 – 17:45

17:45 – 18:15 Round table and open discussions with the speakers

:

09:00 – 09:15 .

09:15 – 09:45 Cadence; 0:30 hour.

09:45 – 11:15 Cadence: Virtual Model Prototyping

11:15 – 11:30 – .

11:30 – 12:30 Cadence: High Level Synthesis

12:30 – 13:30 .

13:30 – 14:45 Cadence: Genus the new synthesis solution

14:45 – 15:00 – .

15:00 – 16:15 Cadence: Innovus – state of the art digital implementation

16:15 – 16:45 « «» – Cadence

16:45 – 17:15 «» – Cadence Incisive .

17:15 – 18:00 , .

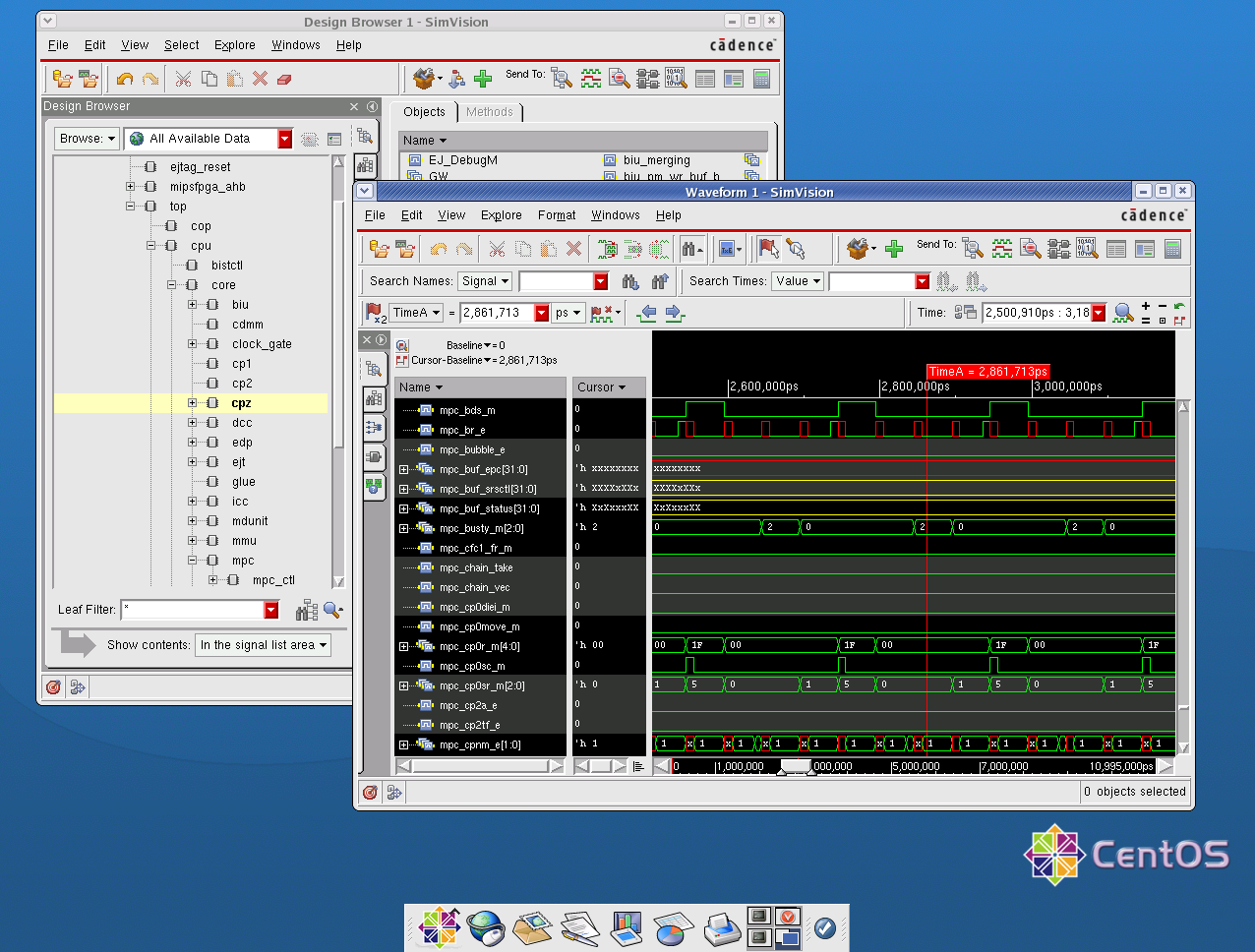

Cadence. MIPS microAptiv UP MIPSfpga SimVision:

Source: https://habr.com/ru/post/fr384913/

All Articles