T1 - Ordinateur de bricolage 8 bits discret

Il y en a toujours eu beaucoup «faits maison». Avec l'avènement du réseau, les amateurs de faire quelque chose de leurs propres mains se sont immédiatement organisés et ont créé de nombreux types de communautés, de forums et d'autres endroits où vous pouvez discuter avec votre propre type. Grâce à cela, des travaux intéressants apparaissent régulièrement sur Internet, dont certains méritent une attention particulière.L'un de ces travaux est notamment un projet de création d'un ordinateur 8 bits discret. L'auteur du projet est Andrew Starr , et le projet lui-même se trouve ici sur cette page . À quoi ressemble un projet?Selon l'auteur, il s'agit en partie d'un assemblage cinétique, en partie d'un hommage aux réalisations de la science et de la technologie et aux réalisations des dernières années. Il s'agit en partie d'un projet éducatif.Pour créer ce système, l'auteur utilise les éléments suivants:

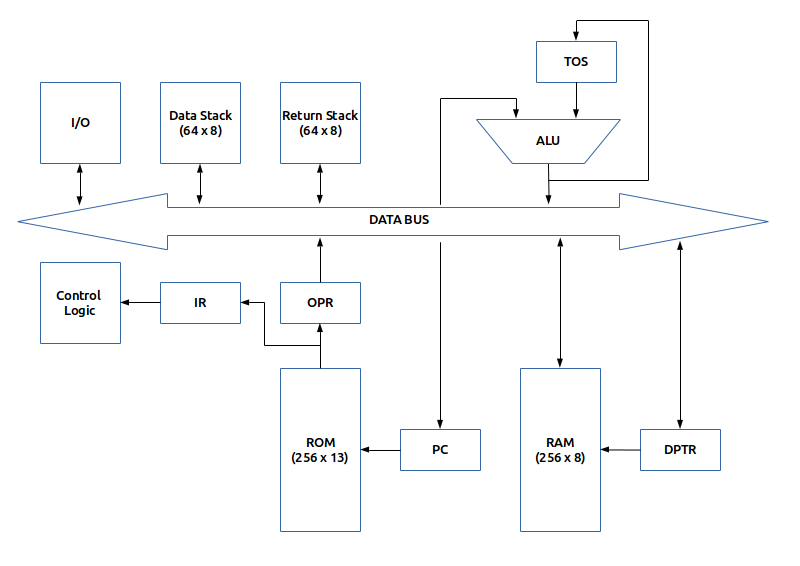

Il y en a toujours eu beaucoup «faits maison». Avec l'avènement du réseau, les amateurs de faire quelque chose de leurs propres mains se sont immédiatement organisés et ont créé de nombreux types de communautés, de forums et d'autres endroits où vous pouvez discuter avec votre propre type. Grâce à cela, des travaux intéressants apparaissent régulièrement sur Internet, dont certains méritent une attention particulière.L'un de ces travaux est notamment un projet de création d'un ordinateur 8 bits discret. L'auteur du projet est Andrew Starr , et le projet lui-même se trouve ici sur cette page . À quoi ressemble un projet?Selon l'auteur, il s'agit en partie d'un assemblage cinétique, en partie d'un hommage aux réalisations de la science et de la technologie et aux réalisations des dernières années. Il s'agit en partie d'un projet éducatif.Pour créer ce système, l'auteur utilise les éléments suivants:- Bus 8 bits

- 2 * piles 64 bits (données, retour);

- Architecture Harvard : mémoire principale de 256 octets et mémoire de programme de 256 mots;

- Mot de commande logiciel 13 bits: 5 bits par opcode, opérande 8 bits;

- Tous les éléments de mémoire sont fabriqués à l'aide de noyaux de ferrite;

- La mémoire du programme est réalisée à l'aide de transformateurs en ferrite;

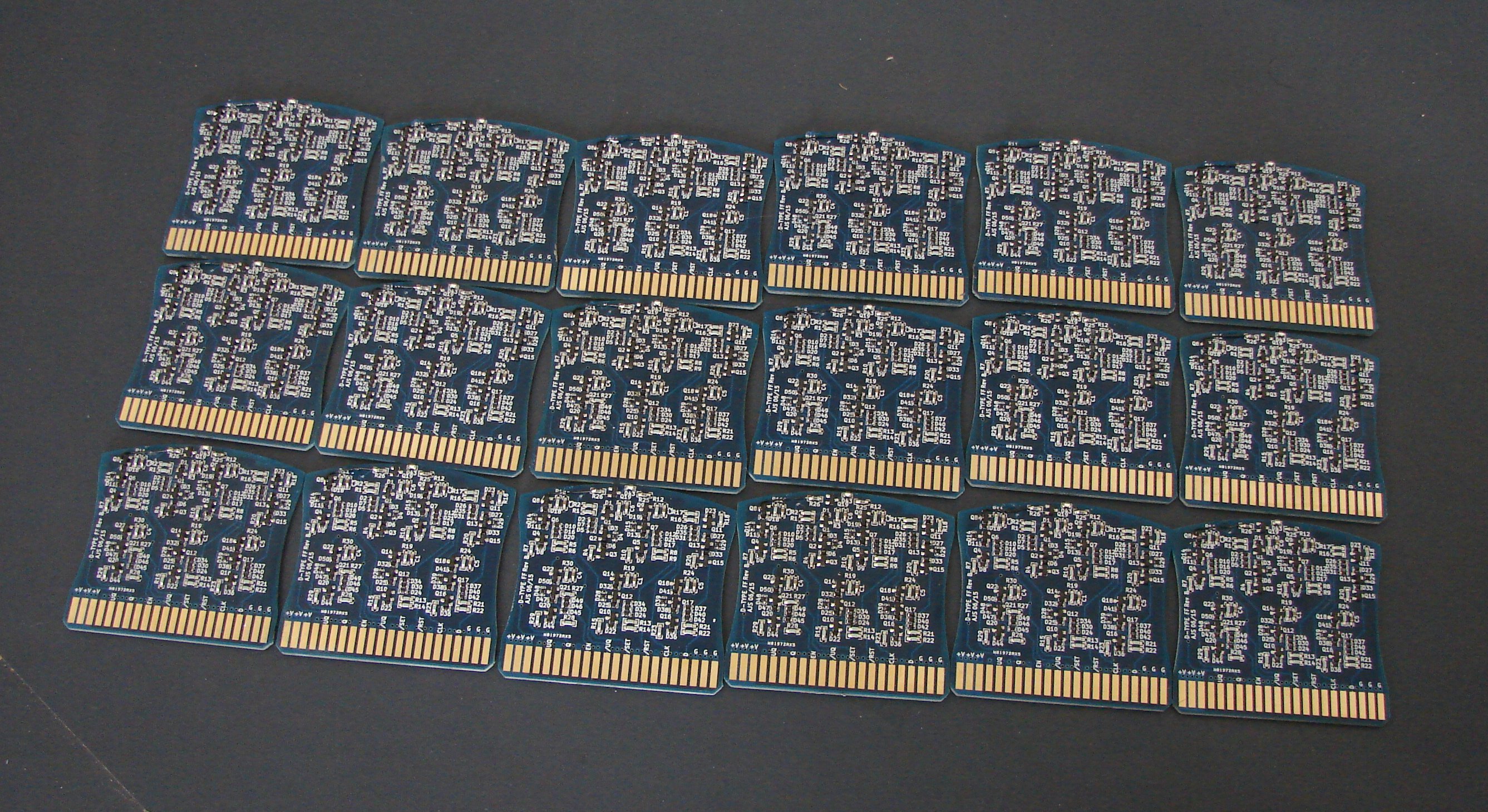

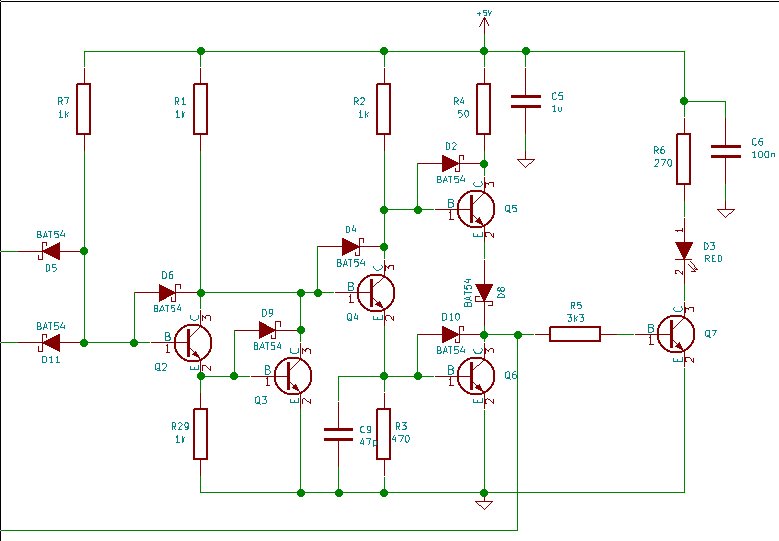

- Les éléments logiques sont constitués d'éléments discrets sous forme de modules enfichables;

- La fréquence d'horloge cible est de 1 MHz.

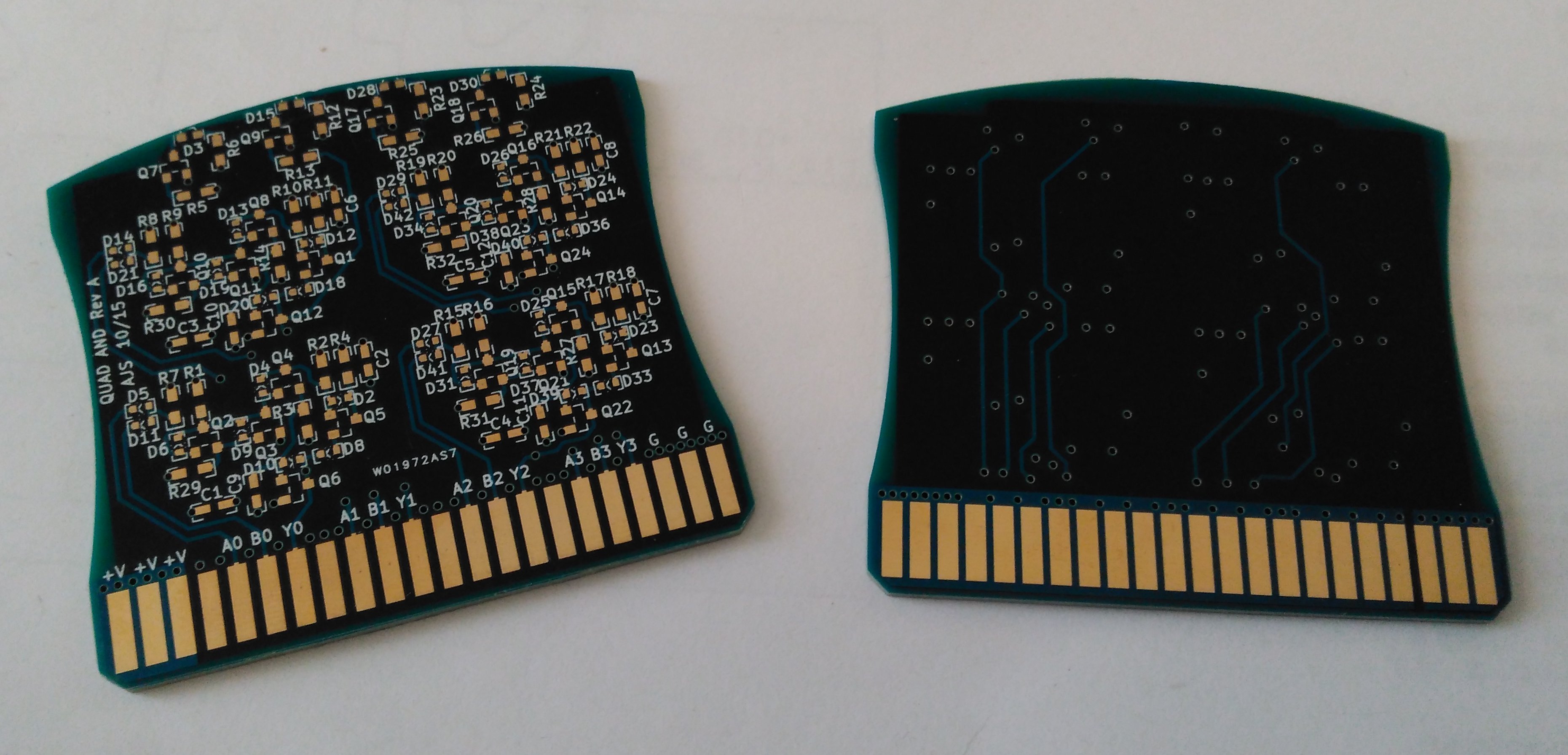

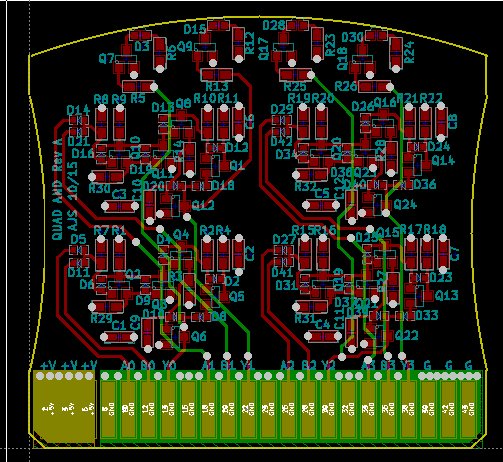

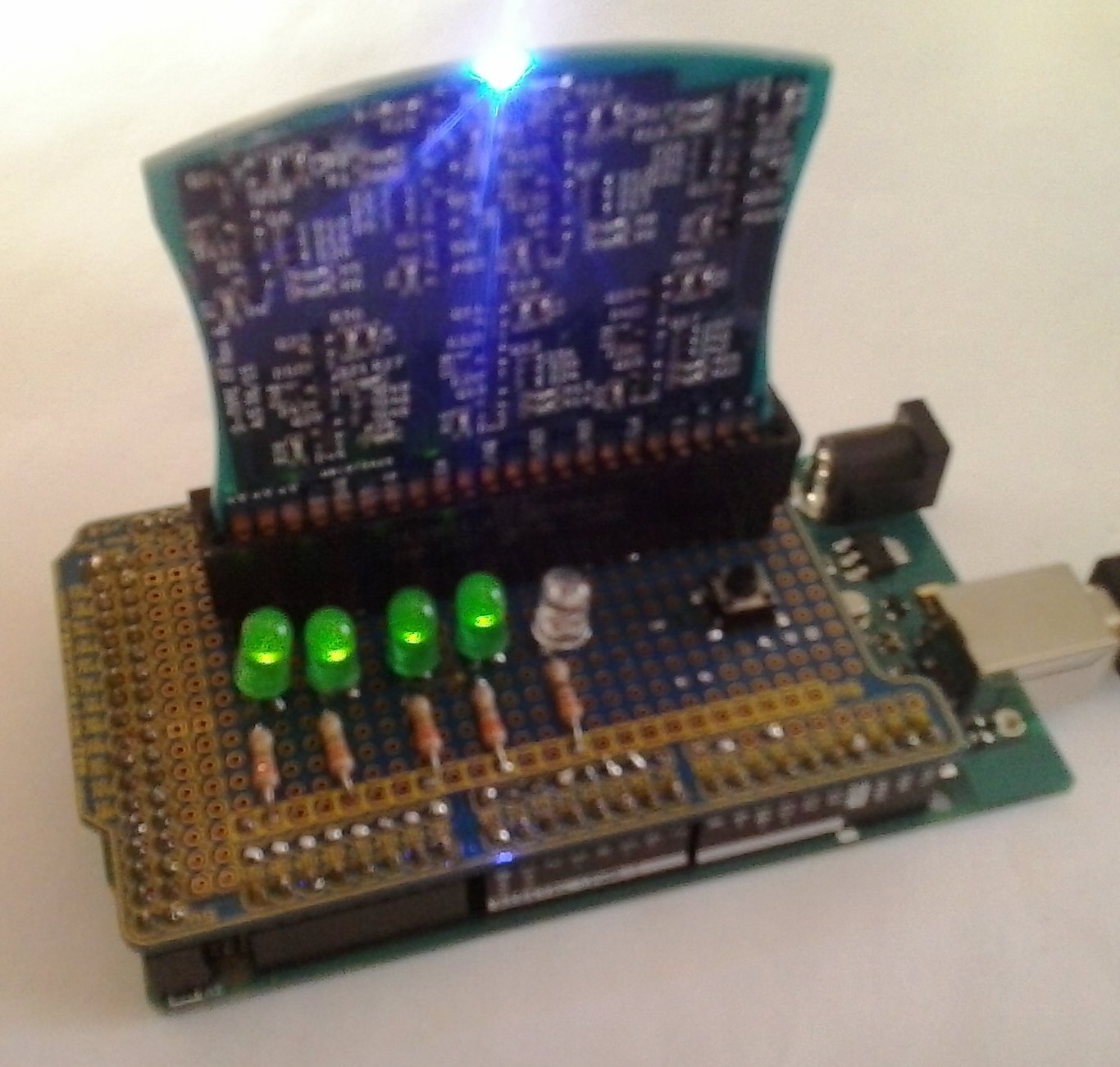

Dans l'architecture Harvard, les caractéristiques des dispositifs de mémoire pour les instructions et de la mémoire pour les données n'ont pas besoin d'être les mêmes. En particulier, la largeur des mots, la synchronisation, la technologie d'implémentation et la structure des adresses mémoire peuvent varier. Sur certains systèmes, les instructions peuvent être stockées dans une mémoire morte, tandis que le stockage de données nécessite généralement une mémoire de lecture et d'écriture. Certains systèmes nécessitent beaucoup plus de mémoire pour les instructions que de mémoire pour les données, car les données peuvent généralement être chargées à partir d'une mémoire externe ou plus lente. Un tel besoin augmente la largeur de bit (largeur) du bus d'adresses de mémoire d'instructions par rapport au bus d'adresses de mémoire de données.Architecture du système: Il utilise une machine standard à 2 piles avec plusieurs modifications qui permettent d'utiliser l'architecture Harvard et le champ de données optionnel dans les instructions.Maintenant, l'auteur a déjà développé un schéma de modules ET et commandé les modules appropriés, qui sont arrivés l'autre jour. Test des

Il utilise une machine standard à 2 piles avec plusieurs modifications qui permettent d'utiliser l'architecture Harvard et le champ de données optionnel dans les instructions.Maintenant, l'auteur a déjà développé un schéma de modules ET et commandé les modules appropriés, qui sont arrivés l'autre jour. Test des

schémas

schémas

: d'

: d' autres composants sont également prêts, y compris les décodeurs d'adresses pour la mémoire de la pile.

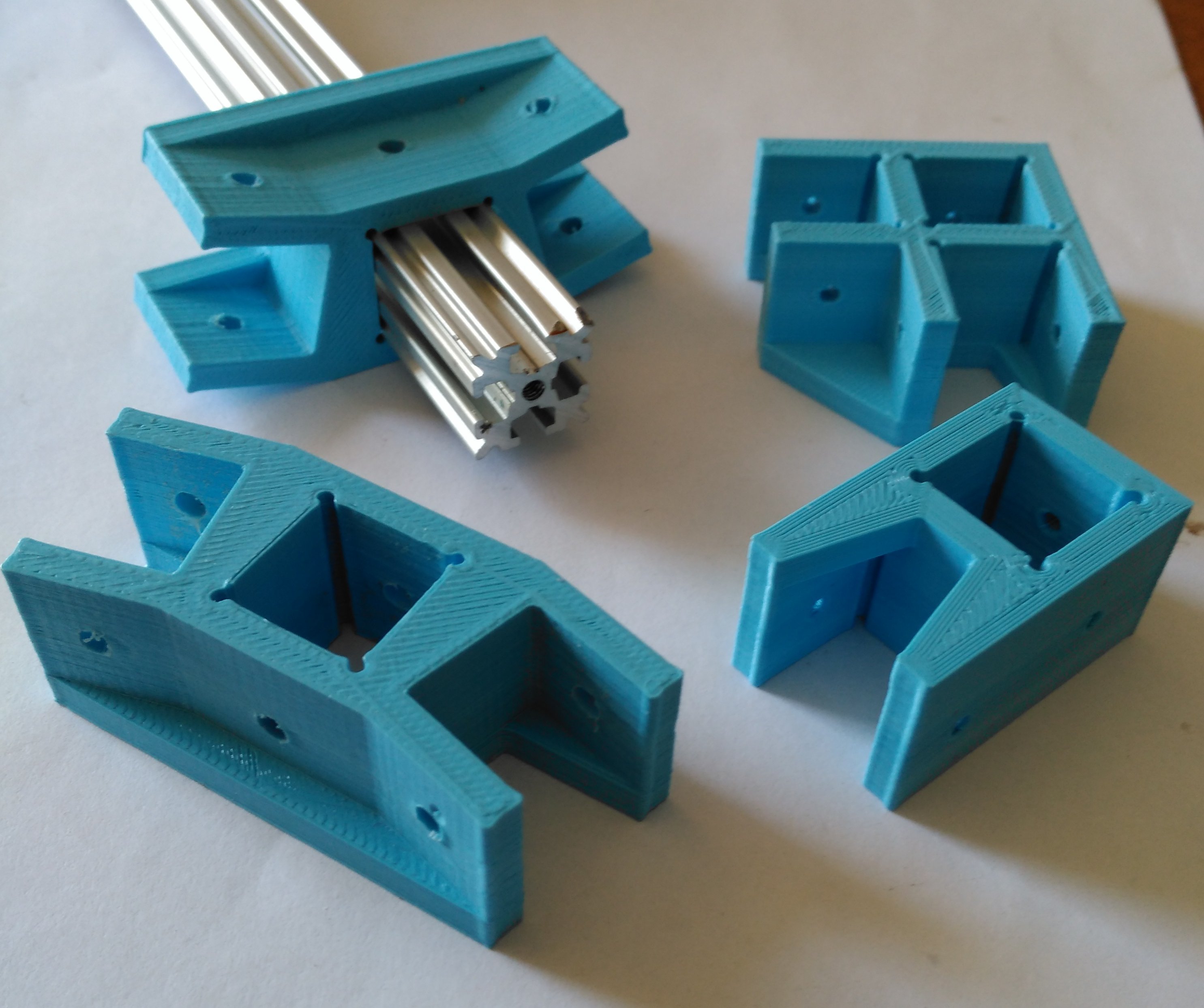

autres composants sont également prêts, y compris les décodeurs d'adresses pour la mémoire de la pile. Entre autres choses, l'auteur développe également un corps pour sa création:

Entre autres choses, l'auteur développe également un corps pour sa création: Maintenant le travail est toujours en cours, vous pouvez donc suivre le projet ici .

Maintenant le travail est toujours en cours, vous pouvez donc suivre le projet ici .Source: https://habr.com/ru/post/fr385409/

All Articles