Photos, matériaux et rebondissements du séminaire MIPSfpga au MEPhI

Fin octobre, un séminaire sur MIPSfpga a eu lieu au MEPhI - l'un d'une série de séminaires organisés par des universités russes en collaboration avec Imagination Technologies, Microchip Technology en partenariat avec Gamma St.Petersburg, des représentants du groupe Macro de Xilinx en Russie, avec la participation de conférenciers de MathWorks et NIISI. Vous trouverez ci-dessous un mélange de photographies, de liens vers du matériel, des notes sur la préparation du séminaire et une culture mythique. Ci-dessous, une photo de MEPhI à l'extérieur. Le mot «nucléaire» rappelle qu'il y a un réacteur nucléaire à l'Institut d'ingénierie physique de Moscou, donc c'est difficile d'y arriver, surtout avec un passeport américain - j'ai obtenu un laissez-passer pour deux semaines, et le recteur a signé l'ordre du séminaire. A l'entrée il y a un mitrailleur avec Kalachnikov (!) (Je n'étais pas autorisé à photographier le mitrailleur ) Me voici (Yuri Punchul) avec les autres organisateurs du séminaire - Igor Ivanovich Shagurin et Maxim Gorbunov: Igor Ivanovich Shagurin, député. Chef du département de micro et nanoélectronique - auteur d'ouvrages et d'articles sur les microprocesseurs Intel, Motorola et PowerPC, travaux de laboratoire sur MIPS . UPD: Clarification d'un camarade de NIIIS:

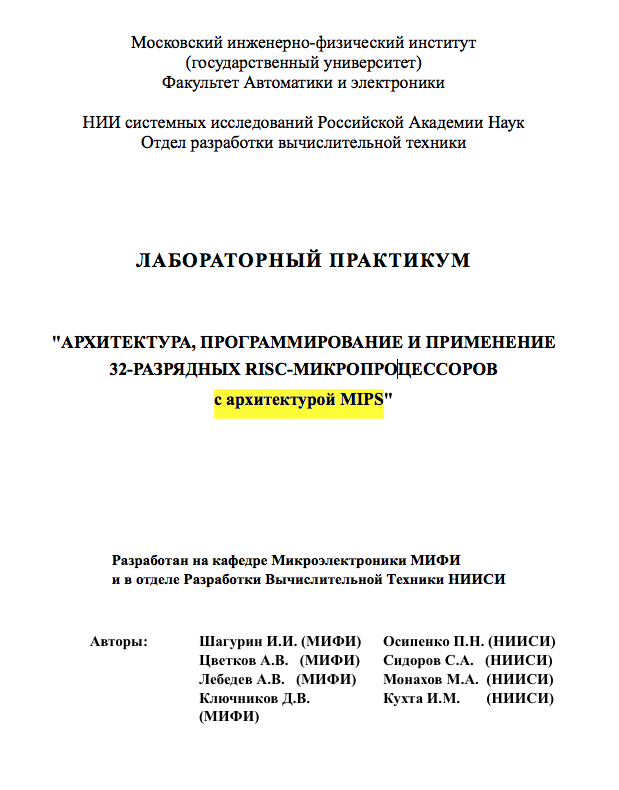

(Je n'étais pas autorisé à photographier le mitrailleur ) Me voici (Yuri Punchul) avec les autres organisateurs du séminaire - Igor Ivanovich Shagurin et Maxim Gorbunov: Igor Ivanovich Shagurin, député. Chef du département de micro et nanoélectronique - auteur d'ouvrages et d'articles sur les microprocesseurs Intel, Motorola et PowerPC, travaux de laboratoire sur MIPS . UPD: Clarification d'un camarade de NIIIS:

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

Fait intéressant, Igor Ivanovich Shagurin est allé représenter l'électronique soviétique lors d'une conférence à San Francisco dans les années 1970, lorsque l'URSS était un pays assez isolé. Les participants à cette conférence VLSI dans les années 1970 ont été emmenés à Muir Woods, la région avec les séquoias Sequoia sempervirens les plus élevés sur terre, Maxim Gorbunov , un chercheur de NIIIS / SRISA , un institut qui est également impliqué dans le développement de microprocesseurs russes avec une architecture MIPS - COMDIV-32 et COMMISSION-64. Maxim est spécialisé dans la conception de la topologie des VLSI résistants aux radiations et a été co-président d'une des sections de la conférence internationale RADECS à Moscou:

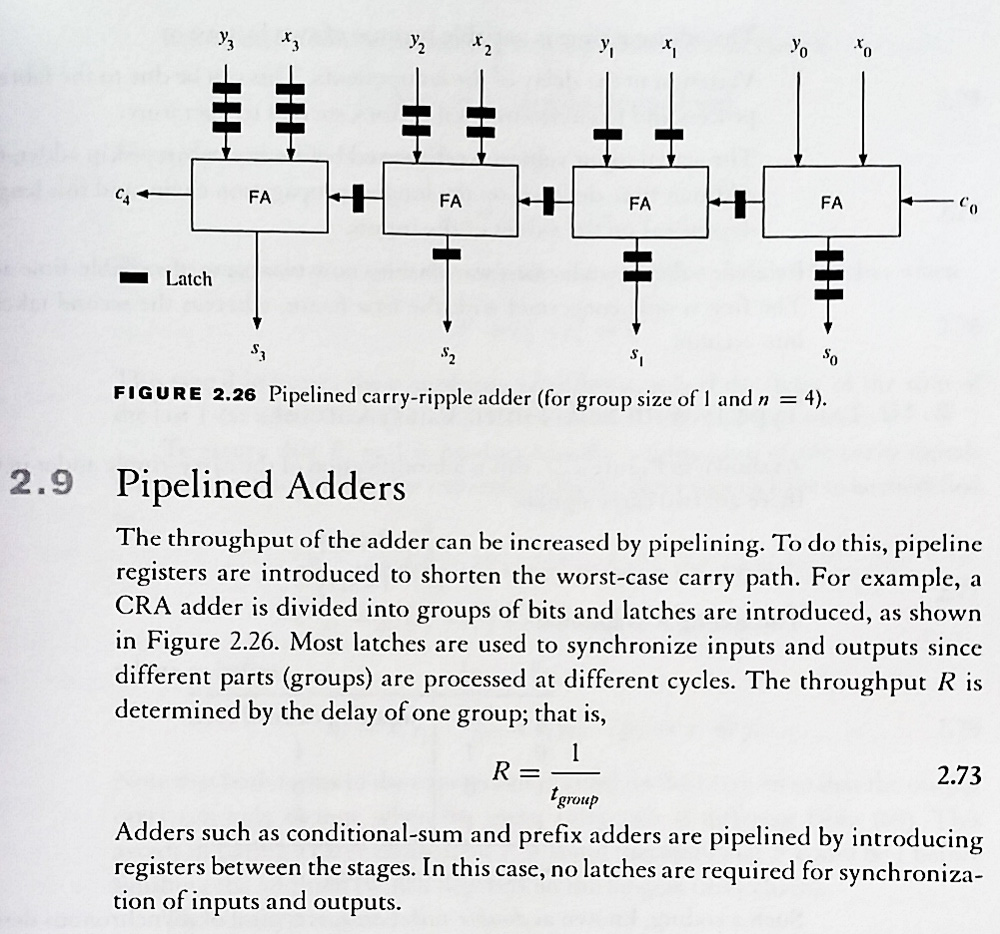

Avant le séminaire MIPSfpga à l'Institut de physique d'ingénierie de Moscou, l'un des instructeurs, Yegor Kuzmin, a commencé à me poser des questions sur les conditions de course dans un certain schéma d'informatique spécialisée qui a surgi comme projet étudiant. Je ne suis pas sûr de l'avoir bien compris, mais j'ai exprimé que dans une conception synchrone correctement organisée, de tels problèmes ne se posent pas et j'ai promis d'envoyer comme exemple une photographie d'une page du livre "Arithmétique numérique", qui comprend l'organisation de l'additionneur de pipeline, qui contient une petite quantité de logique combinatoire (la même que dans l'additionneur avec transfert séquentiel), mais place en même temps les registres (déclencheurs D) de telle manière que l'additionneur peut commencer une nouvelle opération d'addition à chaque cycle d'horloge, avec une fréquence signal d'horloge, déterminé par le retard d'un additionneur combinatoire complet à un bit:Digital Arithmetic 1st Edition de Milos D.Ercegovac et Tomás Lang En même temps, j'ai photographié quelques pages sur les circuits asynchrones à temps libre, également liés au problème .

Avant le séminaire MIPSfpga à l'Institut de physique d'ingénierie de Moscou, l'un des instructeurs, Yegor Kuzmin, a commencé à me poser des questions sur les conditions de course dans un certain schéma d'informatique spécialisée qui a surgi comme projet étudiant. Je ne suis pas sûr de l'avoir bien compris, mais j'ai exprimé que dans une conception synchrone correctement organisée, de tels problèmes ne se posent pas et j'ai promis d'envoyer comme exemple une photographie d'une page du livre "Arithmétique numérique", qui comprend l'organisation de l'additionneur de pipeline, qui contient une petite quantité de logique combinatoire (la même que dans l'additionneur avec transfert séquentiel), mais place en même temps les registres (déclencheurs D) de telle manière que l'additionneur peut commencer une nouvelle opération d'addition à chaque cycle d'horloge, avec une fréquence signal d'horloge, déterminé par le retard d'un additionneur combinatoire complet à un bit:Digital Arithmetic 1st Edition de Milos D.Ercegovac et Tomás Lang En même temps, j'ai photographié quelques pages sur les circuits asynchrones à temps libre, également liés au problème . Ensuite, j'ai été présenté à Vladimir Dementiev, qui, avec Andrei Andrianov, Dmitry Kozlovsky, anime des cours de laboratoire au MEPhI pour la programmation des microcontrôleurs Microchip PIC32MX. J'ai dit à Vladimir que le professeur Alex Dean de l' Université de Caroline du Nord a collaboré avec Imagination, Microchip et Digilent et développe actuellement un nouveau cours sur la programmation des microcontrôleurs Microchip PIC32MZCe cours comprend les RTOS et la nouvelle connexion des microcontrôleurs au cloud. Le microcontrôleur PIC32MZ est basé sur le cœur du microprocesseur MIPS microAptiv UP, le même que celui utilisé dans MIPSfpga. Par conséquent, j'ai commencé à agiter les camarades MEPhI pour participer à l'examen et (s'ils le souhaitent) aux tests bêta de ce cours: Mais revenons à notre séminaire. Le sujet du séminaire était MIPSfpga. Ce que c'est:

Ensuite, j'ai été présenté à Vladimir Dementiev, qui, avec Andrei Andrianov, Dmitry Kozlovsky, anime des cours de laboratoire au MEPhI pour la programmation des microcontrôleurs Microchip PIC32MX. J'ai dit à Vladimir que le professeur Alex Dean de l' Université de Caroline du Nord a collaboré avec Imagination, Microchip et Digilent et développe actuellement un nouveau cours sur la programmation des microcontrôleurs Microchip PIC32MZCe cours comprend les RTOS et la nouvelle connexion des microcontrôleurs au cloud. Le microcontrôleur PIC32MZ est basé sur le cœur du microprocesseur MIPS microAptiv UP, le même que celui utilisé dans MIPSfpga. Par conséquent, j'ai commencé à agiter les camarades MEPhI pour participer à l'examen et (s'ils le souhaitent) aux tests bêta de ce cours: Mais revenons à notre séminaire. Le sujet du séminaire était MIPSfpga. Ce que c'est:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

Donc, j'ai d'abord parlé et parlé de:1. Imagination Technologies et son unité commerciale MIPS2. Programmes éducatifs d'Imagination Technologies3. Pour rafraîchir le concept de flux RTL vers GDSII pour ceux dans le public qui n'avaient pas Verilog / VHDL à la spécialisation: conception des blocs IP et des systèmes sur puce (SoC).4. J'ai parlé un peu des trois lignes de cœurs de microprocesseur MIPS et plus en détail de la ligne de cœurs de classe microcontrôleur, basée sur l'une d'entre elles (MIPS microAptiv UP), le package MIPSfpga5 a été créé . Étant donné que l'un des exercices comprenait en outre la démonstration du cache, j'ai dit quelques mots et sur les caches dans MIPS microAptiv UP

Après mon premier discours, Mikhail Peselnik, un conférencier de MathWorks, a fait un discours: Mikhail Peselnik a implémenté un sous-ensemble de MIPS sur Simulink , qui a reçu une sorte de prix éditorial MATLAB Central Pick of the Week: l'exemple de Mikhail a montré que pour un étudiant, l'architecture et la microarchitecture des cœurs de processeur peuvent être étudiées de différentes manières - au moins sur Verilog et VHDL, au moins avec l'aide de modèles C, au moins avec l'aide de Simulink. Mais après avoir étudié les bases de l'architecture et de la microarchitecture, l'étudiant devrait expérimenter avec un processeur industriel, et ici MIPSfpga entre en scène avec lequel:

Après mon premier discours, Mikhail Peselnik, un conférencier de MathWorks, a fait un discours: Mikhail Peselnik a implémenté un sous-ensemble de MIPS sur Simulink , qui a reçu une sorte de prix éditorial MATLAB Central Pick of the Week: l'exemple de Mikhail a montré que pour un étudiant, l'architecture et la microarchitecture des cœurs de processeur peuvent être étudiées de différentes manières - au moins sur Verilog et VHDL, au moins avec l'aide de modèles C, au moins avec l'aide de Simulink. Mais après avoir étudié les bases de l'architecture et de la microarchitecture, l'étudiant devrait expérimenter avec un processeur industriel, et ici MIPSfpga entre en scène avec lequel:

- Les étudiants peuvent construire leurs propres prototypes de systèmes sur une puce, combinant un noyau de microprocesseur, une mémoire et des périphériques d'E / S conçus par eux

- , . « ».

- , , .

Mais pour expérimenter les développements SoC et le noyau, ils doivent avoir une bonne maîtrise de l'outil / outil d'implémentation. Par conséquent, après l'intervention de Mikhail Mikhail Filippov, ingénieur d'application de Macro Group, un représentant officiel de Xilinx en Russie. Xilinx est la société qui a autrefois inventé les FPGA et reste à ce jour n ° 1 des FPGA les plus rapides.Alexander Filippov a fait deux rapports:- Nouveaux FPGA de série 7 et MPSoC UltraScale - Produits XILINX pour des systèmes de puces programmables puissants

- Environnement de conception XILINX VIVADO pour la création de systèmes sur puce

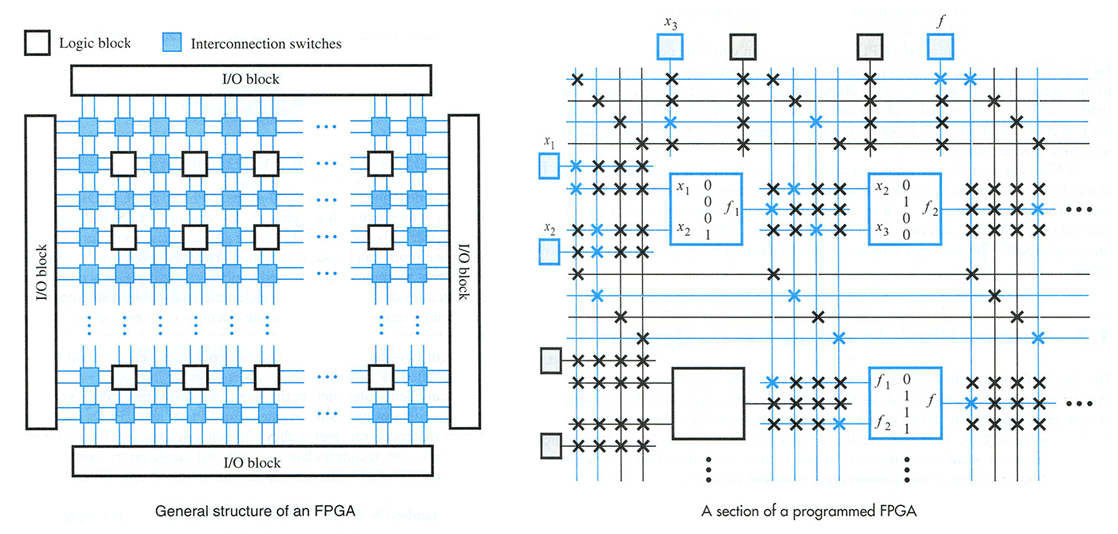

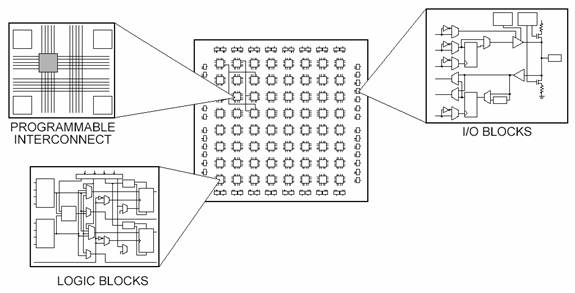

Qu'est-ce que FPGA / FPGA sur mes doigts J'ai expliqué dans un autre article sur Habr - Comment commencer à développer du fer en utilisant des FPGA - instructions étape par étape . Mais répétons cette information encore une fois:dans la version la plus simple, le FPGA est constitué d'une matrice de cellules homogènes, chacune pouvant être transformée en fonction à l'aide de multiplexeurs connectés aux bits de la mémoire de configuration. Une cellule peut devenir une porte ET avec quatre entrées et une sortie, une autre - un registre à un bit, etc. Nous chargeons une séquence de bits de la mémoire dans la mémoire de configuration - et le circuit électronique donné est formé dans le FPGA, qui peut être un processeur, un contrôleur d'affichage, etc.Les FPGA / FPGA ne sont pas des processeurs; en «programmant» des FPGA (remplissant la mémoire de configuration des FPGA), vous créez un circuit électronique (matériel), tandis que lorsque vous programmez un processeur (matériel fixe), vous glissez une chaîne d'instructions de programme séquentielles écrites dedans (Logiciel).Vous trouverez ci-dessous un schéma de l'unité FPGA la plus simple, qui comprend une table de correspondance (LUT) et une bascule. Certes, dans ce schéma, les multiplexeurs qui modifient la fonction de la cellule et les connexions à la mémoire de configuration ne sont pas affichés.

Qu'est-ce que FPGA / FPGA sur mes doigts J'ai expliqué dans un autre article sur Habr - Comment commencer à développer du fer en utilisant des FPGA - instructions étape par étape . Mais répétons cette information encore une fois:dans la version la plus simple, le FPGA est constitué d'une matrice de cellules homogènes, chacune pouvant être transformée en fonction à l'aide de multiplexeurs connectés aux bits de la mémoire de configuration. Une cellule peut devenir une porte ET avec quatre entrées et une sortie, une autre - un registre à un bit, etc. Nous chargeons une séquence de bits de la mémoire dans la mémoire de configuration - et le circuit électronique donné est formé dans le FPGA, qui peut être un processeur, un contrôleur d'affichage, etc.Les FPGA / FPGA ne sont pas des processeurs; en «programmant» des FPGA (remplissant la mémoire de configuration des FPGA), vous créez un circuit électronique (matériel), tandis que lorsque vous programmez un processeur (matériel fixe), vous glissez une chaîne d'instructions de programme séquentielles écrites dedans (Logiciel).Vous trouverez ci-dessous un schéma de l'unité FPGA la plus simple, qui comprend une table de correspondance (LUT) et une bascule. Certes, dans ce schéma, les multiplexeurs qui modifient la fonction de la cellule et les connexions à la mémoire de configuration ne sont pas affichés. Diagrammes illustrant la structure du FPGA:

Diagrammes illustrant la structure du FPGA: Et un de plus:

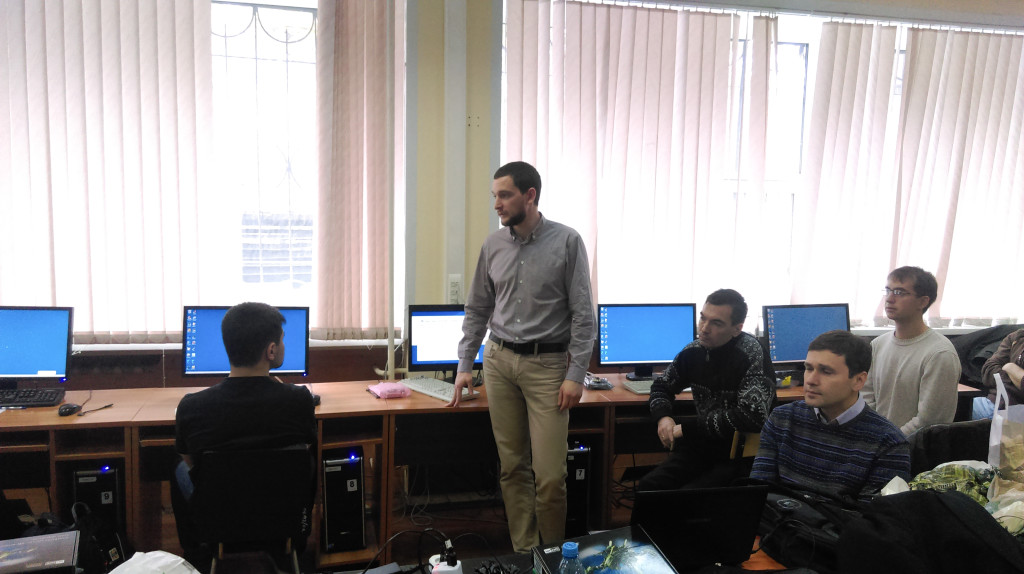

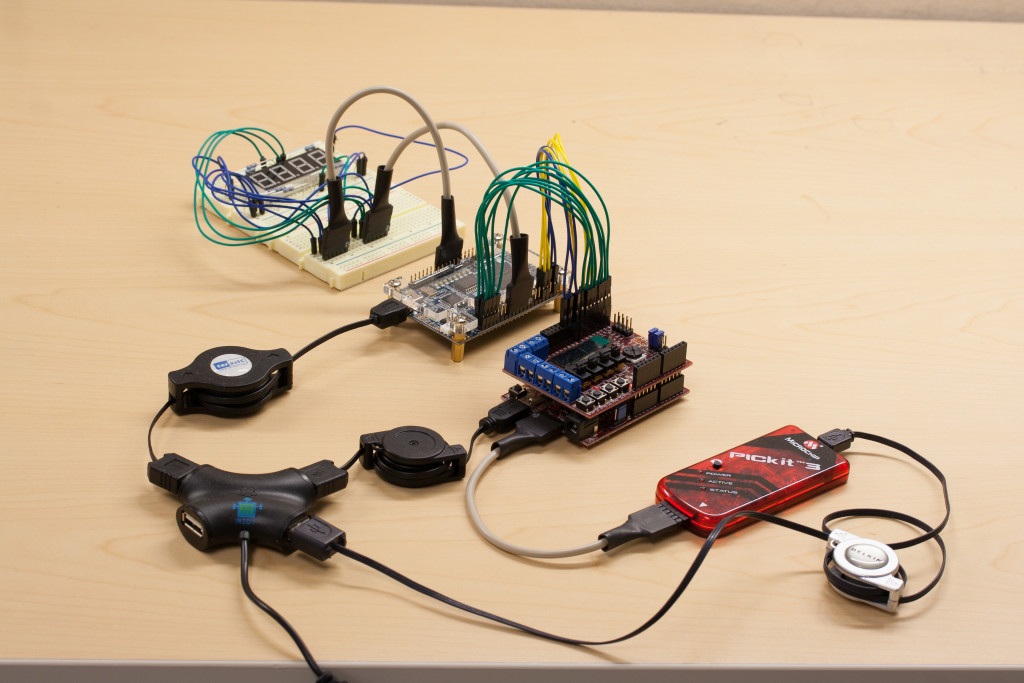

Et un de plus: Après le déjeuner dans la salle à manger de l'Institut de physique des ingénieurs de Moscou, nous avons commencé la partie pratique. Initialement, lorsque Imagination Technologies et Xilinx ont tenu un tel séminaire à Los Angeles, ils ont utilisédiapositives préparées par les professeurs David et Sarah Harris du sud de la Californie . Comme à l'origine, vous pouvez voir sur la vidéo:Les 8 vidéos de l'atelier de Los Angeles Pour les séminaires en Russie, les fixations de base et de laboratoire de Harris ont dû être substantiellement modifiées. Les modifications peuvent être trouvées sur https://github.com/MIPSfpga/mipsfpga-plus . Les différences sont les suivantes:1. Tout est trié pour les cartes mères bon marché d'Altera, disponibles en Russie sans tracteur import-export2. Le programme a été chargé dans un système synthétisé sans utiliser BusBlaster, simplement via UART3. Le capteur de lumière en tant qu'appareil périphérique au lieu d'un écran LCD4. Commutable signal d'horloge à ultra-basse fréquence, permettant aux laboratoires de visualiser le fonctionnement de tout processeur interne5. Ajout d'un laboratoire simple pour visualiser les erreurs de cache+ chaque petite chose et les cosmétiques - un chargeur de démarrage / chargeur de démarrage plus compact, la possibilité de transactions étroites non-cacheable à la mémoire, etc.Détails:1. Portage sous AlteraTout d'abord, les diapositives Harris ont tout montré pour Xilinx, et récemment, l'expédition des cartes des FPGA Xilinx vers la Russie est devenue une procédure bureaucratique assez compliquée, prenant 3-4 mois. La même chose s'est produite avec la licence du logiciel de synthèse et du Xilinx Vivado lieu et route, même avec des licences gratuites. Certaines universités russes ne disposaient pas de cartes Xilinx ni de licences Vivado; d'autres n'avaient que l'ancienne licence pour le prédécesseur de Vivado - le logiciel ISE 2013, qui ne supportait pas les FPGA sur les cartes que j'ai transportées en Russie.En bref, pour des séminaires en Russie, des camarades et moi, en Californie, avions porté MIPSfpga sur deux cartes bon marché disponibles en Russie auprès de son rival Xilinx Altera (cette société fusionne maintenant avec Intel). Les planches Alter ont été données pour les besoins de l'atelier par la société Zelenograd SPC Elvis . La carte principale de MEPhI, MIPT et SSAU était la Terasic DE0-CV basée sur Altera Cyclone V: une autre carte était la Terasic DE0-Nano - un châle très compact adapté aux projets comme les robots volants, mais avec une petite quantité de périphériques à bord: Terasic DE0 - désavantage Nano est un petit nombre de périphériques sur la carte elle-même, mais c'est aussi un avantage, car DE0-Nano peut être connecté en tant que concepteur avec d'autres cartes et intégré dans différents périphériques:

Après le déjeuner dans la salle à manger de l'Institut de physique des ingénieurs de Moscou, nous avons commencé la partie pratique. Initialement, lorsque Imagination Technologies et Xilinx ont tenu un tel séminaire à Los Angeles, ils ont utilisédiapositives préparées par les professeurs David et Sarah Harris du sud de la Californie . Comme à l'origine, vous pouvez voir sur la vidéo:Les 8 vidéos de l'atelier de Los Angeles Pour les séminaires en Russie, les fixations de base et de laboratoire de Harris ont dû être substantiellement modifiées. Les modifications peuvent être trouvées sur https://github.com/MIPSfpga/mipsfpga-plus . Les différences sont les suivantes:1. Tout est trié pour les cartes mères bon marché d'Altera, disponibles en Russie sans tracteur import-export2. Le programme a été chargé dans un système synthétisé sans utiliser BusBlaster, simplement via UART3. Le capteur de lumière en tant qu'appareil périphérique au lieu d'un écran LCD4. Commutable signal d'horloge à ultra-basse fréquence, permettant aux laboratoires de visualiser le fonctionnement de tout processeur interne5. Ajout d'un laboratoire simple pour visualiser les erreurs de cache+ chaque petite chose et les cosmétiques - un chargeur de démarrage / chargeur de démarrage plus compact, la possibilité de transactions étroites non-cacheable à la mémoire, etc.Détails:1. Portage sous AlteraTout d'abord, les diapositives Harris ont tout montré pour Xilinx, et récemment, l'expédition des cartes des FPGA Xilinx vers la Russie est devenue une procédure bureaucratique assez compliquée, prenant 3-4 mois. La même chose s'est produite avec la licence du logiciel de synthèse et du Xilinx Vivado lieu et route, même avec des licences gratuites. Certaines universités russes ne disposaient pas de cartes Xilinx ni de licences Vivado; d'autres n'avaient que l'ancienne licence pour le prédécesseur de Vivado - le logiciel ISE 2013, qui ne supportait pas les FPGA sur les cartes que j'ai transportées en Russie.En bref, pour des séminaires en Russie, des camarades et moi, en Californie, avions porté MIPSfpga sur deux cartes bon marché disponibles en Russie auprès de son rival Xilinx Altera (cette société fusionne maintenant avec Intel). Les planches Alter ont été données pour les besoins de l'atelier par la société Zelenograd SPC Elvis . La carte principale de MEPhI, MIPT et SSAU était la Terasic DE0-CV basée sur Altera Cyclone V: une autre carte était la Terasic DE0-Nano - un châle très compact adapté aux projets comme les robots volants, mais avec une petite quantité de périphériques à bord: Terasic DE0 - désavantage Nano est un petit nombre de périphériques sur la carte elle-même, mais c'est aussi un avantage, car DE0-Nano peut être connecté en tant que concepteur avec d'autres cartes et intégré dans différents périphériques:

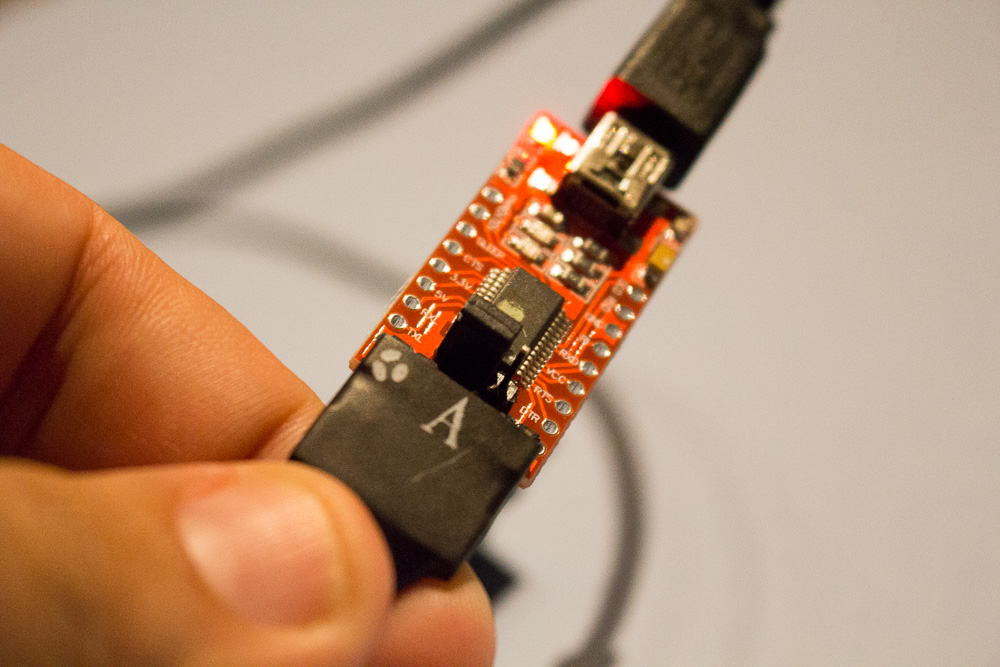

2. Téléchargement via UART Ledeuxième problème de diapositive de Harris était d'utiliser l'adaptateur de débogage Bus Blaster et le logiciel appelé OpenOCD . Fondamentalement, BusBlaster / OpenOCD est une assez bonne solution de ce type. Il permet non seulement de charger des programmes dans le système synthétisé à l'intérieur du FPGA, mais aussi de les déboguer à distance via l'interface EJTAG, un complément d'un niveau supérieur sur l'interface JTAG. Dans le même temps, BusBlaster ne coûte que 43 $, ce qui est beaucoup moins cher que les adaptateurs industriels de débogage EJTAG.Malheureusement, la combinaison BusBlaster / OpenOCD est assez grossière, et j'avais peur que cela ne fonctionne pas sur une configuration informatique inattendue en Russie (j'avais raison - cela ne fonctionnait pas au MIPT et SSAU). Outre,Sur un site qui vend une combinaison BusBlaster / OpenOCD pour MIPS , les cartes sont parfois épuisées.Pour cela et pour d'autres raisons, j'ai commencé à chercher d'autres moyens de télécharger des logiciels sur le système (dans le FPGA, vous devez charger séparément la configuration / le matériel et les logiciels du processeur (dans un système synthétisé avec un processeur)). Le troll Internet anonyme Alexey a essayé de me prendre faible pendant longtemps, afin que je puisse implémenter le chargeur de démarrage EJTAG via Altera USB Blaster, mais comme je n'étais pas un expert EJTAG, j'ai choisi une solution simple qui fonctionnait depuis l'ère soviétique - pour charger le programme via le port série / UART. Certes, à l'époque soviétique, il y avait un port RS-232C, et dans les années 1990, des puces FTDI sont apparues, ce qui a permis de tout faire via un câble USB connecté à un PC. Différentes variantes d'un tel adaptateur peuvent être achetées pour 5 $ à Moscou et pour moins de 2 $ via Internet depuis la Chine:

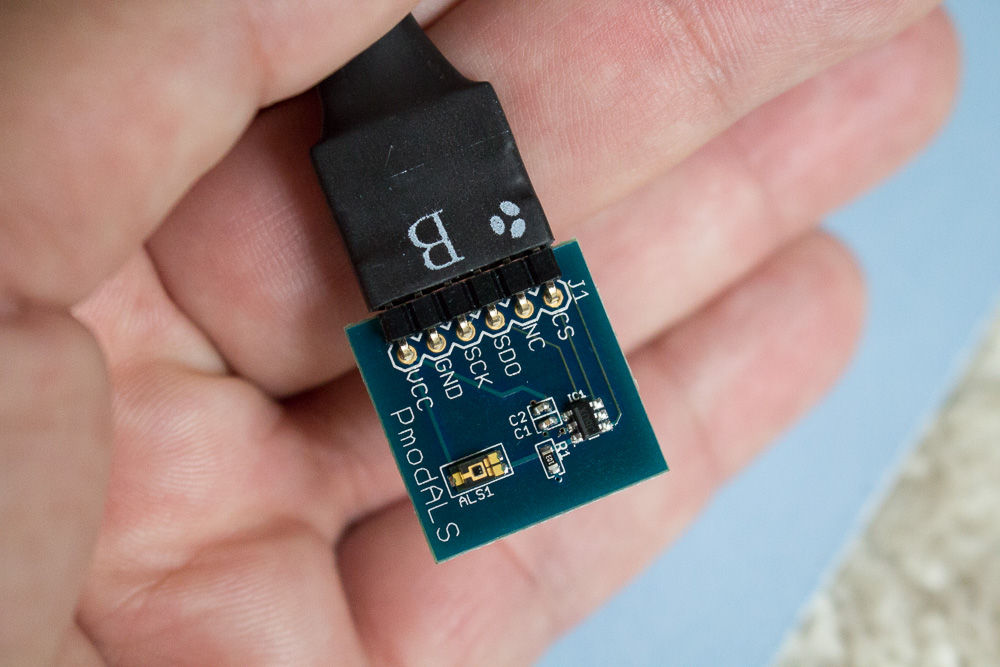

2. Téléchargement via UART Ledeuxième problème de diapositive de Harris était d'utiliser l'adaptateur de débogage Bus Blaster et le logiciel appelé OpenOCD . Fondamentalement, BusBlaster / OpenOCD est une assez bonne solution de ce type. Il permet non seulement de charger des programmes dans le système synthétisé à l'intérieur du FPGA, mais aussi de les déboguer à distance via l'interface EJTAG, un complément d'un niveau supérieur sur l'interface JTAG. Dans le même temps, BusBlaster ne coûte que 43 $, ce qui est beaucoup moins cher que les adaptateurs industriels de débogage EJTAG.Malheureusement, la combinaison BusBlaster / OpenOCD est assez grossière, et j'avais peur que cela ne fonctionne pas sur une configuration informatique inattendue en Russie (j'avais raison - cela ne fonctionnait pas au MIPT et SSAU). Outre,Sur un site qui vend une combinaison BusBlaster / OpenOCD pour MIPS , les cartes sont parfois épuisées.Pour cela et pour d'autres raisons, j'ai commencé à chercher d'autres moyens de télécharger des logiciels sur le système (dans le FPGA, vous devez charger séparément la configuration / le matériel et les logiciels du processeur (dans un système synthétisé avec un processeur)). Le troll Internet anonyme Alexey a essayé de me prendre faible pendant longtemps, afin que je puisse implémenter le chargeur de démarrage EJTAG via Altera USB Blaster, mais comme je n'étais pas un expert EJTAG, j'ai choisi une solution simple qui fonctionnait depuis l'ère soviétique - pour charger le programme via le port série / UART. Certes, à l'époque soviétique, il y avait un port RS-232C, et dans les années 1990, des puces FTDI sont apparues, ce qui a permis de tout faire via un câble USB connecté à un PC. Différentes variantes d'un tel adaptateur peuvent être achetées pour 5 $ à Moscou et pour moins de 2 $ via Internet depuis la Chine: Je noterai tout de suite que vous pouvez charger des programmes dans le SoC synthétisé de différentes manières. Dans l'un d'eux, plus traditionnel, le système a un petit programme fixe en mémoire (bootloader), qui démarre après une réinitialisation (réinitialisation) du système et charge un programme plus grand via le port UART / série. Cette méthode a été utilisée par Anton Pavlov de NIIIS, qui l'a démontrée lors de séminaires à l'Université d'État de Moscou et à l'Institut de physique des ingénieurs de Moscou, et a également écrit une note à son sujet sur les geektimes "MIPSfpga: en dehors du canon" .J'ai fait le chargement d'une manière alternative, dans laquelle la mémoire est remplie d'une machine d'état, entièrement implémentée dans le matériel. La machine accepte un fichier texte au format Motorola S-Record depuis un PC via UART, l'analyse (tout ce qui se trouve dans le matériel) et remplit la mémoire de données, tandis que le processeur est dans un état de réinitialisation. Ensuite, le processeur se réveille et commence à lire le programme à partir de la mémoire système. Tout ce qui doit être fait du côté PC est de convertir le fichier ELF exécutable au format Motorola S-Record et de l'envoyer au port COM virtuel avec la commande "type" windows-shell.3. Capteur de lumière comme périphérique au lieu d'un écran LCDDans les laboratoires Harris d'origine, ils ont utilisé un indicateur à sept segments et un écran LCD SPI comme exemples de périphériques. Un exemple avec un indicateur à sept segments est ennuyeux - tout élève comprend que si vous savez comment clignoter avec une seule lumière, alors vous savez comment clignoter avec sept lumières. L'exemple SPI est un peu meilleur, surtout quand il s'agit d'étudiants débutants, mais pourquoi avons-nous besoin d'un deuxième affichage s'il y a déjà un indicateur à sept segments? En bref, avant de voyager en Russie, j'ai acheté 20 capteurs de lumière, également avec une interface SPI, et les ai utilisés à la place des écrans: En même temps, l'interface est très simple - voici le module d'interface que j'ai écrit (note: ce code n'inclut pas toutes les modifications du système pour l'appairer avec Bus AHB-Lite, pour que le logiciel voie la valeur):

Je noterai tout de suite que vous pouvez charger des programmes dans le SoC synthétisé de différentes manières. Dans l'un d'eux, plus traditionnel, le système a un petit programme fixe en mémoire (bootloader), qui démarre après une réinitialisation (réinitialisation) du système et charge un programme plus grand via le port UART / série. Cette méthode a été utilisée par Anton Pavlov de NIIIS, qui l'a démontrée lors de séminaires à l'Université d'État de Moscou et à l'Institut de physique des ingénieurs de Moscou, et a également écrit une note à son sujet sur les geektimes "MIPSfpga: en dehors du canon" .J'ai fait le chargement d'une manière alternative, dans laquelle la mémoire est remplie d'une machine d'état, entièrement implémentée dans le matériel. La machine accepte un fichier texte au format Motorola S-Record depuis un PC via UART, l'analyse (tout ce qui se trouve dans le matériel) et remplit la mémoire de données, tandis que le processeur est dans un état de réinitialisation. Ensuite, le processeur se réveille et commence à lire le programme à partir de la mémoire système. Tout ce qui doit être fait du côté PC est de convertir le fichier ELF exécutable au format Motorola S-Record et de l'envoyer au port COM virtuel avec la commande "type" windows-shell.3. Capteur de lumière comme périphérique au lieu d'un écran LCDDans les laboratoires Harris d'origine, ils ont utilisé un indicateur à sept segments et un écran LCD SPI comme exemples de périphériques. Un exemple avec un indicateur à sept segments est ennuyeux - tout élève comprend que si vous savez comment clignoter avec une seule lumière, alors vous savez comment clignoter avec sept lumières. L'exemple SPI est un peu meilleur, surtout quand il s'agit d'étudiants débutants, mais pourquoi avons-nous besoin d'un deuxième affichage s'il y a déjà un indicateur à sept segments? En bref, avant de voyager en Russie, j'ai acheté 20 capteurs de lumière, également avec une interface SPI, et les ai utilisés à la place des écrans: En même temps, l'interface est très simple - voici le module d'interface que j'ai écrit (note: ce code n'inclut pas toutes les modifications du système pour l'appairer avec Bus AHB-Lite, pour que le logiciel voie la valeur):

4. L'horloge est passée à l'ultra-basse fréquence Lorsque MIPSfpga est apparu et que des professeurs d'université russes ont commencé à l'étudier, certains d'entre eux ont commencé à se plaindre que le package dans sa forme originale n'était pas très intéressant pour les étudiants avancés, car les laboratoires préparés par David et Sarah Harris utilisent un processeur comme une «boîte noire», en y connectant simplement des appareils. En d'autres termes, Harris a complètement ignoré que le processeur est indiqué dans le code source, et il est donc possible d'implémenter avec lui des laboratoires qui permettraient de sortir des connexions à partir de registres de processeur arbitraires (non seulement des registres visibles par le programmeur, mais généralement de tout déclencheur D), pour se connecter par exemple, aux LED et observez ce qui arrive au processeur lors de l'exécution de certains programmes.Comme vous le comprenez, pour rendre ces observations «en direct», il est nécessaire de faire fonctionner le processeur à une fréquence d'horloge très basse, par exemple une horloge par seconde. Comment faire? Le cœur MIPS microAptiv UP implémenté en ASIC sur la technologie 28 nm peut fonctionner à des fréquences supérieures à 500 MHz, et sur la technologie 65 nm sur 300 MHz. Lorsqu'elles sont implémentées sur des FPGA, les fréquences sont beaucoup plus basses, mais toujours élevées - 50-60 MHz. Les fréquences des générateurs de signaux d'horloge sur les cartes sont de 50 à 100 MHz, avec la possibilité d'augmenter ou de diminuer la fréquence en utilisant une boucle à verrouillage de phase (PLL) / boucle à verrouillage de phase (PLL) .Malheureusement, en utilisant PLL, vous pouvez réduire la fréquence à ~ 100 KHz, mais vous devez réduire la fréquence à 1 Hz d'une autre manière. Au début, j'ai essayé de le faire en utilisant un bloc d'Altera appeléALTCLKCTRL , mais pour une raison quelconque, cela n'a pas fonctionné. Ensuite, j'ai essayé de diviser le signal d'horloge à l'aide d'un compteur, mais (je le savais déjà) cette solution en elle-même ne fonctionne pas, car le synthétiseur ne comprend pas que le signal de sortie est un signal d'horloge et commence à le diviser incorrectement, ce qui fait que le processeur ne fonctionne pas. J'ai consulté plusieurs amis et nous avons commencé à utiliser l'alter macro «global» (et son équivalent sur Xilinx BUFG). 5. Ajout d'un simple laboratoire de visualisation des erreurs de cache

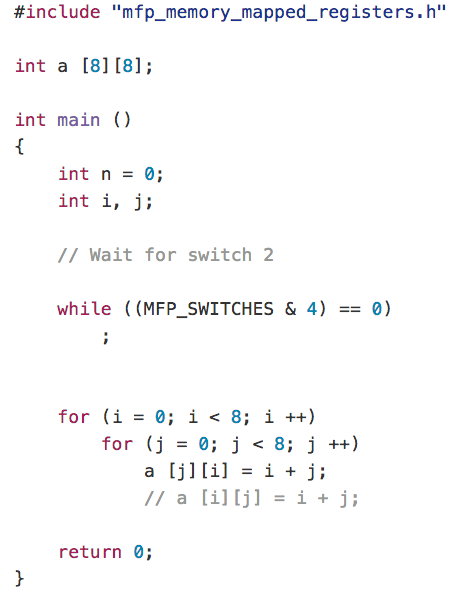

4. L'horloge est passée à l'ultra-basse fréquence Lorsque MIPSfpga est apparu et que des professeurs d'université russes ont commencé à l'étudier, certains d'entre eux ont commencé à se plaindre que le package dans sa forme originale n'était pas très intéressant pour les étudiants avancés, car les laboratoires préparés par David et Sarah Harris utilisent un processeur comme une «boîte noire», en y connectant simplement des appareils. En d'autres termes, Harris a complètement ignoré que le processeur est indiqué dans le code source, et il est donc possible d'implémenter avec lui des laboratoires qui permettraient de sortir des connexions à partir de registres de processeur arbitraires (non seulement des registres visibles par le programmeur, mais généralement de tout déclencheur D), pour se connecter par exemple, aux LED et observez ce qui arrive au processeur lors de l'exécution de certains programmes.Comme vous le comprenez, pour rendre ces observations «en direct», il est nécessaire de faire fonctionner le processeur à une fréquence d'horloge très basse, par exemple une horloge par seconde. Comment faire? Le cœur MIPS microAptiv UP implémenté en ASIC sur la technologie 28 nm peut fonctionner à des fréquences supérieures à 500 MHz, et sur la technologie 65 nm sur 300 MHz. Lorsqu'elles sont implémentées sur des FPGA, les fréquences sont beaucoup plus basses, mais toujours élevées - 50-60 MHz. Les fréquences des générateurs de signaux d'horloge sur les cartes sont de 50 à 100 MHz, avec la possibilité d'augmenter ou de diminuer la fréquence en utilisant une boucle à verrouillage de phase (PLL) / boucle à verrouillage de phase (PLL) .Malheureusement, en utilisant PLL, vous pouvez réduire la fréquence à ~ 100 KHz, mais vous devez réduire la fréquence à 1 Hz d'une autre manière. Au début, j'ai essayé de le faire en utilisant un bloc d'Altera appeléALTCLKCTRL , mais pour une raison quelconque, cela n'a pas fonctionné. Ensuite, j'ai essayé de diviser le signal d'horloge à l'aide d'un compteur, mais (je le savais déjà) cette solution en elle-même ne fonctionne pas, car le synthétiseur ne comprend pas que le signal de sortie est un signal d'horloge et commence à le diviser incorrectement, ce qui fait que le processeur ne fonctionne pas. J'ai consulté plusieurs amis et nous avons commencé à utiliser l'alter macro «global» (et son équivalent sur Xilinx BUFG). 5. Ajout d'un simple laboratoire de visualisation des erreurs de cache Vous pouvez maintenant faire des expériences intéressantes - par exemple, pour faire clignoter la LED lors d'un échec de cache, puis observer en temps réel les hits et les ratés du cache lors du remplissage d'un tableau à deux dimensions. Si vous remplissez le tableau ligne par ligne, les clignotements seront différents de ceux que vous remplissez dans les colonnes: il convient de noter que tout ne s'est pas bien passé:

Vous pouvez maintenant faire des expériences intéressantes - par exemple, pour faire clignoter la LED lors d'un échec de cache, puis observer en temps réel les hits et les ratés du cache lors du remplissage d'un tableau à deux dimensions. Si vous remplissez le tableau ligne par ligne, les clignotements seront différents de ceux que vous remplissez dans les colonnes: il convient de noter que tout ne s'est pas bien passé: 1. Le GPIO dans DE0-Nano est différent des GPIO dans les cartes DE0-CV et Xilinx. En particulier, pour une raison quelconque, je n'ai pas pu déclarer l'intégralité du port GPIO comme un inout, puis utiliser ses bits individuels comme entrée ou comme sortie. Bien que sur DE0-CV, cela se passe bien. Je n'ai pas eu le temps de diviser les différentes sorties GPIO entre différents signaux logiques (sur Verilog), donc je n'ai pas trié le laboratoire avec le capteur de lumière sur DE0-Nano. Pour la même raison, je n'ai pas exporté l'interface avec le Bus Blaster vers le DE0-CV.2. Pire encore, le téléchargement via UART pour DE0-Nano ne fonctionnait pas chez MEPhI, bien qu'avant cela fonctionnait à l'Université d'État de Moscou et sur mon ordinateur portable. La raison n'est toujours pas claire à 100%:2.1. Il y a peut-être eu un problème d'incompatibilité de la version de Windows (7 avec le patch) et du câble USB-UART utilisé pour DE0-Nano. Le câble était un clone de câble chinois bon marché basé sur le chipset PL2303TA, bien que je ne l'ai pas essayé avant le séminaire. Il est connu que la version précédente de tels câbles basés sur des chipsets avec PL2303HX avait un problème de compatibilité avec Windows 8 ( voir ). Le plus odieux que j'ai eu avec moi un ordinateur portable avec une version de Windows 7, et un ordinateur portable avec une version de Windows 8, et diverses alternatives à ce cordon. Mais je n'ai pas vérifié toutes les combinaisons avant le séminaire, bien que j'aurais pu le faire la veille - hélas.2.2. Deux jours avant l'atelier, j'ai apporté des modifications au diviseur d'horloge. Cela ne valait pas la peine non plus.2.3. Eh bien, au moins tout a bien fonctionné sur le DE0-CV.3. Au MEPhI, j'ai montré une version plus complexe de l'exemple de cache qu'auparavant à l'Université d'État de Moscou. C'était une erreur - dans un exemple complexe, le compilateur a optimisé quelque chose, et le motif des lumières n'était pas aussi évident que dans l'exemple simple d'origine. La situation a été quelque peu sauvée par le conférencier supplémentaire invité de NIIMI Anton Pavlov, qui, bien qu'il n'ait pas eu le temps au MEPhI, a montré à certains de présenter sa propre version de la liaison MIPSfpga appelée myMIPSfpga, qu'il a également décrite dans la note "MIPSfpga: en dehors du canon . " Entre autres choses, Anton a porté MIPSfpga sur la carte russe Mars rover 3

1. Le GPIO dans DE0-Nano est différent des GPIO dans les cartes DE0-CV et Xilinx. En particulier, pour une raison quelconque, je n'ai pas pu déclarer l'intégralité du port GPIO comme un inout, puis utiliser ses bits individuels comme entrée ou comme sortie. Bien que sur DE0-CV, cela se passe bien. Je n'ai pas eu le temps de diviser les différentes sorties GPIO entre différents signaux logiques (sur Verilog), donc je n'ai pas trié le laboratoire avec le capteur de lumière sur DE0-Nano. Pour la même raison, je n'ai pas exporté l'interface avec le Bus Blaster vers le DE0-CV.2. Pire encore, le téléchargement via UART pour DE0-Nano ne fonctionnait pas chez MEPhI, bien qu'avant cela fonctionnait à l'Université d'État de Moscou et sur mon ordinateur portable. La raison n'est toujours pas claire à 100%:2.1. Il y a peut-être eu un problème d'incompatibilité de la version de Windows (7 avec le patch) et du câble USB-UART utilisé pour DE0-Nano. Le câble était un clone de câble chinois bon marché basé sur le chipset PL2303TA, bien que je ne l'ai pas essayé avant le séminaire. Il est connu que la version précédente de tels câbles basés sur des chipsets avec PL2303HX avait un problème de compatibilité avec Windows 8 ( voir ). Le plus odieux que j'ai eu avec moi un ordinateur portable avec une version de Windows 7, et un ordinateur portable avec une version de Windows 8, et diverses alternatives à ce cordon. Mais je n'ai pas vérifié toutes les combinaisons avant le séminaire, bien que j'aurais pu le faire la veille - hélas.2.2. Deux jours avant l'atelier, j'ai apporté des modifications au diviseur d'horloge. Cela ne valait pas la peine non plus.2.3. Eh bien, au moins tout a bien fonctionné sur le DE0-CV.3. Au MEPhI, j'ai montré une version plus complexe de l'exemple de cache qu'auparavant à l'Université d'État de Moscou. C'était une erreur - dans un exemple complexe, le compilateur a optimisé quelque chose, et le motif des lumières n'était pas aussi évident que dans l'exemple simple d'origine. La situation a été quelque peu sauvée par le conférencier supplémentaire invité de NIIMI Anton Pavlov, qui, bien qu'il n'ait pas eu le temps au MEPhI, a montré à certains de présenter sa propre version de la liaison MIPSfpga appelée myMIPSfpga, qu'il a également décrite dans la note "MIPSfpga: en dehors du canon . " Entre autres choses, Anton a porté MIPSfpga sur la carte russe Mars rover 3 que moi, en tant que personne torturée par l'exportation-importation (Scylla: contrôle des exportations américaines + Charybdis: douanes russes), je vais essayer d'utiliser pour les événements éducatifs suivants en Russie: Pendant la pause et après le séminaire, Maxim Gorbunov m'a montré divers sites mythiques, dont trois panneaux dans l'esprit de l'ère de la galaxie d'Andromède et du café moléculaire de multi-volume rouge et blanc datent de 1960: UPD: Comme dans les commentaires a commencé à discuter de l'église mifishnuyu, et je ferai à ce sujet (je ne suis pas inséré l Ce fragment était à l'origine, car il n'était pas sûr qu'il soit approprié pour les geektimes):

que moi, en tant que personne torturée par l'exportation-importation (Scylla: contrôle des exportations américaines + Charybdis: douanes russes), je vais essayer d'utiliser pour les événements éducatifs suivants en Russie: Pendant la pause et après le séminaire, Maxim Gorbunov m'a montré divers sites mythiques, dont trois panneaux dans l'esprit de l'ère de la galaxie d'Andromède et du café moléculaire de multi-volume rouge et blanc datent de 1960: UPD: Comme dans les commentaires a commencé à discuter de l'église mifishnuyu, et je ferai à ce sujet (je ne suis pas inséré l Ce fragment était à l'origine, car il n'était pas sûr qu'il soit approprié pour les geektimes):

Je suis allé à l'église mythique, autour de laquelle il y avait tellement de cris sur Internet il y a environ trois ans, à cause de laquelle des employés ont même quitté l'Institut de génie physique de Moscou pour protester. En tant que personne neutre, c'est-à-dire vraiment incroyant, pas partisan militant de l'un ou l'autre côté du conflit, je dois dire que 1) l'église mythique est plutôt modeste et non vulgaire, semblable dans son esprit à la cathédrale orthodoxe de San Francisco; 2) MEPhI n'est pas la première université russe avec une religion, le cours d'orthodoxie est apparu à l'Institut de physique et de technologie de Moscou déjà en 1988 (alors tout le collège de physique et de technologie est venu vers lui, les étudiants ont écouté la première conférence debout, mais après trois mois, il ne restait plus qu'une douzaine d'étudiants); 3) il existe des églises dans de nombreuses universités américaines. À suivre.

Je suis allé à l'église mythique, autour de laquelle il y avait tellement de cris sur Internet il y a environ trois ans, à cause de laquelle des employés ont même quitté l'Institut de génie physique de Moscou pour protester. En tant que personne neutre, c'est-à-dire vraiment incroyant, pas partisan militant de l'un ou l'autre côté du conflit, je dois dire que 1) l'église mythique est plutôt modeste et non vulgaire, semblable dans son esprit à la cathédrale orthodoxe de San Francisco; 2) MEPhI n'est pas la première université russe avec une religion, le cours d'orthodoxie est apparu à l'Institut de physique et de technologie de Moscou déjà en 1988 (alors tout le collège de physique et de technologie est venu vers lui, les étudiants ont écouté la première conférence debout, mais après trois mois, il ne restait plus qu'une douzaine d'étudiants); 3) il existe des églises dans de nombreuses universités américaines. À suivre.

Source: https://habr.com/ru/post/fr387157/

All Articles