Prototypage ASIC sur FPGA

Le développement de puces est complexe, coûteux et prend du temps. Et le prix de toute erreur est extrêmement élevé. Après avoir fait le cristal avec des correctifs et des mises à jour, rien ne peut être corrigé. Par conséquent, la vérification des schémas conçus au stade du développement est particulièrement méticuleuse. Pour chaque bloc fonctionnel, des tests de bloc sont écrits dans tous les modes de fonctionnement et hors fonctionnement. Après avoir intégré le bloc dans le circuit général, des tests système sont effectués sur le fonctionnement de ce bloc dans le cadre du système. Tous les tests tournent constamment dans les tests de régression. Il y a même un signe informel d'un niveau de test moins ou moins acceptable - lorsque la quantité de code de test est 10 fois la quantité de code de l'unité testée. Mais tous ces tests ne donnent pas l'impression que le circuit est viable, car toute simulation est le comportement du circuit pendant des centaines de millisecondes maximum.Mais dans la vie, le circuit devrait fonctionner sur des centaines de milliers d'heures. Une fois, j'ai cherché un échec lorsque 1 ou 2 octets ont été perdus pour 1 Go d'informations transmises et aucun test fonctionnel n'a trouvé ce problème. Et cette erreur ne s'est manifestée que sur le prototype FPGA de la future puce. À propos des prototypes que nous avons réalisés et de ce qui se passe dans le monde, cet article vous le dira.Le prototypage de futures puces sur un FPGA est le seul moyen de tester le fonctionnement du circuit sur des tâches du monde réel en moins de temps réel. Le prototype vous permet de déboguer le logiciel, d'obtenir les caractéristiques de performances initiales et bien plus encore. Les FPGA modernes disposent de suffisamment de ressources pour ces tâches. Par exemple, vous pouvez vous-même implémenter un ordinateur à part entière avec un processeur Intel 8086 sur une carte mère avec FPGA pour 300 $ .2004 année

Malheureusement, nous n'avons pas pu trouver le tout premier prototype dans les dépôts de notre armoire à squelettes, mais c'était une petite écharpe basée sur le Xilinx Spartan3-400 (XC3S400). 400 signifie le nombre de milliers d'équivalents de valve dont dispose le développeur pour créer son circuit. Le prix du mouchoir était d'environ 50 $ et permettait d'y implanter un simple microcontrôleur 8 bits avec toute la mémoire et à une fréquence de 40 MHz. Le prototypage a consisté dans le fait que le microcontrôleur développé dessus clignote une LED.2005 année

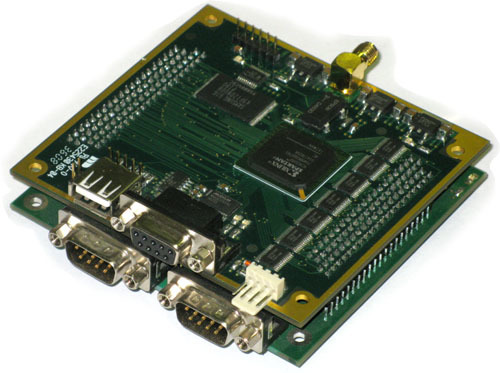

La carte spéciale pour le prototype a déjà été développée non pas comme une expérience, mais comme une étape significative du projet. FPGA Xilinx Spartan3-1000 déjà appliqué. Ceux. 1 million de vannes étaient déjà à notre disposition et le microcontrôleur conçu fonctionnait à sa fréquence maximale de 48 MHz. Et c'est sur cette carte que j'ai récupéré les 2 octets perdus par gigaoctet. Le prix de la planche était d'environ 200 $.

2007 année

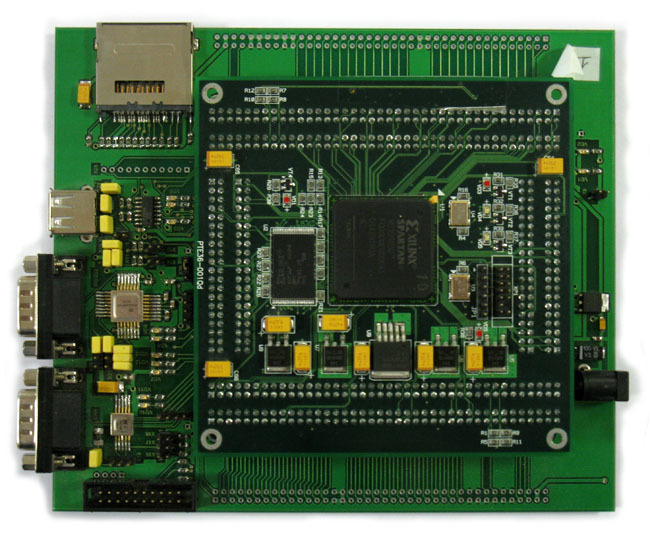

Pour le nouveau microcontrôleur 32 bits, il était évident qu'un million de vannes pourraient ne pas suffire. Par conséquent, une nouvelle carte mère basée sur Xilinx Spartan3-5000 a été développée, grâce à laquelle 5 millions de portes sont devenues disponibles. Le prix de la carte était d'environ 500 $ et pendant longtemps, cette carte est devenue la principale pour le prototypage de nouveaux développements. Sur cette base, non seulement des microcontrôleurs ont été testés, mais aussi divers microcircuits spécialisés. Le microcontrôleur conçu en FPGA fonctionnait déjà à une fréquence réduite de 20 MHz, bien que dans le silicium il fonctionnait à des fréquences de 100 MHz et même 150 MHz.Le prototype du microcontrôleur 32 bits: Le prototype de la carte vidéo (malheureusement le projet n'est pas allé en direct, mais la RTL terminée attend dans les coulisses):

Le prototype de la carte vidéo (malheureusement le projet n'est pas allé en direct, mais la RTL terminée attend dans les coulisses): Le prototype du commutateur Ethernet 4 voies avec émetteurs-récepteurs intégrés:

Le prototype du commutateur Ethernet 4 voies avec émetteurs-récepteurs intégrés:

2010 année

Lors du développement d'un microcontrôleur dual-core (RISC 32 bits + DSP 16 bits), nous avons finalement atteint le niveau alors que 5 millions n'étaient déjà pas suffisants. Mais l'implémentation en FPGA de différentes configurations tronquées du futur microcircuit a permis de tester son fonctionnement. Par exemple, ils ont vendu deux cœurs (RISC + DSP) avec un ensemble tronqué de périphériques ou un cœur (RISC), mais toute la périphérie.année 2012

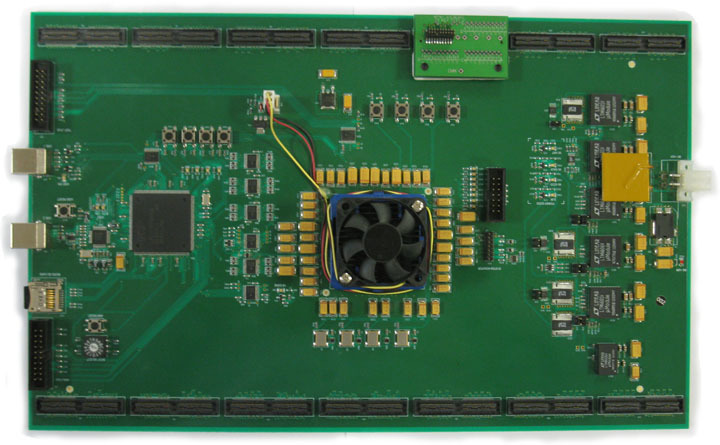

Le nouveau projet nécessitait une nouvelle carte, car la quantité de mémoire interne requise pour le nouveau cœur DSP 32 bits dépassait déjà la capacité disponible dans le plus grand FPGA Spartan. J'ai dû passer à des FPGA plus chers et complexes. Le temps du projet était limité et a décidé de trouver une solution toute faite. Le choix s'est porté sur la carte d'INREVIUM avec le plus grand à l'époque FPGA Xilinx Virtex-6 XC6VLX760. Et bien que le nombre de portes équivalentes ait augmenté à seulement 8 millions, mais la quantité de mémoire de bloc intégrée est passée de 2 Mbit à 25 Mbit.Le choix a également très probablement déterminé que le coût des frais était préservé sur le site du bureau de représentation allemand dans le cache de Google, et nous savions qu'il en coûterait 18 000 $ avant de signer un accord de non-divulgation. Et avec le coût d'une seule puce FPGA de 15 000 $, cela a éliminé toutes les questions sur le développement de votre propre carte. Les cartes série pour de si grands FPGA coûtent généralement autant que les FPGA eux-mêmes ou sont légèrement plus chères.L'achat de la carte a également apporté beaucoup de connaissances intéressantes, par exemple, notre distributeur local était convaincu que cette carte coûte 40 000 $, frais de port compris, et en général, elle risque beaucoup avec un prépaiement de 100% de notre part. En fin de compte, 3 de ces cartes ont été achetées sans intermédiaires, et maintenant elles sont utilisées pour prototyper nos processeurs DSP.

Et bien que le nombre de portes équivalentes ait augmenté à seulement 8 millions, mais la quantité de mémoire de bloc intégrée est passée de 2 Mbit à 25 Mbit.Le choix a également très probablement déterminé que le coût des frais était préservé sur le site du bureau de représentation allemand dans le cache de Google, et nous savions qu'il en coûterait 18 000 $ avant de signer un accord de non-divulgation. Et avec le coût d'une seule puce FPGA de 15 000 $, cela a éliminé toutes les questions sur le développement de votre propre carte. Les cartes série pour de si grands FPGA coûtent généralement autant que les FPGA eux-mêmes ou sont légèrement plus chères.L'achat de la carte a également apporté beaucoup de connaissances intéressantes, par exemple, notre distributeur local était convaincu que cette carte coûte 40 000 $, frais de port compris, et en général, elle risque beaucoup avec un prépaiement de 100% de notre part. En fin de compte, 3 de ces cartes ont été achetées sans intermédiaires, et maintenant elles sont utilisées pour prototyper nos processeurs DSP.année 2013

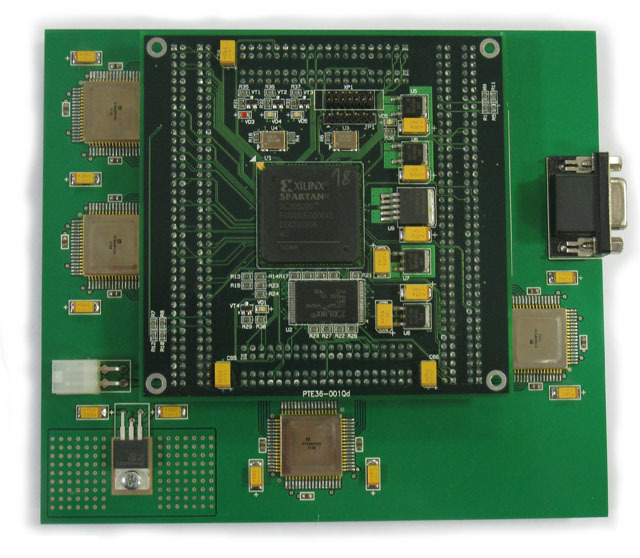

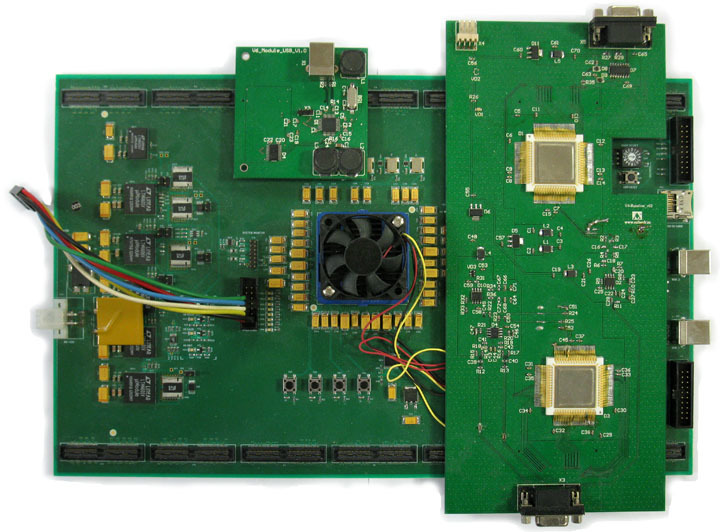

Pour le nouveau microcontrôleur spécialisé 32 bits, il a été décidé d'essayer de créer votre propre carte. Premièrement, les développeurs de modules sur FPGA devraient développer et ne pas avoir peur d'utiliser des microcircuits qui sont plus chers que leurs voitures personnelles, et deuxièmement, l'un des distributeurs avait plusieurs Virtex-6 XC6VLX550T en stock et il les a offerts à un rabais important. Le FPGA LX550T est un pas plus petit que le LX760 (environ 30% de valves en moins), mais le prix final des cartes, compte tenu du développement, n'était que d'environ 8 000 $. 6 planches ont été assemblées. Nous n'avions pas prévu de les distribuer aux clients, mais organisé pour que les développeurs y accèdent via Internet. Le conseil d'administration a mis en œuvre de nombreuses solutions intéressantes. Par exemple, les fichiers du micrologiciel ont été chargés sur la carte comme sur un périphérique MassStorage dans une carte SD spéciale, puis ils ont été chargés à partir de celle-ci dans le FPGA.Au total, la carte peut avoir jusqu'à 10 firmwares différents, et grâce à un programme de gestion spécial, vous pouvez choisir celui à utiliser pour le moment. Également mis en œuvre diverses protections "contre le fou", afin de ne pas brûler accidentellement une puce coûteuse. Tout cela vous permet de travailler avec ces cartes à distance, en toute sécurité et de leur faire confiance même aux étudiants. Le MK conçu en FPGA fonctionnait à une fréquence de 40 MHz.La carte elle-même (prototype d'un microcontrôleur dual-core 32 bits spécialisé ): Prototype d'une puce spécialisée pour les capteurs de conversion angle-code:

spécialisé ): Prototype d'une puce spécialisée pour les capteurs de conversion angle-code: Malheureusement, cette carte a plusieurs inconvénients: de mauvais connecteurs sont sélectionnés pour connecter des modules supplémentaires, mais c'est la moitié du problème, nous avons oublié de corriger trous près des connecteurs, et les modules ne sont en fait maintenus que dans les connecteurs. Afin d'accéder à certains contrôles de la carte principale, vous devez déterminer les modules d'extension.

Malheureusement, cette carte a plusieurs inconvénients: de mauvais connecteurs sont sélectionnés pour connecter des modules supplémentaires, mais c'est la moitié du problème, nous avons oublié de corriger trous près des connecteurs, et les modules ne sont en fait maintenus que dans les connecteurs. Afin d'accéder à certains contrôles de la carte principale, vous devez déterminer les modules d'extension.Expérience domestique

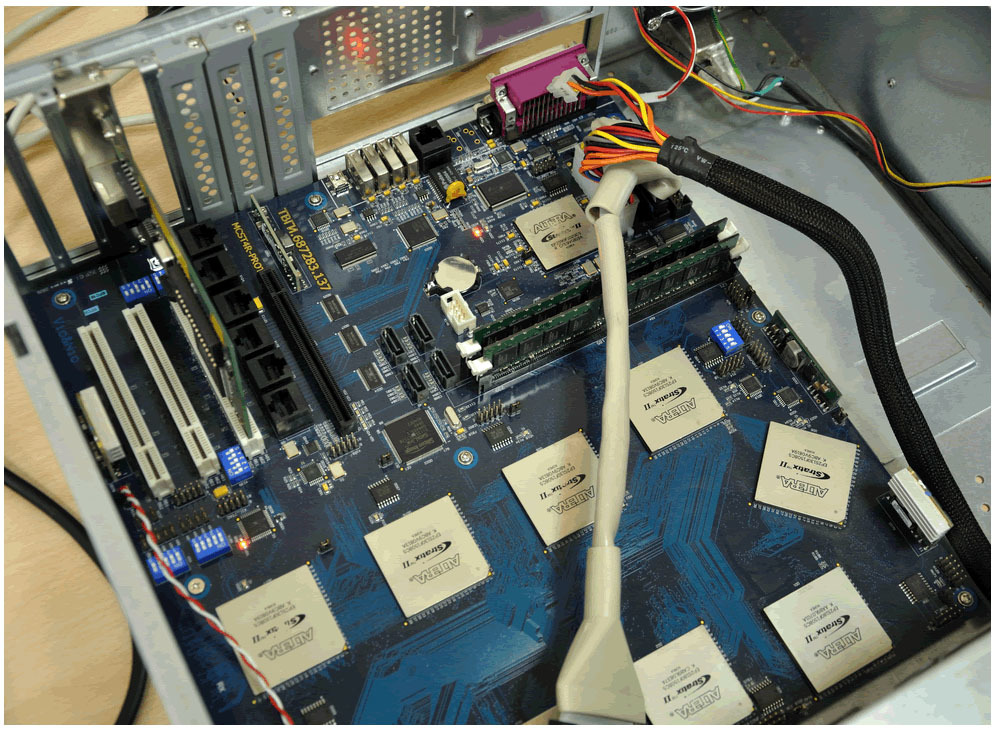

Mais qu'en est-il des autres développeurs de puces personnalisées? Par exemple, le MCST lors du prototypage du VLSI 1891VM6Ya (R-1000, un processeur à quatre cœurs avec une architecture SPARC v.9 64 bits) a utilisé une carte spécialisée avec 10 FPGA Altera Stratix II (4 x EP2S180 + 5 x EP2S130 + 1 x EP2S90). Le volume total des portes logiques du système peut être estimé à 20 millions de dollars. Aujourd'hui, une puce EP2S180 coûte environ 8 000 $. Ainsi, le coût des seules puces FPGA du prototype dépasse 50 000 $.Pour le prototypage du processeur Elbrus-4C +, 21 microcircuits Altera Stratix IV EP4SE820 étaient déjà nécessaires et avec un volume total de 100 millions de valves (bien que le MCST lui-même cite un chiffre de 750 millions) et coûte environ 200000 $. Dans ce cas, la fréquence de travail du prototype est de 9 MHz.

Aujourd'hui, une puce EP2S180 coûte environ 8 000 $. Ainsi, le coût des seules puces FPGA du prototype dépasse 50 000 $.Pour le prototypage du processeur Elbrus-4C +, 21 microcircuits Altera Stratix IV EP4SE820 étaient déjà nécessaires et avec un volume total de 100 millions de valves (bien que le MCST lui-même cite un chiffre de 750 millions) et coûte environ 200000 $. Dans ce cas, la fréquence de travail du prototype est de 9 MHz.Expérience étrangère

Désormais, des solutions spécialisées pour le prototypage FPGA sont proposées par des sociétés spécialisées dans le développement d'outils de CAO pour la microélectronique, bien que des modules adaptés au prototypage soient également disponibles dans d'autres sociétés. Intel et IBM ont des prototypes FPGA, mais leurs caractéristiques ne sont pas annoncées et elles ne sont connues d'un large cercle que lorsque le prototype est déjà obsolète.Cadence propose une plate-forme spéciale de prototypage rapide basée sur le FPGA Altera Stratix-4 EP4SE820. Dans la configuration minimale, la plate-forme se compose de deux (avec un volume total de 10 millions de valves), et au maximum de six FPGA (avec un volume allant jusqu'à 30 millions de valves). Le prix d'une puce EP4SE820 aujourd'hui est de ~ 10 000 $. Le nouveau système de Cadence est appelé Protium et est basé sur le Xilinx Virtex-7 XC7V2000T et vous permet de mettre en œuvre de 25 millions de FPGA à 100 millions de valves à huit. Le coût d'une puce XC7V2000T est maintenant d'environ 20 000 $. Ceux. Protium entièrement équipé coûtera au moins 160 000 $.En plus des outils de développement, Aldec propose également une plateforme de prototypage FPGA de HES-7.

Le nouveau système de Cadence est appelé Protium et est basé sur le Xilinx Virtex-7 XC7V2000T et vous permet de mettre en œuvre de 25 millions de FPGA à 100 millions de valves à huit. Le coût d'une puce XC7V2000T est maintenant d'environ 20 000 $. Ceux. Protium entièrement équipé coûtera au moins 160 000 $.En plus des outils de développement, Aldec propose également une plateforme de prototypage FPGA de HES-7. Jusqu'à six Xilinx Virtex-7 XC7V2000T ou UltraSacle XCVU440 se trouvent sur une même carte. Dans le cas de l'implémentation du module basé sur le FPGA UltraSacle XCVU440, le nombre total de portes atteint 158 millions. En utilisant une carte supplémentaire, vous pouvez assembler 24 puces FPGA en un seul module et obtenir 633 millions de portes. Le coût d'une puce XCVU440 est maintenant de 49 000 $. Et le coût total maximum de tous les FPGA dépasse 1M $.Synopsys a probablement la plus grande expérience dans le développement de plateformes de prototypage FPGA. Leurs premiers modèles étaient basés sur le FPGA Virtex-6 (HAPS-60), puis Virtex-7 (HAPS-70). Leur dernier développement, HAPS-80, dans un seul module contient de un à quatre FPGA Xilinx UltraScale XCVU440.

Jusqu'à six Xilinx Virtex-7 XC7V2000T ou UltraSacle XCVU440 se trouvent sur une même carte. Dans le cas de l'implémentation du module basé sur le FPGA UltraSacle XCVU440, le nombre total de portes atteint 158 millions. En utilisant une carte supplémentaire, vous pouvez assembler 24 puces FPGA en un seul module et obtenir 633 millions de portes. Le coût d'une puce XCVU440 est maintenant de 49 000 $. Et le coût total maximum de tous les FPGA dépasse 1M $.Synopsys a probablement la plus grande expérience dans le développement de plateformes de prototypage FPGA. Leurs premiers modèles étaient basés sur le FPGA Virtex-6 (HAPS-60), puis Virtex-7 (HAPS-70). Leur dernier développement, HAPS-80, dans un seul module contient de un à quatre FPGA Xilinx UltraScale XCVU440. Les modules prêts à l'emploi peuvent être combinés en un seul rack. Et dans ce cas, le volume total est un record de 1,6 milliard de soupapes.Lorsque vous utilisez un FPGA, la fréquence maximale peut atteindre 300 MHz, lorsque vous utilisez les voisins dans un module à 100 MHz, lorsque vous utilisez plusieurs modules, la fréquence est réduite à 30 MHz.

Les modules prêts à l'emploi peuvent être combinés en un seul rack. Et dans ce cas, le volume total est un record de 1,6 milliard de soupapes.Lorsque vous utilisez un FPGA, la fréquence maximale peut atteindre 300 MHz, lorsque vous utilisez les voisins dans un module à 100 MHz, lorsque vous utilisez plusieurs modules, la fréquence est réduite à 30 MHz. Ainsi, disposant d'environ 3,5 M $ pour l'achat de FPGA, vous pouvez assembler une plateforme adaptée au prototypage d'Intel Xeon E7. Eh bien, ou attendez 20 ans, lorsque les FPGA d'un tel volume tomberont à quelques centaines de dollars.

Ainsi, disposant d'environ 3,5 M $ pour l'achat de FPGA, vous pouvez assembler une plateforme adaptée au prototypage d'Intel Xeon E7. Eh bien, ou attendez 20 ans, lorsque les FPGA d'un tel volume tomberont à quelques centaines de dollars. Source: https://habr.com/ru/post/fr387653/

All Articles