Distribution d'éléphants: cartes FPGA pour des projets éducatifs avec MIPSfpga

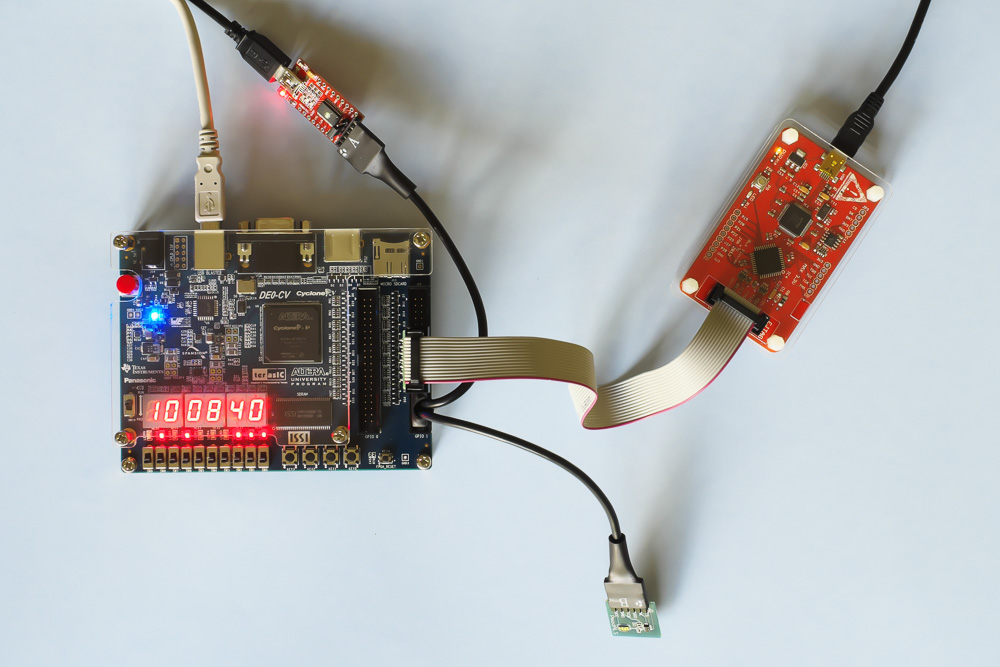

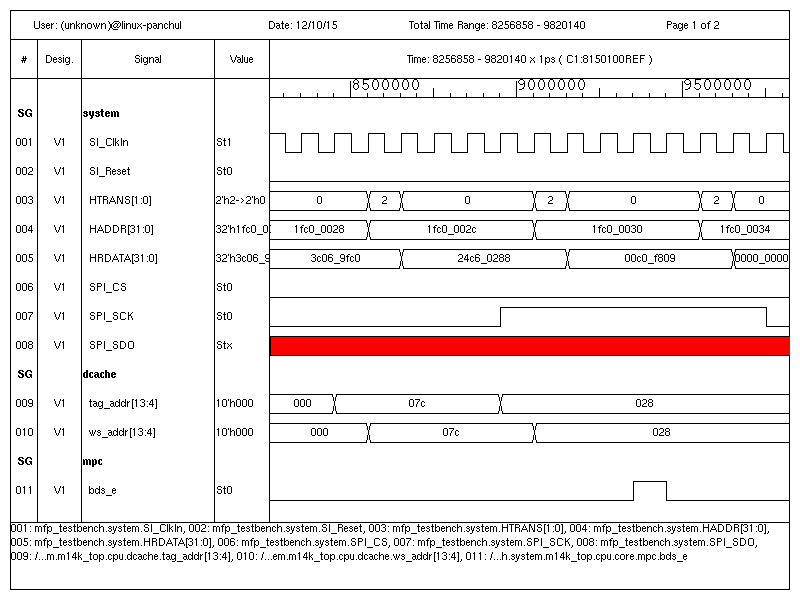

Il y a un mois, des séminaires sur MIPSfpga ( 1 , 2 , 3 , 4 ) ont eu lieu dans les universités russes , et un homme du NIIIS nommé Anton Pavlov a écrit une note sur ses propres améliorations MIPSfpga "MIPSfpga: en dehors du canon" . Depuis que les professeurs ont rencontré positivement le nouveau produit pour enseigner aux étudiants en électronique en général, l'idée est apparue pour aider à démarrer avec les tableaux, et en même temps pour plusieurs personnes et organisations.En particulier, en l'honneur du nouvel an, je coopère avec Vitaliy Kravchenko de univeda.ruNous prévoyons une petite distribution d'éléphants, c'est-à-dire des cartes Terasic DE0-CV gratuites avec FPGA Altera Cyclone V. Vous pouvez donc répéter l'acte d'Anton Pavlov. Étant donné que cette distribution particulière ne se fait pas avec l'argent d'Imagination Technologies, pas avec l'argent d'Altera et non avec l'argent du Centre scientifique et de production d'Elvis, mais avec l'argent de bienfaiteurs privés, y compris moi personnellement, les éléphants seront distribués avec des conditions plutôt spécifiques décrites ci-dessous. Les objectifs de l'événement: 1. Augmenter le niveau d'implication des universités russes dans la recherche mondiale dans le domaine de la microarchitecture des processeurs, la conception de SoC et de systèmes multicœurs hétérogènes 2. Augmenter le nombre de textes russes sur MIPS Insider afin que les visiteurs de l'industrie électronique internationale et du monde universitaire commencent à comprendre que les Russes arrivent 3. Créer, au nom de la communauté, un tas de matériel de formation autour de MIPSfpga, qui pourrait être utilisé par les enseignants des universités russes et les professeurs d'université dans d'autres pays - États-Unis, Japon, Chine, etc.Termes:1. Il est souhaitable que le bénéficiaire soit un enseignant, un étudiant diplômé ou un étudiant d'une université russe.2. Il est souhaitable que cette université ne soit pas l'Université d'État de Moscou, l'Institut de physique et de technologie de Moscou, le MEPhI, le MIET et l'ITMO, qui peuvent recevoir ces frais d'autres sources.3. Il est très souhaitable qu'avant de recevoir le tableau, un ami créatif m'envoie non seulement une description du projet, mais aussi un code en Verilog ou VHDL, C et / ou assembleur, avec lequel il simule un prototype d'un futur système synthétisé dans un environnement ModelSim ou Icarus. Les chronogrammes sont également les bienvenus.4. Le code du projet une fois terminé est téléchargé sur http://github.com/MIPSfpga - voir par exemple http://github.com/MIPSfpga/mipsfpga-plus5. Il est également décrit dans la section Wiki:5.1. Que contient chaque fichier5.2. Hiérarchie des modules matériels5.3. Comment simuler - instructions avec captures d'écran5.4. Diagrammes de temps de simulation5.5. Comment synthétiser - instructions avec captures d'écran5.6. Résultats de synthèse - taille et fréquence maximale5.7. Description de la partie logicielle5.8. Photos du FPGA de travail6. Ceci est présenté sur http://geektimes.ru sous la forme de l'article7. La même chose est présentée sur http://silicon-russia.com8. La même chose est présentée sur http://community.imgtec.com / forums / cat / mips-insider / mipsfpga9. La langue (6), (7), (8) peut être le russe ou l'anglais10. Si vous ne faites rien avec la planche pendant un mois, elle vous est retirée et transférée à quelqu'un d'autre11. Si nous (I et UnivEDA) organisons des événements en Russie tels que des compétitions ou des entraînements, nous vous facturerons également des frais prendre le tempsExemples de projets avec cartes:1. Interface entre MIPSfpga et capteurs avec interfaces SPI, I2C, UART et autres. Capteurs d'humidité, de température, de son, de compas, de télémètre, etc.2. L'interface entre MIPSfpga et externe par rapport à la mémoire FPGA - SDRAM, DDR, etc. (dans les exemples actuels, la mémoire système est construite à partir de la mémoire de bloc à l'intérieur du FPGA)3. L'interface entre MIPSfpga et les appareils plus grands est un écran VGA, une souris, un clavier, un joystick.4. Visualisation du cache en exécutant le processeur à une fréquence de 1 horloge par seconde et en émettant des signaux liés à la transaction (requête, échec, etc.).5. Visualisation du fonctionnement du convoyeur et des dispositifs arithmétiques en démarrant le processeur avec une fréquence de 1 horloge par seconde et en émettant des signaux de commande du convoyeur, etc.6. Ajout de commandes au processeur à l'aide de l'interface CorExtend / User Defined Instructions (UDI). Un exemple est les commandes de cryptage spéciales.7. Travaux de laboratoire avec une démonstration du fonctionnement des interruptions dans différents modes et un gestionnaire d'interruptions.8. Ponts entre le bus AHB-Lite et d'autres bus - AXI, APB, OCP, Wishbone, PLB, etc.9. Systèmes multiprocesseurs sans la cohérence des caches de premier niveau et (pour les plus avancés) avec des caches cohérents et l'implémentation de protocoles comme MESI.10. Portage vers MIPSfpga divers programmes et systèmes d'exploitation - du simple RTOS aux différentes variantes Linux (MIPSfpga prend en charge TLB MMU).Veuillez envoyer vos suggestions à yuri.panchul@imgtec.com avec une copie de yuri@panchul.com

3. Créer, au nom de la communauté, un tas de matériel de formation autour de MIPSfpga, qui pourrait être utilisé par les enseignants des universités russes et les professeurs d'université dans d'autres pays - États-Unis, Japon, Chine, etc.Termes:1. Il est souhaitable que le bénéficiaire soit un enseignant, un étudiant diplômé ou un étudiant d'une université russe.2. Il est souhaitable que cette université ne soit pas l'Université d'État de Moscou, l'Institut de physique et de technologie de Moscou, le MEPhI, le MIET et l'ITMO, qui peuvent recevoir ces frais d'autres sources.3. Il est très souhaitable qu'avant de recevoir le tableau, un ami créatif m'envoie non seulement une description du projet, mais aussi un code en Verilog ou VHDL, C et / ou assembleur, avec lequel il simule un prototype d'un futur système synthétisé dans un environnement ModelSim ou Icarus. Les chronogrammes sont également les bienvenus.4. Le code du projet une fois terminé est téléchargé sur http://github.com/MIPSfpga - voir par exemple http://github.com/MIPSfpga/mipsfpga-plus5. Il est également décrit dans la section Wiki:5.1. Que contient chaque fichier5.2. Hiérarchie des modules matériels5.3. Comment simuler - instructions avec captures d'écran5.4. Diagrammes de temps de simulation5.5. Comment synthétiser - instructions avec captures d'écran5.6. Résultats de synthèse - taille et fréquence maximale5.7. Description de la partie logicielle5.8. Photos du FPGA de travail6. Ceci est présenté sur http://geektimes.ru sous la forme de l'article7. La même chose est présentée sur http://silicon-russia.com8. La même chose est présentée sur http://community.imgtec.com / forums / cat / mips-insider / mipsfpga9. La langue (6), (7), (8) peut être le russe ou l'anglais10. Si vous ne faites rien avec la planche pendant un mois, elle vous est retirée et transférée à quelqu'un d'autre11. Si nous (I et UnivEDA) organisons des événements en Russie tels que des compétitions ou des entraînements, nous vous facturerons également des frais prendre le tempsExemples de projets avec cartes:1. Interface entre MIPSfpga et capteurs avec interfaces SPI, I2C, UART et autres. Capteurs d'humidité, de température, de son, de compas, de télémètre, etc.2. L'interface entre MIPSfpga et externe par rapport à la mémoire FPGA - SDRAM, DDR, etc. (dans les exemples actuels, la mémoire système est construite à partir de la mémoire de bloc à l'intérieur du FPGA)3. L'interface entre MIPSfpga et les appareils plus grands est un écran VGA, une souris, un clavier, un joystick.4. Visualisation du cache en exécutant le processeur à une fréquence de 1 horloge par seconde et en émettant des signaux liés à la transaction (requête, échec, etc.).5. Visualisation du fonctionnement du convoyeur et des dispositifs arithmétiques en démarrant le processeur avec une fréquence de 1 horloge par seconde et en émettant des signaux de commande du convoyeur, etc.6. Ajout de commandes au processeur à l'aide de l'interface CorExtend / User Defined Instructions (UDI). Un exemple est les commandes de cryptage spéciales.7. Travaux de laboratoire avec une démonstration du fonctionnement des interruptions dans différents modes et un gestionnaire d'interruptions.8. Ponts entre le bus AHB-Lite et d'autres bus - AXI, APB, OCP, Wishbone, PLB, etc.9. Systèmes multiprocesseurs sans la cohérence des caches de premier niveau et (pour les plus avancés) avec des caches cohérents et l'implémentation de protocoles comme MESI.10. Portage vers MIPSfpga divers programmes et systèmes d'exploitation - du simple RTOS aux différentes variantes Linux (MIPSfpga prend en charge TLB MMU).Veuillez envoyer vos suggestions à yuri.panchul@imgtec.com avec une copie de yuri@panchul.com

Source: https://habr.com/ru/post/fr387803/

All Articles