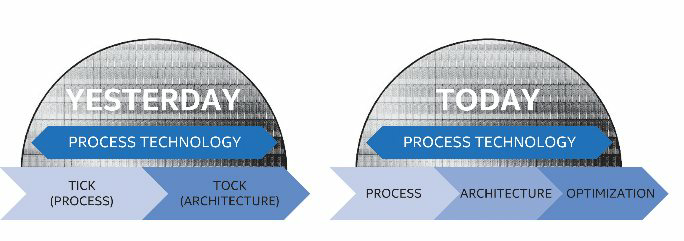

Intel abandonne sa stratégie du tick-to-tack

Maintenant, les processeurs feront le cycle "processus-architecture-optimisation"

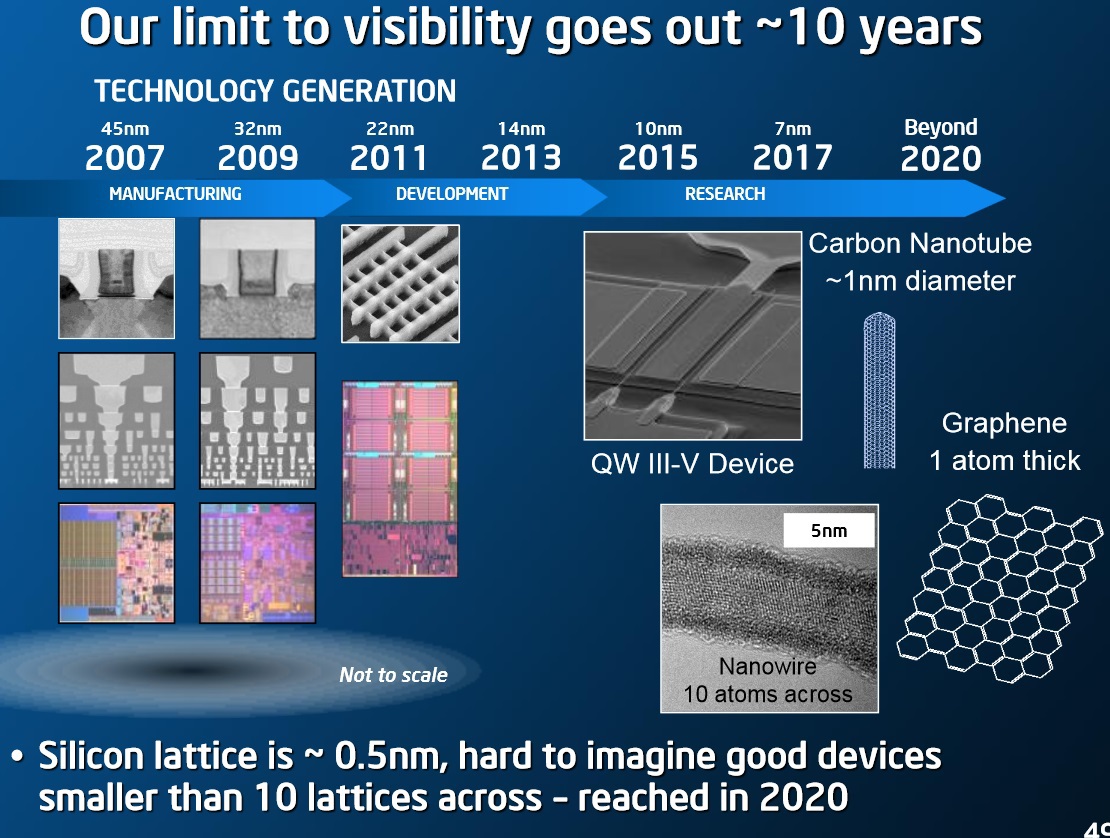

En tant qu'entreprise publique avec plus de 10 millions de dollars d'actifs détenus par plus de 500 actionnaires, Intel a fourni à la Securities and Exchange Commission des États-Unis un rapport annuel 10-K . Le document de 150 pages présente un intérêt particulier à la page 14, sur laquelle Intel reconnaît qu'il abandonne la stratégie du tick-to-tack au profit du nouveau concept d'optimisation d'architecture de processus.Tick-Tock est un modèle de développement de microprocesseur qu'Intel utilise depuis 2007. À certains intervalles, la technologie vous permet de réduire la taille des éléments sur la carte, ce qui réduit la consommation d'énergie et permet d'installer un plus grand nombre de transistors sur une puce de même taille. S'il est possible d'adapter plus d'éléments, alors une nouvelle microarchitecture est possible: de nouvelles commandes sont ajoutées, la logique de travail s'améliore, le nombre d'éléments différents augmente.La stratégie du tick-to-tack divise les deux processus. Au fil du "tick", les transistors deviennent plus petits. Il y a des changements dans la microarchitecture, mais ils sont insignifiants. «So» signifie la création d'une nouvelle microarchitecture, c'est-à-dire de grands changements, parfois fondamentaux, afin de réaliser de gros gains de productivité.Intel déplace ces étapes depuis près de 10 ans. Chacun d'eux prend d'un an à un an et demi. Mais récemment, il est devenu de plus en plus difficile de réduire le processus de fabrication. Lors du passage de 22 à 14 nanomètres , des retards de 6 à 9 mois sont apparus. À ce moment, il était nécessaire d'augmenter le pourcentage de sortie de puces réalisables des plaquettes à un niveau acceptable au coût. La loi de Moore, qui décrit le doublement du nombre de transistors sur une puce tous les 24 mois, doit être ajustée.À l'avenir, il est prévu de passer à 10, puis à 7 et 5 nanomètres. Atteindre de nouvelles frontières signifie l' utilisation possible de la lithographie dans les ultraviolets profonds, les quadruples motifs auto-alignés (SAQP), le rejet du silicium en faveur des semi-conducteurs III-V, les nanotubes de carbone et le graphène.

En tant qu'entreprise publique avec plus de 10 millions de dollars d'actifs détenus par plus de 500 actionnaires, Intel a fourni à la Securities and Exchange Commission des États-Unis un rapport annuel 10-K . Le document de 150 pages présente un intérêt particulier à la page 14, sur laquelle Intel reconnaît qu'il abandonne la stratégie du tick-to-tack au profit du nouveau concept d'optimisation d'architecture de processus.Tick-Tock est un modèle de développement de microprocesseur qu'Intel utilise depuis 2007. À certains intervalles, la technologie vous permet de réduire la taille des éléments sur la carte, ce qui réduit la consommation d'énergie et permet d'installer un plus grand nombre de transistors sur une puce de même taille. S'il est possible d'adapter plus d'éléments, alors une nouvelle microarchitecture est possible: de nouvelles commandes sont ajoutées, la logique de travail s'améliore, le nombre d'éléments différents augmente.La stratégie du tick-to-tack divise les deux processus. Au fil du "tick", les transistors deviennent plus petits. Il y a des changements dans la microarchitecture, mais ils sont insignifiants. «So» signifie la création d'une nouvelle microarchitecture, c'est-à-dire de grands changements, parfois fondamentaux, afin de réaliser de gros gains de productivité.Intel déplace ces étapes depuis près de 10 ans. Chacun d'eux prend d'un an à un an et demi. Mais récemment, il est devenu de plus en plus difficile de réduire le processus de fabrication. Lors du passage de 22 à 14 nanomètres , des retards de 6 à 9 mois sont apparus. À ce moment, il était nécessaire d'augmenter le pourcentage de sortie de puces réalisables des plaquettes à un niveau acceptable au coût. La loi de Moore, qui décrit le doublement du nombre de transistors sur une puce tous les 24 mois, doit être ajustée.À l'avenir, il est prévu de passer à 10, puis à 7 et 5 nanomètres. Atteindre de nouvelles frontières signifie l' utilisation possible de la lithographie dans les ultraviolets profonds, les quadruples motifs auto-alignés (SAQP), le rejet du silicium en faveur des semi-conducteurs III-V, les nanotubes de carbone et le graphène. Diapositive de la présentation d'il y a un an .Un document pour la Securities and Exchange Commission traite du cours de développement global d'Intel. La société explique que la durée totale d'utilisation du produit pour la technologie de processus actuelle sera augmentée à 14 nanomètres et l'avenir à 10 nm. Mais le rythme du marché des lancements de nouveaux produits se poursuivra. Comment cela sera-t-il réalisé? Intel donne l'image, qui dans ce post est postée avant le kat. Dans ce document, «tick-tock» est appelé la technologie d'hier, et le cycle en trois étapes «processus-architecture-optimisation» (PAO) est déclaré la réalité actuelle.Broadwell, le disciple du Haswell 22 nm, a aidé à calculer 14 nanomètres. La microarchitecture actuelle d'Intel est Skylake, la sixième génération de Core, la technologie de processus «so» de 14 nm. Son suiveur, Kaby Lake, sera également de 14 nm, mais offrira «des améliorations de performances significatives par rapport à la famille de processeurs Core de sixième génération».Atteindre 10 nanomètres peut être aidé par la collaboration mentionnée dans le document avec ASML pour l'étude de la photolithographie en ultraviolet profond, notamment celle applicable aux plaques de diamètres 300 et 450 millimètres. Intel garde toujours la tête: 14 nm ont été introduits en août 2014, Samsung et TSMC se sont relevés plus tard.Le lac Kaby de 14 nm devrait être libéré cette année. Selon les plans actuels, les produits de la microarchitecture Cannonlake 10 nanomètres devraient apparaître en 2017. Dans le cycle en trois étapes, il est facile de voir des avantages évidents pour l'utilisateur final: la même carte mère peut convenir à des produits de deux générations ou plus.

Diapositive de la présentation d'il y a un an .Un document pour la Securities and Exchange Commission traite du cours de développement global d'Intel. La société explique que la durée totale d'utilisation du produit pour la technologie de processus actuelle sera augmentée à 14 nanomètres et l'avenir à 10 nm. Mais le rythme du marché des lancements de nouveaux produits se poursuivra. Comment cela sera-t-il réalisé? Intel donne l'image, qui dans ce post est postée avant le kat. Dans ce document, «tick-tock» est appelé la technologie d'hier, et le cycle en trois étapes «processus-architecture-optimisation» (PAO) est déclaré la réalité actuelle.Broadwell, le disciple du Haswell 22 nm, a aidé à calculer 14 nanomètres. La microarchitecture actuelle d'Intel est Skylake, la sixième génération de Core, la technologie de processus «so» de 14 nm. Son suiveur, Kaby Lake, sera également de 14 nm, mais offrira «des améliorations de performances significatives par rapport à la famille de processeurs Core de sixième génération».Atteindre 10 nanomètres peut être aidé par la collaboration mentionnée dans le document avec ASML pour l'étude de la photolithographie en ultraviolet profond, notamment celle applicable aux plaques de diamètres 300 et 450 millimètres. Intel garde toujours la tête: 14 nm ont été introduits en août 2014, Samsung et TSMC se sont relevés plus tard.Le lac Kaby de 14 nm devrait être libéré cette année. Selon les plans actuels, les produits de la microarchitecture Cannonlake 10 nanomètres devraient apparaître en 2017. Dans le cycle en trois étapes, il est facile de voir des avantages évidents pour l'utilisateur final: la même carte mère peut convenir à des produits de deux générations ou plus.Source: https://habr.com/ru/post/fr392041/

All Articles