L'histoire du développement des processeurs: la fin des années 80 - le début des années 2000

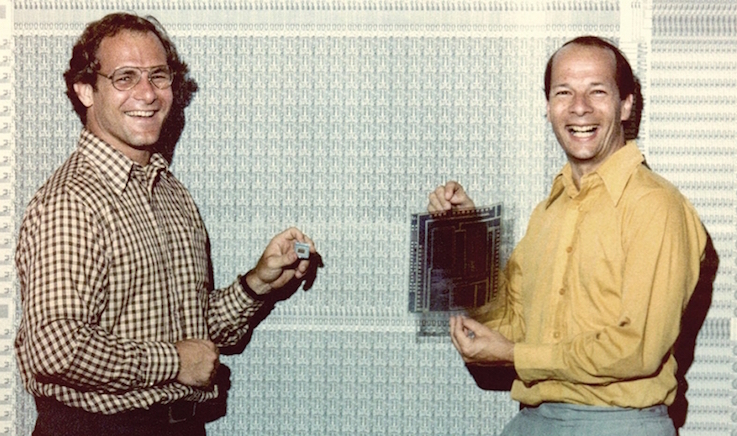

Poursuivant le thème du premier article, l'histoire de l'évolution des processeurs de la fin du XXe siècle au début du XXIe siècle.De nombreux processeurs des années 80 utilisaient l'architecture CISC (Complex Instruction Set Computing). Les puces étaient assez complexes et coûteuses, ainsi que pas suffisamment productives. Il fallait moderniser la production et augmenter le nombre de transistors.Architecture RISCEn 1980, le projet RISC Berkeley a été lancé, dirigé par les ingénieurs américains David Patterson et Carlo Sequin. RISC (ordinateur à jeu d'instructions restreint) - architecture de processeur à vitesse accrue grâce à des instructions simplifiées. Chefs de projet Berkeley RISC - David Patterson et Carlo SequinAprès plusieurs années de travail fructueux, plusieurs échantillons de processeurs avec un jeu d'instructions réduit sont apparus sur le marché. Chaque instruction de la plateforme RISC était simple et exécutée en un seul cycle. Il existe également de nombreux registres à usage général. De plus, un pipeline avec des instructions simplifiées a été utilisé, ce qui a permis d'augmenter efficacement la fréquence d'horloge.RISC I a été publié en 1982 et contenait plus de 44 420 transistors. Il n'avait que 32 instructions et travaillait à une fréquence de 4 MHz. Le prochain RISC II comprenait 40 760 transistors, utilisait 39 instructions et était plus rapide. Processeur

Chefs de projet Berkeley RISC - David Patterson et Carlo SequinAprès plusieurs années de travail fructueux, plusieurs échantillons de processeurs avec un jeu d'instructions réduit sont apparus sur le marché. Chaque instruction de la plateforme RISC était simple et exécutée en un seul cycle. Il existe également de nombreux registres à usage général. De plus, un pipeline avec des instructions simplifiées a été utilisé, ce qui a permis d'augmenter efficacement la fréquence d'horloge.RISC I a été publié en 1982 et contenait plus de 44 420 transistors. Il n'avait que 32 instructions et travaillait à une fréquence de 4 MHz. Le prochain RISC II comprenait 40 760 transistors, utilisait 39 instructions et était plus rapide. Processeur RISC IIProcesseurs MIPS: R2000, R3000, R4000 et R4400L'architecture des processeurs MIPS (Microprocessor without Interlocked Pipeline Stages) prévoyait la présence d'unités auxiliaires dans le cristal. MIPS a utilisé un convoyeur allongé.En 1984, un groupe de chercheurs dirigé par le scientifique américain John Hennessey a fondé une entreprise qui conçoit des dispositifs microélectroniques. MIPS possède une architecture de microprocesseur sous licence et des cœurs IP pour les appareils domestiques intelligents, les applications réseau et mobiles. En 1985, le premier produit de la société a été lancé - le R2000 32 bits, qui en 1988 a été finalisé dans le R3000. Le modèle mis à jour prend en charge le multitraitement, le cache d'instructions et le cache de données. Le processeur a trouvé une application dans les postes de travail de la série SG de différentes sociétés. Le R3000 est également devenu la base de la console de jeu Sony PlayStation.

RISC IIProcesseurs MIPS: R2000, R3000, R4000 et R4400L'architecture des processeurs MIPS (Microprocessor without Interlocked Pipeline Stages) prévoyait la présence d'unités auxiliaires dans le cristal. MIPS a utilisé un convoyeur allongé.En 1984, un groupe de chercheurs dirigé par le scientifique américain John Hennessey a fondé une entreprise qui conçoit des dispositifs microélectroniques. MIPS possède une architecture de microprocesseur sous licence et des cœurs IP pour les appareils domestiques intelligents, les applications réseau et mobiles. En 1985, le premier produit de la société a été lancé - le R2000 32 bits, qui en 1988 a été finalisé dans le R3000. Le modèle mis à jour prend en charge le multitraitement, le cache d'instructions et le cache de données. Le processeur a trouvé une application dans les postes de travail de la série SG de différentes sociétés. Le R3000 est également devenu la base de la console de jeu Sony PlayStation. Processeur R3000En 1991, la nouvelle génération de la gamme R4000 est lancée. Ce processeur avait une architecture 64 bits, un coprocesseur intégré et fonctionnait à une fréquence d'horloge de 100 MHz. Le cache interne était de 16 Ko (8 Ko d'instructions de cache et 8 Ko de données de cache).Un an plus tard, une version modifiée du processeur - R4400 - est sortie. Dans ce modèle, le cache est passé à 32 Ko (16 Ko de commandes de cache et 16 Ko de données de cache). Le processeur pourrait fonctionner à une fréquence de 100 MHz à 250 MHz.Processeurs MIPS: R8000 et R10000En 1994, le premier processeur avec une implémentation superscalaire de l'architecture MIPS, le R8000, est apparu. La capacité du cache de données était de 16 Ko. Ce processeur avait une bande passante d'accès aux données élevée (jusqu'à 1,2 Gb / s) en combinaison avec une vitesse de fonctionnement élevée. La fréquence a atteint 75 MHz - 90 MHz. Six circuits ont été utilisés: un dispositif pour les instructions entières, pour les instructions à virgule flottante, trois descripteurs de cache RAM secondaire et un contrôleur de cache ASIC.

Processeur R3000En 1991, la nouvelle génération de la gamme R4000 est lancée. Ce processeur avait une architecture 64 bits, un coprocesseur intégré et fonctionnait à une fréquence d'horloge de 100 MHz. Le cache interne était de 16 Ko (8 Ko d'instructions de cache et 8 Ko de données de cache).Un an plus tard, une version modifiée du processeur - R4400 - est sortie. Dans ce modèle, le cache est passé à 32 Ko (16 Ko de commandes de cache et 16 Ko de données de cache). Le processeur pourrait fonctionner à une fréquence de 100 MHz à 250 MHz.Processeurs MIPS: R8000 et R10000En 1994, le premier processeur avec une implémentation superscalaire de l'architecture MIPS, le R8000, est apparu. La capacité du cache de données était de 16 Ko. Ce processeur avait une bande passante d'accès aux données élevée (jusqu'à 1,2 Gb / s) en combinaison avec une vitesse de fonctionnement élevée. La fréquence a atteint 75 MHz - 90 MHz. Six circuits ont été utilisés: un dispositif pour les instructions entières, pour les instructions à virgule flottante, trois descripteurs de cache RAM secondaire et un contrôleur de cache ASIC. Processeur R8000En 1996, une version révisée a été publiée - R10000. Le processeur comprenait 32 Ko du cache principal de données et d'instructions. Le CPU fonctionnait à une fréquence de 150 MHz - 250 MHz.À la fin des années 90, MIPS a commencé à vendre des licences pour les architectures MIPS32 et MIPS64 32 bits et 64 bits.Processeurs SPARCSun Microsystems, qui a développé l'architecture évolutive SPARC (Scalable Processor ARChitecture), a rejoint les rangs des processeurs. Le premier processeur du même nom est sorti à la fin des années 80 et s'appelait SPARC V7. Sa fréquence a atteint 14,28 MHz - 40 MHz.En 1992, la prochaine version 32 bits appelée SPARC V8 est apparue, sur la base de laquelle le processeur microSPARC a été créé. La fréquence d'horloge était de 40 MHz - 50 MHz.Texas Instruments, Fujitsu, Philips et d'autres ont collaboré à l'architecture SPARC V9 de nouvelle génération avec Sun Microsystems. La plate-forme s'est étendue à 64 bits et était superscalaire avec un pipeline à 9 étages. SPARC V9 prévoyait l'utilisation de la mémoire cache de premier niveau, divisée en instructions et données (chacune d'une capacité de 16 Ko), ainsi que le deuxième niveau d'une capacité de 512 Ko - 1024 Ko. Processeur

Processeur R8000En 1996, une version révisée a été publiée - R10000. Le processeur comprenait 32 Ko du cache principal de données et d'instructions. Le CPU fonctionnait à une fréquence de 150 MHz - 250 MHz.À la fin des années 90, MIPS a commencé à vendre des licences pour les architectures MIPS32 et MIPS64 32 bits et 64 bits.Processeurs SPARCSun Microsystems, qui a développé l'architecture évolutive SPARC (Scalable Processor ARChitecture), a rejoint les rangs des processeurs. Le premier processeur du même nom est sorti à la fin des années 80 et s'appelait SPARC V7. Sa fréquence a atteint 14,28 MHz - 40 MHz.En 1992, la prochaine version 32 bits appelée SPARC V8 est apparue, sur la base de laquelle le processeur microSPARC a été créé. La fréquence d'horloge était de 40 MHz - 50 MHz.Texas Instruments, Fujitsu, Philips et d'autres ont collaboré à l'architecture SPARC V9 de nouvelle génération avec Sun Microsystems. La plate-forme s'est étendue à 64 bits et était superscalaire avec un pipeline à 9 étages. SPARC V9 prévoyait l'utilisation de la mémoire cache de premier niveau, divisée en instructions et données (chacune d'une capacité de 16 Ko), ainsi que le deuxième niveau d'une capacité de 512 Ko - 1024 Ko. Processeur UltraSPARC IIIProcesseurs StrongARMEn 1995, un projet a été lancé pour développer la famille de microprocesseurs StrongARM qui implémentait le jeu d'instructions ARM V4. Ces processeurs étaient une architecture scalaire classique avec un pipeline à 5 étages, comprenant des unités de contrôle de la mémoire et prenant en charge un cache d'instructions et de données de 16 Ko chacune.

UltraSPARC IIIProcesseurs StrongARMEn 1995, un projet a été lancé pour développer la famille de microprocesseurs StrongARM qui implémentait le jeu d'instructions ARM V4. Ces processeurs étaient une architecture scalaire classique avec un pipeline à 5 étages, comprenant des unités de contrôle de la mémoire et prenant en charge un cache d'instructions et de données de 16 Ko chacune. StrongARM SA-110Et déjà en 1996, le premier processeur basé sur StrongARM - SA-110 est sorti. Il a travaillé à des fréquences d'horloge de 100 MHz, 160 MHz ou 200 MHz.Les modèles SA-1100, SA-1110 et SA-1500 sont également entrés sur le marché.

StrongARM SA-110Et déjà en 1996, le premier processeur basé sur StrongARM - SA-110 est sorti. Il a travaillé à des fréquences d'horloge de 100 MHz, 160 MHz ou 200 MHz.Les modèles SA-1100, SA-1110 et SA-1500 sont également entrés sur le marché. Processeur SA-110 dans les processeurs Apple MessagePad 2000POWER, POWER2 et PowerPCEn 1985, IBM a commencé à développer l'architecture RISC de nouvelle génération dans le cadre du projet America. Le développement du processeur POWER (Performance Optimization With Enhanced RISC) et l'ensemble d'instructions pour celui-ci a duré 5 ans. Il était très productif, mais comprenait 11 puces différentes. Et par conséquent, en 1992, une autre version de processeur a été lancée qui tient dans une puce.

Processeur SA-110 dans les processeurs Apple MessagePad 2000POWER, POWER2 et PowerPCEn 1985, IBM a commencé à développer l'architecture RISC de nouvelle génération dans le cadre du projet America. Le développement du processeur POWER (Performance Optimization With Enhanced RISC) et l'ensemble d'instructions pour celui-ci a duré 5 ans. Il était très productif, mais comprenait 11 puces différentes. Et par conséquent, en 1992, une autre version de processeur a été lancée qui tient dans une puce. Chipset POWEREn 1991, l'architecture PowerPC (en abrégé PPC) a été développée par IBM, Apple et Motorola Alliance. Il se composait d'un ensemble de fonctions de base de la plate-forme POWER, et a également pris en charge le travail dans deux modes et était rétrocompatible avec le mode de fonctionnement 32 bits pour la version 64 bits. Le but principal était les ordinateurs personnels.Le processeur PowerPC 601 était utilisé sur le Macintosh.

Chipset POWEREn 1991, l'architecture PowerPC (en abrégé PPC) a été développée par IBM, Apple et Motorola Alliance. Il se composait d'un ensemble de fonctions de base de la plate-forme POWER, et a également pris en charge le travail dans deux modes et était rétrocompatible avec le mode de fonctionnement 32 bits pour la version 64 bits. Le but principal était les ordinateurs personnels.Le processeur PowerPC 601 était utilisé sur le Macintosh. Processeur PowerPCEn 1993, POWER2 a été introduit avec un ensemble d'instructions étendu. La vitesse d'horloge du processeur variait de 55 MHz à 71,5 MHz, et le cache de données et d'instructions était de 128-256 Kb et 32 Kb. Les microcircuits du processeur (il y en avait 8) contenaient 23 millions de transistors, et ils ont été fabriqués en utilisant la technologie CMOS de 0,72 micromètre.En 1998, IBM a publié la troisième série de processeurs POWER3 64 bits entièrement conformes à la norme PowerPC.Entre 2001 et 2010, des modèles POWER4 (jusqu'à huit commandes exécutées en parallèle), POWER5 et POWER6 double cœur et quatre à huit modèles POWER7 nucléaires ont été lancés.Processeurs Alpha 21064AEn 1992, Digital Equipment Corporation (DEC) a lancé le processeur Alpha 21064 (EV4). Il s'agissait d'un cristal superscalaire 64 bits avec une architecture en pipeline et une fréquence d'horloge de 100 MHz à 200 MHz. Fabriqué à l'aide d'une technologie de processus de 0,75 micron avec un bus de processeur 128 bits externe. Il y avait 16 Ko de cache (8 Ko de données et 8 Ko d'instructions).Le prochain modèle de la série était le processeur 21164 (EV5), sorti en 1995. Il possédait deux blocs entiers et comptait déjà trois niveaux de mémoire cache (deux dans le processeur, le troisième - externe). Le cache du premier niveau a été divisé en un cache de données et un cache d'instructions de 8 Ko chacun. La quantité de cache dans le deuxième niveau était de 96 Ko. La vitesse d'horloge du processeur allait de 266 MHz à 500 MHz.

Processeur PowerPCEn 1993, POWER2 a été introduit avec un ensemble d'instructions étendu. La vitesse d'horloge du processeur variait de 55 MHz à 71,5 MHz, et le cache de données et d'instructions était de 128-256 Kb et 32 Kb. Les microcircuits du processeur (il y en avait 8) contenaient 23 millions de transistors, et ils ont été fabriqués en utilisant la technologie CMOS de 0,72 micromètre.En 1998, IBM a publié la troisième série de processeurs POWER3 64 bits entièrement conformes à la norme PowerPC.Entre 2001 et 2010, des modèles POWER4 (jusqu'à huit commandes exécutées en parallèle), POWER5 et POWER6 double cœur et quatre à huit modèles POWER7 nucléaires ont été lancés.Processeurs Alpha 21064AEn 1992, Digital Equipment Corporation (DEC) a lancé le processeur Alpha 21064 (EV4). Il s'agissait d'un cristal superscalaire 64 bits avec une architecture en pipeline et une fréquence d'horloge de 100 MHz à 200 MHz. Fabriqué à l'aide d'une technologie de processus de 0,75 micron avec un bus de processeur 128 bits externe. Il y avait 16 Ko de cache (8 Ko de données et 8 Ko d'instructions).Le prochain modèle de la série était le processeur 21164 (EV5), sorti en 1995. Il possédait deux blocs entiers et comptait déjà trois niveaux de mémoire cache (deux dans le processeur, le troisième - externe). Le cache du premier niveau a été divisé en un cache de données et un cache d'instructions de 8 Ko chacun. La quantité de cache dans le deuxième niveau était de 96 Ko. La vitesse d'horloge du processeur allait de 266 MHz à 500 MHz. DEC Alpha AXP 21064En 1996, les processeurs Alpha 21264 (EV6) sont sortis avec 15,2 millions de transistors, fabriqués en utilisant la technologie de processus de 15,2 microns. Leur fréquence d'horloge allait de 450 MHz à 600 MHz. Les blocs entiers et les blocs de chargement / sauvegarde ont été combinés en un seul module Ebox, et les blocs à virgule flottante ont été combinés en un module Fbox. Le cache de premier niveau a conservé une allocation de mémoire pour les instructions et les données. Le volume de chaque pièce était de 64 Ko. La quantité de cache au deuxième niveau était de 2 Mo à 8 Mo.En 1999, DEC a été acheté par Compaq. En conséquence, la majeure partie de la production utilisant Alpha a été transférée à API NetWorks, Inc.Processeurs Intel P5 et P54CSelon la disposition de Vinod Dham, le processeur de cinquième génération, nommé P5, a été développé. En 1993, le CPU est entré en production sous le nom de Pentium.Les processeurs de base P5 ont été fabriqués à l'aide d'une technologie de traitement de 800 nanomètres utilisant la technologie bipolaire BiCMOS. Ils contenaient 3,1 millions de transistors. Pentium avait un bus de données 64 bits, une architecture superscalaire. Il y avait une mise en cache séparée du code du programme et des données. Le cache de premier niveau de 16 Ko a été utilisé, divisé en 2 segments (8 Ko pour les données et 8 Ko pour les instructions). Les premiers modèles étaient à des fréquences de 60 MHz - 66 MHz.

DEC Alpha AXP 21064En 1996, les processeurs Alpha 21264 (EV6) sont sortis avec 15,2 millions de transistors, fabriqués en utilisant la technologie de processus de 15,2 microns. Leur fréquence d'horloge allait de 450 MHz à 600 MHz. Les blocs entiers et les blocs de chargement / sauvegarde ont été combinés en un seul module Ebox, et les blocs à virgule flottante ont été combinés en un module Fbox. Le cache de premier niveau a conservé une allocation de mémoire pour les instructions et les données. Le volume de chaque pièce était de 64 Ko. La quantité de cache au deuxième niveau était de 2 Mo à 8 Mo.En 1999, DEC a été acheté par Compaq. En conséquence, la majeure partie de la production utilisant Alpha a été transférée à API NetWorks, Inc.Processeurs Intel P5 et P54CSelon la disposition de Vinod Dham, le processeur de cinquième génération, nommé P5, a été développé. En 1993, le CPU est entré en production sous le nom de Pentium.Les processeurs de base P5 ont été fabriqués à l'aide d'une technologie de traitement de 800 nanomètres utilisant la technologie bipolaire BiCMOS. Ils contenaient 3,1 millions de transistors. Pentium avait un bus de données 64 bits, une architecture superscalaire. Il y avait une mise en cache séparée du code du programme et des données. Le cache de premier niveau de 16 Ko a été utilisé, divisé en 2 segments (8 Ko pour les données et 8 Ko pour les instructions). Les premiers modèles étaient à des fréquences de 60 MHz - 66 MHz. Processeur Intel PentiumLa même année, Intel a lancé les processeurs P54C. La production de nouveaux processeurs a été transférée à une technologie de traitement de 0,6 micron. La vitesse du processeur était de 75 MHz, et depuis 1994 - 90 MHz et 100 MHz. Un an plus tard, l'architecture du P54C (P54CS) a été transférée à une technologie de traitement à 350 nm et la fréquence d'horloge a été augmentée à 200 MHz.En 1997, le P5 a reçu la dernière mise à jour - le P55C (Pentium MMX). La prise en charge du jeu d'instructions MMX (MultiMedia eXtension) est apparue. Le processeur se composait de 4,5 millions de transistors et est fabriqué à l'aide de la technologie CMOS avancée de 280 nanomètres. Le cache du premier niveau est passé à 32 Ko (16 Ko pour les données et 16 Ko pour les instructions). La fréquence du processeur a atteint 233 MHz.Processeurs AMD K5 et K6En 1995, AMD a sorti le processeur K5. L'architecture était un noyau RISC, mais elle fonctionnait avec des instructions CISC complexes. Les processeurs ont été fabriqués en utilisant une technologie de processus de 350 ou 500 nanomètres, avec 4,3 millions de transistors. Tous les K5 avaient cinq blocs entiers et un bloc à virgule flottante. Le cache d'instructions était de 16 Ko et les données étaient de 8 Ko. La vitesse d'horloge du processeur allait de 75 MHz à 133 MHz.

Processeur Intel PentiumLa même année, Intel a lancé les processeurs P54C. La production de nouveaux processeurs a été transférée à une technologie de traitement de 0,6 micron. La vitesse du processeur était de 75 MHz, et depuis 1994 - 90 MHz et 100 MHz. Un an plus tard, l'architecture du P54C (P54CS) a été transférée à une technologie de traitement à 350 nm et la fréquence d'horloge a été augmentée à 200 MHz.En 1997, le P5 a reçu la dernière mise à jour - le P55C (Pentium MMX). La prise en charge du jeu d'instructions MMX (MultiMedia eXtension) est apparue. Le processeur se composait de 4,5 millions de transistors et est fabriqué à l'aide de la technologie CMOS avancée de 280 nanomètres. Le cache du premier niveau est passé à 32 Ko (16 Ko pour les données et 16 Ko pour les instructions). La fréquence du processeur a atteint 233 MHz.Processeurs AMD K5 et K6En 1995, AMD a sorti le processeur K5. L'architecture était un noyau RISC, mais elle fonctionnait avec des instructions CISC complexes. Les processeurs ont été fabriqués en utilisant une technologie de processus de 350 ou 500 nanomètres, avec 4,3 millions de transistors. Tous les K5 avaient cinq blocs entiers et un bloc à virgule flottante. Le cache d'instructions était de 16 Ko et les données étaient de 8 Ko. La vitesse d'horloge du processeur allait de 75 MHz à 133 MHz. Processeur AMD K5Sous la marque K5, deux versions des processeurs SSA / 5 et 5k86 ont été produites. Le premier a fonctionné à des fréquences de 75 MHz à 100 MHz. Le processeur 5k86 fonctionnait à des fréquences de 90 MHz à 133 MHz.En 1997, la société a présenté le processeur K6, dont l'architecture était très différente de celle du K5. Les processeurs ont été fabriqués à l'aide d'une technologie de traitement de 350 nanomètres, comprenaient 8,8 millions de transistors, ont pris en charge un changement dans l'ordre des instructions, un ensemble d'instructions MMX et un bloc à virgule flottante. La surface cristalline était de 162 mm². Le cache du premier niveau totalisait 64 Ko (32 Ko de données et 32 Ko d'instructions). Le processeur fonctionnait à une fréquence de 166 MHz, 200 MHz et 233 MHz. La fréquence du bus système était de 66 MHz.En 1998, AMD a sorti des puces avec une architecture K6-2 améliorée, avec 9,3 millions de transistors fabriqués en utilisant une technologie de processus de 250 nanomètres. La fréquence maximale des puces était de 550 MHz.

Processeur AMD K5Sous la marque K5, deux versions des processeurs SSA / 5 et 5k86 ont été produites. Le premier a fonctionné à des fréquences de 75 MHz à 100 MHz. Le processeur 5k86 fonctionnait à des fréquences de 90 MHz à 133 MHz.En 1997, la société a présenté le processeur K6, dont l'architecture était très différente de celle du K5. Les processeurs ont été fabriqués à l'aide d'une technologie de traitement de 350 nanomètres, comprenaient 8,8 millions de transistors, ont pris en charge un changement dans l'ordre des instructions, un ensemble d'instructions MMX et un bloc à virgule flottante. La surface cristalline était de 162 mm². Le cache du premier niveau totalisait 64 Ko (32 Ko de données et 32 Ko d'instructions). Le processeur fonctionnait à une fréquence de 166 MHz, 200 MHz et 233 MHz. La fréquence du bus système était de 66 MHz.En 1998, AMD a sorti des puces avec une architecture K6-2 améliorée, avec 9,3 millions de transistors fabriqués en utilisant une technologie de processus de 250 nanomètres. La fréquence maximale des puces était de 550 MHz. Processeur AMD K6En 1999, la troisième génération est sortie - l'architecture K6-III. Le cristal a conservé toutes les fonctionnalités du K6-2, mais en même temps, un cache intégré du deuxième niveau d'une capacité de 256 Ko est apparu. Le volume du cache de premier niveau était de 64 Ko.Processeurs AMD K7Dans le même 1999, K6 a été remplacé par des processeurs K7. Ils ont été produits en utilisant la technologie 250 nm avec 22 millions de transistors. Le CPU avait une nouvelle unité entière (ALU). Le bus système EV6 assurait la transmission de données sur les deux fronts du signal d'horloge, ce qui permettait d'obtenir une fréquence effective de 200 MHz à une fréquence physique de 100 MHz. Le cache du premier niveau était de 128 Ko (64 Ko d'instructions et 64 Ko de données). Le cache de deuxième niveau a atteint 512 Ko.

Processeur AMD K6En 1999, la troisième génération est sortie - l'architecture K6-III. Le cristal a conservé toutes les fonctionnalités du K6-2, mais en même temps, un cache intégré du deuxième niveau d'une capacité de 256 Ko est apparu. Le volume du cache de premier niveau était de 64 Ko.Processeurs AMD K7Dans le même 1999, K6 a été remplacé par des processeurs K7. Ils ont été produits en utilisant la technologie 250 nm avec 22 millions de transistors. Le CPU avait une nouvelle unité entière (ALU). Le bus système EV6 assurait la transmission de données sur les deux fronts du signal d'horloge, ce qui permettait d'obtenir une fréquence effective de 200 MHz à une fréquence physique de 100 MHz. Le cache du premier niveau était de 128 Ko (64 Ko d'instructions et 64 Ko de données). Le cache de deuxième niveau a atteint 512 Ko. Processeur AMD K7Un peu plus tard, des cristaux basés sur le noyau d'Orion sont apparus. Ils ont été produits selon la technologie du procédé à 180 nm.La version du noyau Thunderbird a introduit des changements inhabituels dans les processeurs. Le cache du 2e niveau a été transféré directement au cœur du processeur et a fonctionné avec la même fréquence. Le cache avait une capacité effective de 384 Ko (128 Ko de cache au premier niveau et 256 Ko de cache au deuxième niveau). La fréquence d'horloge du bus système a augmenté - il fonctionne désormais avec une fréquence de 133 MHz.Processeurs Intel P6L'architecture P6 a remplacé le P5 en 1995. Le processeur était superscalaire et supportait les changements dans l'ordre des opérations. Les processeurs utilisaient un double bus indépendant, ce qui augmentait considérablement la bande passante mémoire.Dans le même 1995, les processeurs Pentium Pro de nouvelle génération ont été introduits. Les cristaux fonctionnaient à une fréquence de 150 MHz à 200 MHz, avaient 16 Ko de cache au premier niveau et jusqu'à 1 Mo de cache au deuxième niveau.

Processeur AMD K7Un peu plus tard, des cristaux basés sur le noyau d'Orion sont apparus. Ils ont été produits selon la technologie du procédé à 180 nm.La version du noyau Thunderbird a introduit des changements inhabituels dans les processeurs. Le cache du 2e niveau a été transféré directement au cœur du processeur et a fonctionné avec la même fréquence. Le cache avait une capacité effective de 384 Ko (128 Ko de cache au premier niveau et 256 Ko de cache au deuxième niveau). La fréquence d'horloge du bus système a augmenté - il fonctionne désormais avec une fréquence de 133 MHz.Processeurs Intel P6L'architecture P6 a remplacé le P5 en 1995. Le processeur était superscalaire et supportait les changements dans l'ordre des opérations. Les processeurs utilisaient un double bus indépendant, ce qui augmentait considérablement la bande passante mémoire.Dans le même 1995, les processeurs Pentium Pro de nouvelle génération ont été introduits. Les cristaux fonctionnaient à une fréquence de 150 MHz à 200 MHz, avaient 16 Ko de cache au premier niveau et jusqu'à 1 Mo de cache au deuxième niveau. Processeur Intel Pentium ProEn 1999, les premiers processeurs Pentium III ont été introduits. Ils étaient basés sur une nouvelle génération du noyau P6 appelé Katmai, qui étaient des versions modifiées de Deschutes. La prise en charge des instructions SSE a été ajoutée au noyau et le mécanisme de travail avec la mémoire a été amélioré. La fréquence d'horloge des processeurs Katmai a atteint 600 MHz.En 2000, les premiers processeurs Pentium 4 avec un cœur Willamette ont été lancés. La fréquence effective du bus système était de 400 MHz (fréquence physique - 100 MHz). Le cache du premier niveau a atteint un volume de 8 Ko et le cache du deuxième niveau a atteint 256 Ko.Le noyau suivant de la ligne était Northwood (2002). Les processeurs contenaient 55 millions de transistors et ont été fabriqués en utilisant la nouvelle technologie CMOS 130 nm avec des composés de cuivre. La fréquence du bus système était de 400 MHz, 533 MHz ou 800 MHz.

Processeur Intel Pentium ProEn 1999, les premiers processeurs Pentium III ont été introduits. Ils étaient basés sur une nouvelle génération du noyau P6 appelé Katmai, qui étaient des versions modifiées de Deschutes. La prise en charge des instructions SSE a été ajoutée au noyau et le mécanisme de travail avec la mémoire a été amélioré. La fréquence d'horloge des processeurs Katmai a atteint 600 MHz.En 2000, les premiers processeurs Pentium 4 avec un cœur Willamette ont été lancés. La fréquence effective du bus système était de 400 MHz (fréquence physique - 100 MHz). Le cache du premier niveau a atteint un volume de 8 Ko et le cache du deuxième niveau a atteint 256 Ko.Le noyau suivant de la ligne était Northwood (2002). Les processeurs contenaient 55 millions de transistors et ont été fabriqués en utilisant la nouvelle technologie CMOS 130 nm avec des composés de cuivre. La fréquence du bus système était de 400 MHz, 533 MHz ou 800 MHz. Intel Pentium 4En 2004, la production de processeurs a de nouveau été transférée à des normes technologiques plus subtiles - 90 nm. Pentium 4 sur le noyau Prescott est sorti. Le cache des données de premier niveau a augmenté à 16 Ko, et le cache du deuxième niveau a atteint 1 Mo. La fréquence d'horloge était de 2,4 GHz - 3,8 GHz, la fréquence du bus système - 533 MHz ou 800 MHz.Le dernier cœur utilisé dans les processeurs Pentium 4 était le moulin à cèdre à cœur unique. Produit par une nouvelle technologie de processus - 65 nm. Il y avait quatre modèles: 631 (3 GHz), 641 (3,2 GHz), 651 (3,4 GHz), 661 (3,6 GHz).Processeurs Athlon 64 et Athlon 64 X2Fin 2003, AMD a lancé une nouvelle architecture K8 64 bits, basée sur la technologie de traitement à 130 nanomètres. Le processeur avait un contrôleur de mémoire intégré et un bus HyperTransport. Elle a travaillé à une fréquence de 200 MHz. Les nouveaux produits AMD sont appelés Athlon 64. Les processeurs prenaient en charge de nombreux jeux d'instructions, tels que MMX, 3DNow!, SSE, SSE2 et SSE3.

Intel Pentium 4En 2004, la production de processeurs a de nouveau été transférée à des normes technologiques plus subtiles - 90 nm. Pentium 4 sur le noyau Prescott est sorti. Le cache des données de premier niveau a augmenté à 16 Ko, et le cache du deuxième niveau a atteint 1 Mo. La fréquence d'horloge était de 2,4 GHz - 3,8 GHz, la fréquence du bus système - 533 MHz ou 800 MHz.Le dernier cœur utilisé dans les processeurs Pentium 4 était le moulin à cèdre à cœur unique. Produit par une nouvelle technologie de processus - 65 nm. Il y avait quatre modèles: 631 (3 GHz), 641 (3,2 GHz), 651 (3,4 GHz), 661 (3,6 GHz).Processeurs Athlon 64 et Athlon 64 X2Fin 2003, AMD a lancé une nouvelle architecture K8 64 bits, basée sur la technologie de traitement à 130 nanomètres. Le processeur avait un contrôleur de mémoire intégré et un bus HyperTransport. Elle a travaillé à une fréquence de 200 MHz. Les nouveaux produits AMD sont appelés Athlon 64. Les processeurs prenaient en charge de nombreux jeux d'instructions, tels que MMX, 3DNow!, SSE, SSE2 et SSE3. Processeur Athlon 64En 2005, les processeurs AMD appelés Athlon 64 X2 sont entrés sur le marché. Ce sont les premiers processeurs de bureau à double cœur. Le modèle était basé sur deux noyaux réalisés sur un seul cristal. Ils avaient un contrôleur de mémoire commun, un bus HyperTransport et une file d'attente de commandes.

Processeur Athlon 64En 2005, les processeurs AMD appelés Athlon 64 X2 sont entrés sur le marché. Ce sont les premiers processeurs de bureau à double cœur. Le modèle était basé sur deux noyaux réalisés sur un seul cristal. Ils avaient un contrôleur de mémoire commun, un bus HyperTransport et une file d'attente de commandes. Processeur Athlon 64 X2En 2005 et 2006, AMD a commercialisé quatre générations de puces double cœur: trois cœurs Manchester à 90 nm, Toledo et Windsor, ainsi qu'un cœur Brisbane à 65 nm. Les processeurs différaient par la taille du cache du deuxième niveau et la consommation d'énergie.Processeurs Intel Core Lesprocesseurs Pentium M offrent plus de performances que les processeurs de bureau basés sur la microarchitecture NetBurst. Et donc, leurs décisions architecturales sont devenues la base de la microarchitecture Core, qui a été publiée en 2006. Le premier processeur quad-core de bureau était l'Intel Core 2 Extreme QX6700 avec une fréquence d'horloge de 2,67 GHz et 8 Mo de cache au deuxième niveau.Le nom de code de la première génération de processeurs mobiles d'Intel était Yonah. Ils ont été fabriqués en utilisant la technologie de traitement à 65 nm, basée sur l'architecture Banias / Dothan Pentium M, avec l'ajout de la technologie de protection LaGrande. Le processeur peut traiter jusqu'à quatre instructions par cycle d'horloge. Core a repensé l'algorithme de traitement des instructions 128 bits SSE, SSE2 et SSE3. Si avant chaque commande était traitée en deux mesures, maintenant une seule mesure était requise pour l'opération.

Processeur Athlon 64 X2En 2005 et 2006, AMD a commercialisé quatre générations de puces double cœur: trois cœurs Manchester à 90 nm, Toledo et Windsor, ainsi qu'un cœur Brisbane à 65 nm. Les processeurs différaient par la taille du cache du deuxième niveau et la consommation d'énergie.Processeurs Intel Core Lesprocesseurs Pentium M offrent plus de performances que les processeurs de bureau basés sur la microarchitecture NetBurst. Et donc, leurs décisions architecturales sont devenues la base de la microarchitecture Core, qui a été publiée en 2006. Le premier processeur quad-core de bureau était l'Intel Core 2 Extreme QX6700 avec une fréquence d'horloge de 2,67 GHz et 8 Mo de cache au deuxième niveau.Le nom de code de la première génération de processeurs mobiles d'Intel était Yonah. Ils ont été fabriqués en utilisant la technologie de traitement à 65 nm, basée sur l'architecture Banias / Dothan Pentium M, avec l'ajout de la technologie de protection LaGrande. Le processeur peut traiter jusqu'à quatre instructions par cycle d'horloge. Core a repensé l'algorithme de traitement des instructions 128 bits SSE, SSE2 et SSE3. Si avant chaque commande était traitée en deux mesures, maintenant une seule mesure était requise pour l'opération. Intel Core 2 Extreme QX6700En 2007, la microarchitecture Penryn de 45 nm utilisant des portes métalliques Hi-k sans plomb est sortie. La technologie a été utilisée dans la famille de processeurs Intel Core 2 Duo. La prise en charge des instructions SSE4 a été ajoutée à l'architecture et la quantité maximale de cache dans le 2e niveau des processeurs double cœur est passée de 4 Mo à 6 Mo.

Intel Core 2 Extreme QX6700En 2007, la microarchitecture Penryn de 45 nm utilisant des portes métalliques Hi-k sans plomb est sortie. La technologie a été utilisée dans la famille de processeurs Intel Core 2 Duo. La prise en charge des instructions SSE4 a été ajoutée à l'architecture et la quantité maximale de cache dans le 2e niveau des processeurs double cœur est passée de 4 Mo à 6 Mo. Processeur AMD Phenom II X6En 2008, l'architecture de nouvelle génération, Nehalem, a été lancée. Les processeurs ont acquis un contrôleur de mémoire intégré qui prend en charge 2 ou 3 canaux de SDRAM DDR3 ou 4 canaux de FB-DIMM. Au lieu du bus FSB, un nouveau bus QPI est venu. Le cache de niveau 2 a été réduit à 256 Ko par cœur.

Processeur AMD Phenom II X6En 2008, l'architecture de nouvelle génération, Nehalem, a été lancée. Les processeurs ont acquis un contrôleur de mémoire intégré qui prend en charge 2 ou 3 canaux de SDRAM DDR3 ou 4 canaux de FB-DIMM. Au lieu du bus FSB, un nouveau bus QPI est venu. Le cache de niveau 2 a été réduit à 256 Ko par cœur. Intel Core i7Bientôt, Intel a déplacé l'architecture Nehalem vers une nouvelle technologie de processus 32 nm. Cette gamme de processeurs s'appelle Westmere.Le premier modèle de la nouvelle microarchitecture était Clarkdale, qui a deux cœurs et un cœur graphique intégré, produit par la technologie de traitement à 45 nm.Processeurs AMD K10 AMDa essayé de suivre Intel. En 2007, elle a lancé la génération d'architecture de microprocesseur x86 - K10. Quatre cœurs de processeur ont été combinés sur une seule puce. En plus du cache des 1er et 2e niveaux, les modèles K10 ont enfin obtenu L3 de 2 Mo. Le cache de données et d'instructions du 1er niveau était de 64 Ko chacun, et le cache du 2e niveau était de 512 Ko. Il existe également un support prometteur pour le contrôleur de mémoire DDR3. K10 a utilisé deux contrôleurs 64 bits. Chaque cœur de processeur avait un module à virgule flottante de 128 bits. En plus de cela, les nouveaux processeurs ont travaillé via l'interface HyperTransport 3.0.En 2007, les processeurs multi-cœurs Phenom d’AMD pour PC de bureau ont été lancés avec l’architecture K10. Les solutions basées sur K10 ont été produites en utilisant une technologie de traitement à 65 et 45 nm. Dans la nouvelle version de l'architecture (K10.5), le contrôleur de mémoire fonctionnait avec la mémoire DDR2 et DDR3.

Intel Core i7Bientôt, Intel a déplacé l'architecture Nehalem vers une nouvelle technologie de processus 32 nm. Cette gamme de processeurs s'appelle Westmere.Le premier modèle de la nouvelle microarchitecture était Clarkdale, qui a deux cœurs et un cœur graphique intégré, produit par la technologie de traitement à 45 nm.Processeurs AMD K10 AMDa essayé de suivre Intel. En 2007, elle a lancé la génération d'architecture de microprocesseur x86 - K10. Quatre cœurs de processeur ont été combinés sur une seule puce. En plus du cache des 1er et 2e niveaux, les modèles K10 ont enfin obtenu L3 de 2 Mo. Le cache de données et d'instructions du 1er niveau était de 64 Ko chacun, et le cache du 2e niveau était de 512 Ko. Il existe également un support prometteur pour le contrôleur de mémoire DDR3. K10 a utilisé deux contrôleurs 64 bits. Chaque cœur de processeur avait un module à virgule flottante de 128 bits. En plus de cela, les nouveaux processeurs ont travaillé via l'interface HyperTransport 3.0.En 2007, les processeurs multi-cœurs Phenom d’AMD pour PC de bureau ont été lancés avec l’architecture K10. Les solutions basées sur K10 ont été produites en utilisant une technologie de traitement à 65 et 45 nm. Dans la nouvelle version de l'architecture (K10.5), le contrôleur de mémoire fonctionnait avec la mémoire DDR2 et DDR3. Processeur AMD PhenomEn 2011, la nouvelle architecture Bulldozer a été lancée. Chaque module contenait deux cœurs avec son propre bloc entier et son cache de niveau 1. La mémoire cache prise en charge est le troisième niveau de 8 Mo, les bus HyperTransport 3.1, les technologies permettant d'augmenter la fréquence des cœurs Turbo Core de deuxième génération et les jeux d'instructions AVX, SSE 4.1, SSE 4.2, AES. Les processeurs Bulldozer étaient également dotés d'un contrôleur de mémoire DDR3 à double canal avec une fréquence effective de 1866 MHz.

Processeur AMD PhenomEn 2011, la nouvelle architecture Bulldozer a été lancée. Chaque module contenait deux cœurs avec son propre bloc entier et son cache de niveau 1. La mémoire cache prise en charge est le troisième niveau de 8 Mo, les bus HyperTransport 3.1, les technologies permettant d'augmenter la fréquence des cœurs Turbo Core de deuxième génération et les jeux d'instructions AVX, SSE 4.1, SSE 4.2, AES. Les processeurs Bulldozer étaient également dotés d'un contrôleur de mémoire DDR3 à double canal avec une fréquence effective de 1866 MHz. Processeur AMD BulldozerEn 2013, l'entreprise a introduit la prochaine génération de processeurs - Piledriver. Ce modèle était une architecture améliorée de Bulldozer. Les blocs de prédiction de branche ont été affinés et les performances du module de calcul à virgule flottante et entier ont augmenté, ainsi que la vitesse d'horloge.En parcourant l'histoire, vous pouvez retracer les étapes de développement des processeurs, les changements dans leur architecture, l'amélioration des technologies de développement et bien plus encore. Les processeurs modernes sont différents de ceux qui étaient sortis auparavant, mais ils ont en même temps des caractéristiques communes.

Processeur AMD BulldozerEn 2013, l'entreprise a introduit la prochaine génération de processeurs - Piledriver. Ce modèle était une architecture améliorée de Bulldozer. Les blocs de prédiction de branche ont été affinés et les performances du module de calcul à virgule flottante et entier ont augmenté, ainsi que la vitesse d'horloge.En parcourant l'histoire, vous pouvez retracer les étapes de développement des processeurs, les changements dans leur architecture, l'amélioration des technologies de développement et bien plus encore. Les processeurs modernes sont différents de ceux qui étaient sortis auparavant, mais ils ont en même temps des caractéristiques communes. Source: https://habr.com/ru/post/fr392175/

All Articles