Des chercheurs d'Intel et de l'Université de Caroline du Nord accélèrent l'échange de données entre les cœurs de processeur de 2 à 12 fois

La topologie de la septième génération de processeurs Intel Core (anciennement appelé Kaby Lake), qui sera disponible fin 2016. Photo: IntelUne équipe de chercheurs de l'Université de Caroline du Nord et Intel a développé la technologie CAF (Core to Core Communication Acceleration Framework) , qui peut accélérer considérablement l'échange de données entre les cœurs de processeur. En éliminant ce goulot d'étranglement, les fabricants pourront enfin augmenter le nombre de cœurs dans le processeur sans augmentation exponentielle du trafic de service entre eux.Dans la mise en œuvre de programmes parallèles, le plus difficile est d'assurer la bonne coordination des ressources partagées entre les processus. Sur les processeurs modernes, la synchronisation de l'interaction parallèle entre les cœurs est effectuée par deux méthodes: en utilisant le passage de messages et à travers la mémoire partagée.Dans le premier cas, un processus à thread unique est lancé sur chaque cœur, qui échange des données avec d'autres processus s'exécutant sur d'autres noyaux.Lors de l'interaction via la mémoire partagée sur chaque processeur d'un système multiprocesseur, le thread d'exécution qui appartient à un processus est lancé. Les flux échangent des données via une partie de la mémoire commune à ce processus. Le nombre de threads correspond au nombre de processeurs.Les chercheurs proposent de mettre en œuvre une telle coordination des ressourcesau niveau matériel . Dans le résumé des travaux scientifiques préparés, ils notent que «l'interaction par le biais de la mémoire partagée, de par sa nature, inclut des handicaps pour maintenir la cohérence et les ratés de cache, ce qui augmente considérablement les frais généraux et crée une grande quantité de trafic réseau [excédentaire».De nombreuses tâches importantes nécessitent un échange important de trafic entre les cœurs, de sorte qu'une augmentation significative des frais généraux a un impact énorme sur les performances. Cela s'applique également aux performances du pipeline de calcul, qui est largement utilisé dans les solutions logicielles pour le fonctionnement du parallélisme au niveau de la commande.L'accélération matérielle coordonne le travail des cœurs dans le calcul parallèle. La coordination du noyau matériel proposée est beaucoup plus efficace que toutes les méthodes de synchronisation logicielle actuellement utilisées.«Cette approche, que nous avons appelée CAF Framework for Accelerating Communication between Cores , améliore le transfert de données de 2 à 12 fois», a déclaré Yan Solihin, professeur de génie électrique et informatique à l'Université de Caroline du Nord et co-auteur de la recherche. "En d'autres termes, la vitesse d'exécution - du début à la fin - est au moins deux fois plus rapide."Dans le travail scientifique préparé, les auteurs ont effectué une analyse de la surcharge (trafic réseau excessif entre les cœurs), qui se produit lors de la synchronisation des calculs parallèles avec les méthodes logicielles existantes. Et ils ont proposé une solution alternative.Un élément clé du nouveau cadre est le module matériel de gestion de file d'attente QMD (Queue Management Device). Il est capable d'exécuter des fonctions de calcul simples et est connecté au matériel au sous-système de communication, c'est-à-dire à NoC (un réseau sur puce - un mini-Internet à l'intérieur du processeur ).

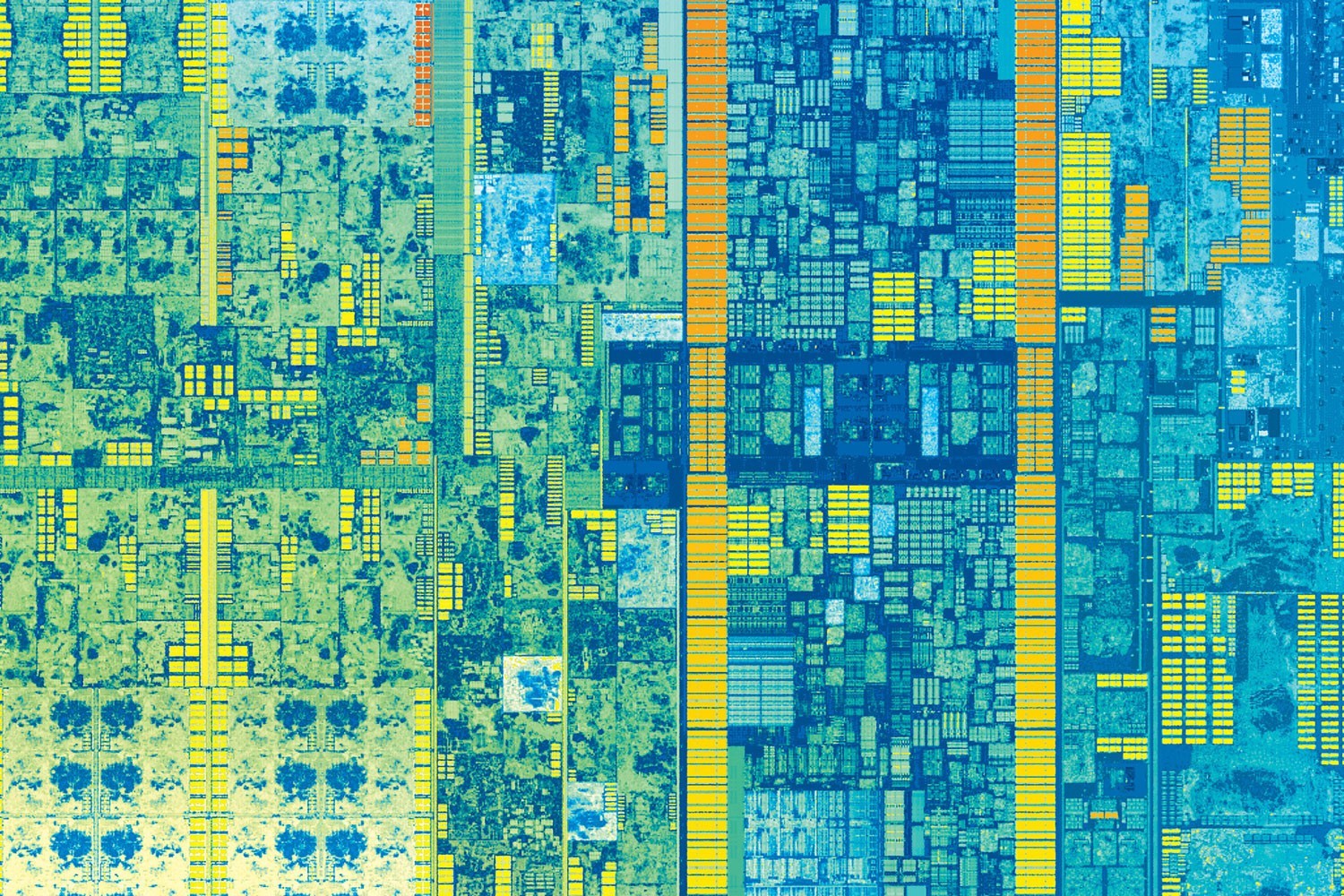

La topologie de la septième génération de processeurs Intel Core (anciennement appelé Kaby Lake), qui sera disponible fin 2016. Photo: IntelUne équipe de chercheurs de l'Université de Caroline du Nord et Intel a développé la technologie CAF (Core to Core Communication Acceleration Framework) , qui peut accélérer considérablement l'échange de données entre les cœurs de processeur. En éliminant ce goulot d'étranglement, les fabricants pourront enfin augmenter le nombre de cœurs dans le processeur sans augmentation exponentielle du trafic de service entre eux.Dans la mise en œuvre de programmes parallèles, le plus difficile est d'assurer la bonne coordination des ressources partagées entre les processus. Sur les processeurs modernes, la synchronisation de l'interaction parallèle entre les cœurs est effectuée par deux méthodes: en utilisant le passage de messages et à travers la mémoire partagée.Dans le premier cas, un processus à thread unique est lancé sur chaque cœur, qui échange des données avec d'autres processus s'exécutant sur d'autres noyaux.Lors de l'interaction via la mémoire partagée sur chaque processeur d'un système multiprocesseur, le thread d'exécution qui appartient à un processus est lancé. Les flux échangent des données via une partie de la mémoire commune à ce processus. Le nombre de threads correspond au nombre de processeurs.Les chercheurs proposent de mettre en œuvre une telle coordination des ressourcesau niveau matériel . Dans le résumé des travaux scientifiques préparés, ils notent que «l'interaction par le biais de la mémoire partagée, de par sa nature, inclut des handicaps pour maintenir la cohérence et les ratés de cache, ce qui augmente considérablement les frais généraux et crée une grande quantité de trafic réseau [excédentaire».De nombreuses tâches importantes nécessitent un échange important de trafic entre les cœurs, de sorte qu'une augmentation significative des frais généraux a un impact énorme sur les performances. Cela s'applique également aux performances du pipeline de calcul, qui est largement utilisé dans les solutions logicielles pour le fonctionnement du parallélisme au niveau de la commande.L'accélération matérielle coordonne le travail des cœurs dans le calcul parallèle. La coordination du noyau matériel proposée est beaucoup plus efficace que toutes les méthodes de synchronisation logicielle actuellement utilisées.«Cette approche, que nous avons appelée CAF Framework for Accelerating Communication between Cores , améliore le transfert de données de 2 à 12 fois», a déclaré Yan Solihin, professeur de génie électrique et informatique à l'Université de Caroline du Nord et co-auteur de la recherche. "En d'autres termes, la vitesse d'exécution - du début à la fin - est au moins deux fois plus rapide."Dans le travail scientifique préparé, les auteurs ont effectué une analyse de la surcharge (trafic réseau excessif entre les cœurs), qui se produit lors de la synchronisation des calculs parallèles avec les méthodes logicielles existantes. Et ils ont proposé une solution alternative.Un élément clé du nouveau cadre est le module matériel de gestion de file d'attente QMD (Queue Management Device). Il est capable d'exécuter des fonctions de calcul simples et est connecté au matériel au sous-système de communication, c'est-à-dire à NoC (un réseau sur puce - un mini-Internet à l'intérieur du processeur ). Illustration de l'article " Réseau sur puce - mini-Internet à l'intérieur du processeur "Le module QMD prend en charge la gestion de la file d'attente et la synchronisation de l'interaction parallèle des cœurs, sans aucune instruction logicielle supplémentaire sur les cœurs CPU. C'est comme un routeur matériel sur un réseau.Le développement futur est important à la lumière de l'augmentation constante des cœurs sur les processeurs modernes. Il s'agit d'un processus tout à fait naturel, car la vitesse d'horloge s'est presque arrêtée en raison de limitations physiques naturelles. Les fabricants n'ont d'autre choix que de paralléliser les calculs.Dans de telles conditions, la synchronisation de l'interaction parallèle entre les cœurs devient le goulot d'étranglement qui limite les performances du système. Avec un routage du trafic efficace entre les cœurs de processeur, vous pouvez continuer à faire évoluer l'architecture du processeur et créer des processeurs avec des dizaines ou des centaines de cœurs avec une mise à l'échelle des performances presque linéaire. Le routage efficace du trafic entre les cœurs est une technologie clé qui est nécessaire pour faire évoluer davantage l'architecture CPU multicœur.En plus d'accélérer à plusieurs reprises l'échange de données entre les cœurs tout en synchronisant le calcul parallèle, le module QMD peut être utile pour agréger les données de plusieurs cœurs. Les chercheurs pensent que cela accélérera le traitement de certaines opérations informatiques de base jusqu'à 15%.Le travail scientifique " CAF: Core to Core Communication Acceleration Framework " sera présenté lors de la 25ème conférence sur les architectures parallèles et les méthodes de compilation PACT '16 , qui se tiendra du 11 au 15 septembre 2016 à Haifa (Israël).Les inventeurs sont Yipeng Wang (Université de Caroline du Nord), Ren Wang, Andrew Herdrich et James Tsai (tous Intel Corp.), et l'auteur principal de l'article est le susmentionné Yan Solihin de l'Université de Caroline du Nord et de la US National Science Foundation.L'article a été inclus dans les Actes de la Conférence internationale 2016 sur les architectures parallèles et la compilation, p. 351-362, doi: 10.1145 / 2967938.2967954. La collection de rapports devrait être distribuée aux participants à la conférence et publiée sur Internet.

Illustration de l'article " Réseau sur puce - mini-Internet à l'intérieur du processeur "Le module QMD prend en charge la gestion de la file d'attente et la synchronisation de l'interaction parallèle des cœurs, sans aucune instruction logicielle supplémentaire sur les cœurs CPU. C'est comme un routeur matériel sur un réseau.Le développement futur est important à la lumière de l'augmentation constante des cœurs sur les processeurs modernes. Il s'agit d'un processus tout à fait naturel, car la vitesse d'horloge s'est presque arrêtée en raison de limitations physiques naturelles. Les fabricants n'ont d'autre choix que de paralléliser les calculs.Dans de telles conditions, la synchronisation de l'interaction parallèle entre les cœurs devient le goulot d'étranglement qui limite les performances du système. Avec un routage du trafic efficace entre les cœurs de processeur, vous pouvez continuer à faire évoluer l'architecture du processeur et créer des processeurs avec des dizaines ou des centaines de cœurs avec une mise à l'échelle des performances presque linéaire. Le routage efficace du trafic entre les cœurs est une technologie clé qui est nécessaire pour faire évoluer davantage l'architecture CPU multicœur.En plus d'accélérer à plusieurs reprises l'échange de données entre les cœurs tout en synchronisant le calcul parallèle, le module QMD peut être utile pour agréger les données de plusieurs cœurs. Les chercheurs pensent que cela accélérera le traitement de certaines opérations informatiques de base jusqu'à 15%.Le travail scientifique " CAF: Core to Core Communication Acceleration Framework " sera présenté lors de la 25ème conférence sur les architectures parallèles et les méthodes de compilation PACT '16 , qui se tiendra du 11 au 15 septembre 2016 à Haifa (Israël).Les inventeurs sont Yipeng Wang (Université de Caroline du Nord), Ren Wang, Andrew Herdrich et James Tsai (tous Intel Corp.), et l'auteur principal de l'article est le susmentionné Yan Solihin de l'Université de Caroline du Nord et de la US National Science Foundation.L'article a été inclus dans les Actes de la Conférence internationale 2016 sur les architectures parallèles et la compilation, p. 351-362, doi: 10.1145 / 2967938.2967954. La collection de rapports devrait être distribuée aux participants à la conférence et publiée sur Internet.Source: https://habr.com/ru/post/fr397275/

All Articles