Traduction de l'article de Ken Shirriff

Presque tous les smartphones utilisent un processeur basé sur la puce ARM1 introduite en 1985. Plus de dix milliards de cœurs ARM ont été utilisés dans une variété de gadgets, y compris l'un des plus gros échecs d'Apple, le Newton Pocket PC, et l'un de ses succès les plus retentissants, l'iPhone. Dans cet article, nous examinerons les éléments clés du processeur ARM1: nous décrirons la structure générale de la puce, examinerons comment les transistors sont disposés et comment ils fonctionnent, interagissent les uns avec les autres pour stocker et traiter les données, et également regarder la

simulation visuelle de ce microprocesseur et découvrir ce qui se passe à l'intérieur d'ARM1 pendant son fonctionnement.

Présentation de la puce ARM1

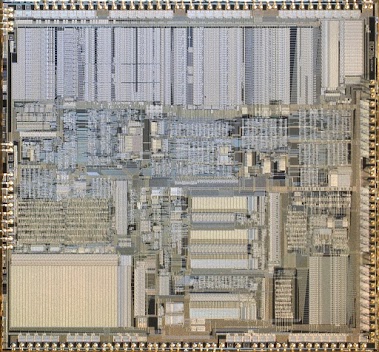

Le microprocesseur ARM1 est construit à partir de blocs fonctionnels, chacun ayant un objectif spécifique. Les registres stockent les données, ALU effectue une arithmétique simple, les décodeurs de commande déterminent comment exécuter chaque commande, etc. Comparé à la plupart des processeurs, le circuit à puce ARM1 est simple et chaque bloc fonctionnel est bien reconnaissable. À titre de comparaison, la disposition des puces, telles que 6502 ou Z-80, est optimisée manuellement pour éviter les taches vides sur le substrat. Dans ces processeurs, les blocs fonctionnels sont collés ensemble, ce qui les rend difficiles à comprendre.

Les principaux composants de la puce ARM1. Les contacts non marqués sont différents signaux de contrôle.

Les principaux composants de la puce ARM1. Les contacts non marqués sont différents signaux de contrôle.Vous voyez maintenant une image montrant les parties fonctionnelles les plus importantes du microprocesseur ARM. Le traitement réel a lieu au bas de la puce, ce qui fait référence au chemin de données. La puce traite 32 bits à la fois, donc sa structure comprend 32 couches horizontales: 31 bits à partir du haut, 0 bits à partir du bas. Plusieurs bus de données fonctionnent horizontalement pour communiquer divers composants de la puce. Sur l'image, vous pouvez voir une grande section de vingt-cinq registres. Le compteur d'instructions (quinzième registre) est à gauche de la section de registre, et le registre zéro est à droite. Neuf des vingt-cinq registres sont facultatifs, car il existe des copies de certains registres à utiliser dans la gestion des interruptions.

Tous les calculs ont lieu dans l'unité de logique arithmétique (ALU), qui est située à droite du bloc de registre. ALU effectue 16 opérations différentes: addition, addition avec transfert, soustraction, addition logique, etc. ALU utilise deux entrées 32 bits et sort 32 bits en sortie. Vous pouvez en savoir plus sur le dispositif ALU

ici . À droite de l'ALU se trouve un dispositif de décalage 32 bits. Ce grand composant effectue une opération de décalage cyclique d'entrée binaire. À gauche se trouvent les lignes d'adresse qui permettent d'accéder aux adresses en mémoire via des contacts d'adresse. Sur la droite se trouvent des lignes de données qui lisent et écrivent des valeurs de données en mémoire.

L'unité de contrôle est située sur le dessus. Les lignes de contrôle sont tracées verticalement de l'unité de contrôle vers le diagramme de ligne de données ci-dessous. Ces signaux sélectionnent les registres, indiquent à l'ALU quelle opération effectuer, etc. Le circuit de décodage d'instructions traite chaque instruction et génère les signaux de commande nécessaires. L'unité de décodage de registre traite les bits de sélection de registre dans l'instruction et génère des signaux de commande pour sélectionner les registres nécessaires.

Coordonnées

Les carrés autour de la surface externe de l'image sont les pads qui connectent le processeur au monde extérieur. La photo ci-dessous montre le boîtier à quatre-vingt-quatre broches du microprocesseur ARM1. Les contacts plaqués or sont connectés à des plots sur une puce de silicium à l'intérieur du boîtier.

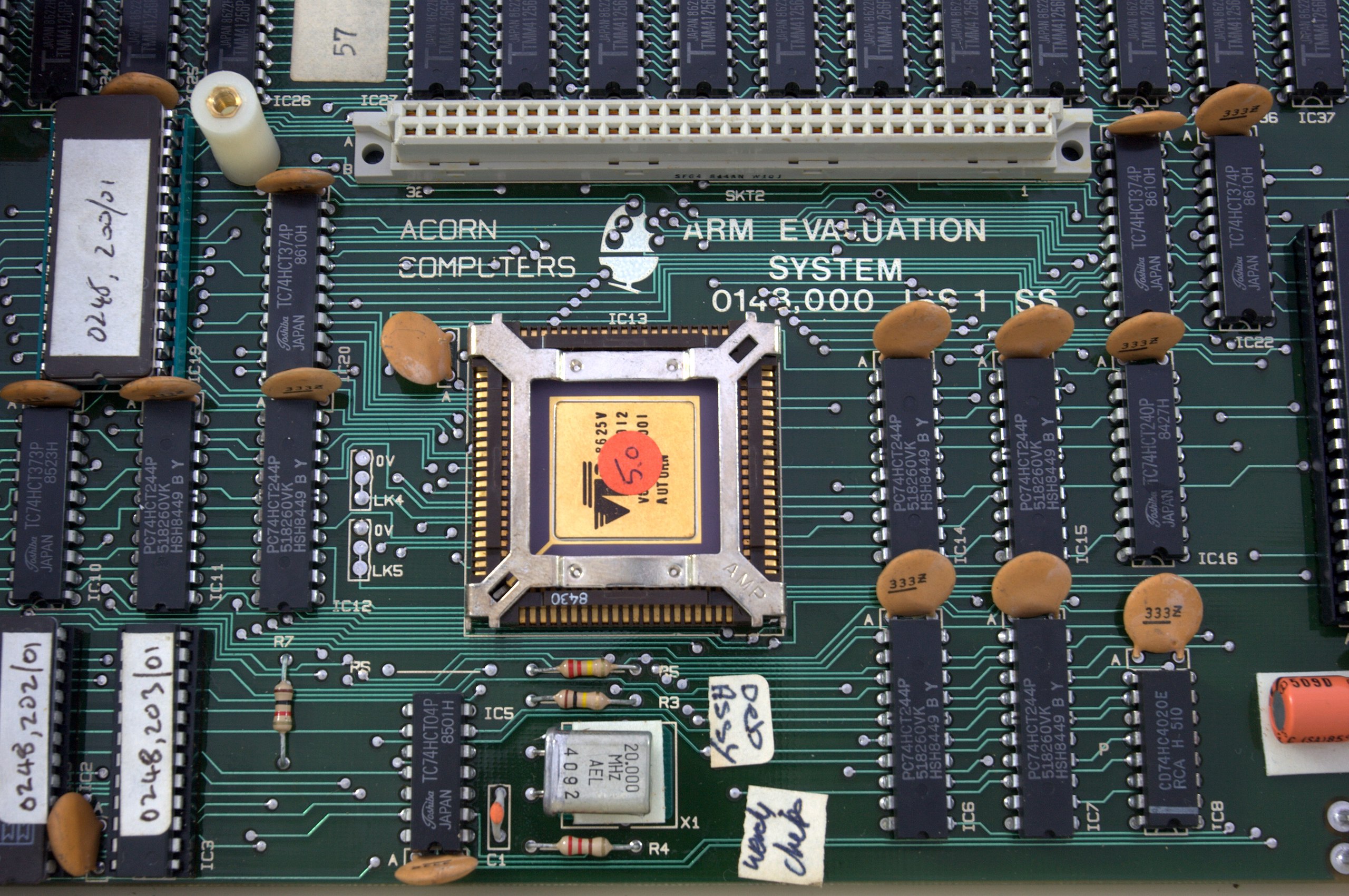

Processeur ARM1 installé dans le système d'évaluation Acorn ARM

Processeur ARM1 installé dans le système d'évaluation Acorn ARMLa plupart des sites sont utilisés pour les lignes d'adresse et les lignes de données menant à la mémoire. La puce possède 26 lignes d'adresse qui lui permettent d'accéder à 64 mégaoctets de mémoire et 32 lignes de données, ce qui lui permet de lire ou d'écrire 32 bits à la fois. Les lignes d'adresse sont dans le coin inférieur gauche et les lignes de données sont à droite. Dans le modèle de simulation de la puce, vous pouvez voir que les signaux sont envoyés aux lignes d'adresse de la mémoire et que les informations de la mémoire sont lues le long des lignes de données. Le côté droit du simulateur affiche les valeurs d'adresse et de données présentées au format hexadécimal. Si vous connaissez le système numérique hexadécimal, vous pouvez facilement corréler ces valeurs avec les états de contact.

Chaque coin de la puce a une ligne d'alimentation (+) et une ligne de masse (-), fournissant une tension d'alimentation de 5 volts, qui est nécessaire au fonctionnement de la puce. Divers signaux de contrôle sont situés en haut de la puce. Dans le simulateur, il est facile de remarquer deux signaux d'horloge qui définissent l'impulsion d'horloge. Les fréquences des phases 1 et 2 alternent, fournissant le signal d'horloge nécessaire au fonctionnement de la puce. Dans notre simulation visuelle, elle devient active environ deux fois par seconde, mais la vraie puce a une fréquence de 8 mégahertz, ce qui est plus d'un million de fois plus rapide. Faites attention au nom du fabricant «ACORN» sur la puce au lieu de 82 broches.

Deux signaux de synchronisation

Deux signaux de synchronisationHistorique du processeur ARM

Le microprocesseur ARM1 a été conçu en 1985 par les ingénieurs Sophie Wilson et Steve Farber d'Acorn Computers. Initialement, la puce s'appelait Acorn RISC Machine et était conçue comme coprocesseur pour le

micro- ordinateur

BBC .

Sophie Wilson et Steve Farber

Sophie Wilson et Steve FarberAu total, plusieurs centaines de microprocesseurs ARM1 ont été produits, on pourrait donc penser qu'il a été perdu dans les entrailles de l'histoire des microprocesseurs des années 1980. Cependant, la première puce ARM1 a conduit à une architecture ARM étonnamment réussie, avec plus de 50 milliards de puces. Que s'est-il passé?

Au début des années 1980, la recherche scientifique a suggéré que si vous simplifiez l'ensemble d'instructions pour le processeur, les développeurs obtiendront de meilleures performances - le processeur sera plus simple mais plus rapide: un ordinateur avec un jeu d'instructions réduit ou RISC (ordinateur avec jeu d'instructions réduit). La recherche à

Stanford et

Berkeley a inspiré les développeurs ARM à choisir l'architecture RISC. De plus, étant donné la petite équipe de développement Acorn, choisir RISC était une solution pratique.

Sur un ordinateur RISC, l'ensemble d'instructions était limité aux plus fréquemment utilisées, optimisé pour de hautes performances et exécuté en un seul cycle d'horloge. Les instructions, quant à elles, sont de taille fixe, ce qui simplifie la logique de décodage des instructions. Un processeur RISC nécessite beaucoup moins de circuits pour le contrôle des commandes et le décodage, ce qui vous permet de placer plus de composants sur la puce.

La simplicité de la conception RISC est évidente en comparant les microprocesseurs ARM1 et Intel 80386 commercialisés la même année: ARM1 avait environ vingt-cinq mille transistors, et 80386 avait deux cent soixante-quinze mille. Voici deux photos des processeurs à la même échelle. L'aire du cristal ARM1 est de cinquante millimètres carrés, par rapport aux cent quatre millimètres carrés du 386e.

En raison du petit nombre de transistors, le processeur ARM1 avait une faible puissance: environ un dixième de watt contre près de deux watts au 386th. La combinaison de hautes performances et d'une faible consommation d'énergie a rendu les versions ultérieures des microprocesseurs ARM très populaires pour les systèmes embarqués. Apple a choisi un processeur ARM pour son infortuné système Pocket Newton. En 1990, Acorn Computers, Apple et le fabricant de puces VLSI Technology ont créé Advanced RISC Machines pour continuer à développer ARM.

Depuis lors, ARM est devenu l'architecture la plus populaire avec plus de cinquante milliards de processeurs. La plupart des appareils mobiles utilisent un microprocesseur ARM. Par exemple, le processeur Apple A8 à l'intérieur de l'iPhone 6 utilise l'ARMv8-A 64 bits. Malgré ses modestes débuts, ARM1 a fait la liste IEEE Spectrum

de 25 puces qui a choqué le monde et est devenu les microprocesseurs les plus influents selon PC World pour toujours.

Fait intéressant, ARM ne fabrique pas de puces. Au lieu de cela, la propriété intellectuelle ARM est concédée sous licence à des centaines d'entreprises différentes qui fabriquent des puces en utilisant l'architecture ARM.

Structure de puce de bas niveau

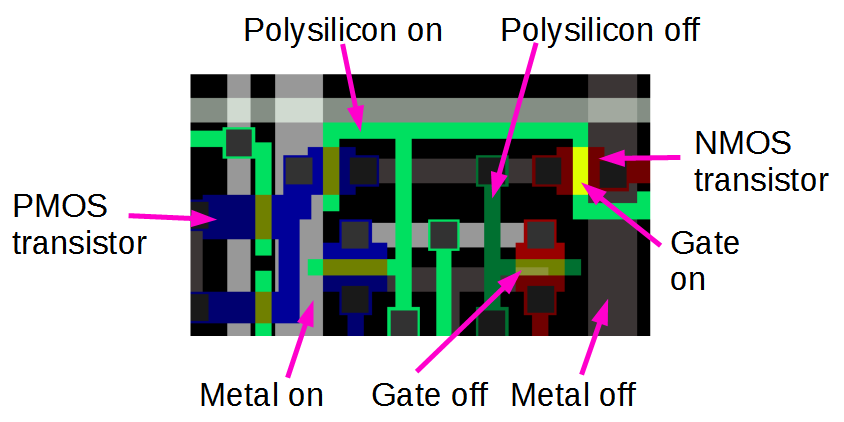

Le microprocesseur ARM1 se compose de cinq couches. Si vous augmentez l'échelle de la puce dans le modèle de simulation, vous pouvez voir les composants de la puce construits à partir de ces couches. Le modèle de simulation utilise une couleur spécifique pour chaque couche et désigne les lignes d'activité avec sa couleur. La couche inférieure est constituée de silicium, sur lequel se trouvent des transistors. Pendant la production, les zones de silicium sont modifiées (alliées) à l'aide de diverses impuretés. Le silicium peut être dopé positivement pour former un transistor P-MOS (bleu) ou négativement pour un transistor N-MOS (rouge). Le silicium non allié est essentiellement un isolant (noir).

Simulator ARM1 présente différentes couches avec ses propres couleurs.

Simulator ARM1 présente différentes couches avec ses propres couleurs.Les lignes de polysilicium marquées en vert sont appliquées sur le silicium. Lorsque le polysilicium traverse le silicium dopé, il forme une grille de transistor (jaune). Enfin, deux couches de métal, indiquées en gris, sont situées au sommet du polysilicium et assurent la conductivité. Les carrés noirs sont des contacts qui forment des liaisons entre différentes couches.

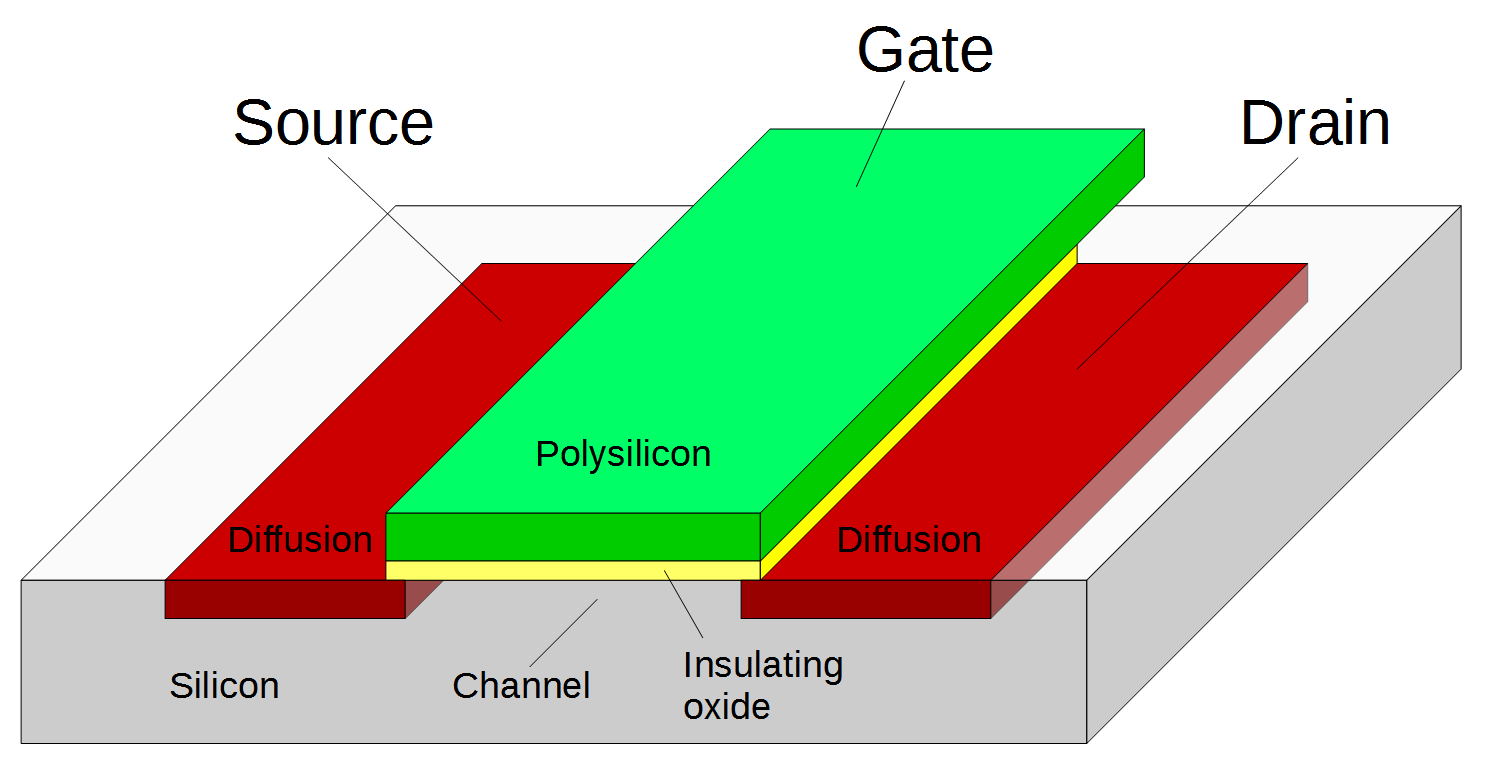

Pour nos besoins, le transistor MOS peut être considéré comme un interrupteur commandé par des grilles. Lorsqu'il est allumé (fermé), le drain et la source dans les régions de silicium sont connectés. Lorsqu'il est déconnecté (ouvert), le drain et la source sont déconnectés.

Structure MOSFET

Structure MOSFETComme la plupart des processeurs modernes, ARM1 a été construit en utilisant la technologie CMOS, qui utilise deux types de transistors MOS: canal N et canal P. Les MOSFET à canal N ne sont activés que lorsqu'un signal de haut niveau est appliqué à la porte et que la sortie est mise à la masse. Les MOSFET à canal P s'activent lorsqu'un signal de bas niveau est appliqué à la grille et que des tensions jusqu'à cinq volts sont appliquées à la sortie.

Le concept d'un fichier de registre

Le fichier de registre est un composant clé d'ARM1 qui stocke des informations à l'intérieur de la puce. Le fichier de registre se compose de vingt-cinq registres, chacun contenant trente-deux bits.

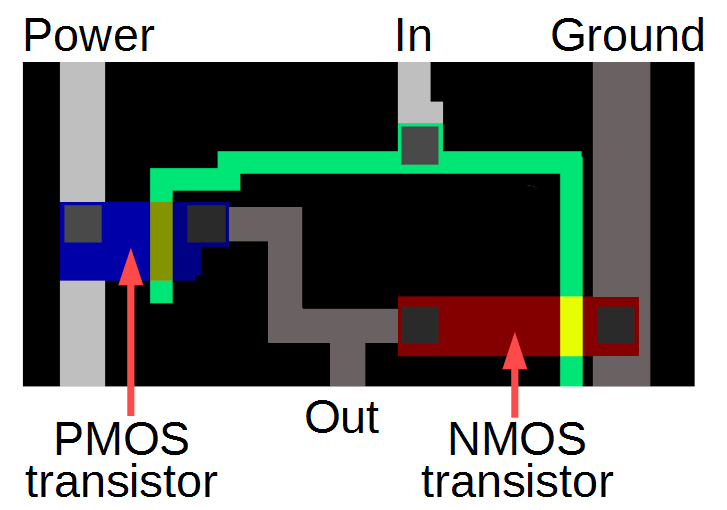

L'image ci-dessous montre deux transistors formant un inverseur. Si un signal de haut niveau est entré, le transistor N-MOS (rouge) se met sous tension, connectant la sortie à la masse, de sorte que la sortie ait un signal de bas niveau. Si l'entrée reçoit un signal de bas niveau, le transistor P-MOS (bleu) se met sous tension, connectant la ligne d'alimentation à la sortie, de sorte que la sortie ait un signal de haut niveau. Ainsi, la sortie est opposée à l'entrée, créant un inverseur.

Onduleur

OnduleurLa combinaison de deux onduleurs en boucle forme un schéma de stockage simple. Si à la sortie du premier onduleur 1, le second produit 0, qui va à l'entrée du premier onduleur et 1 est créé à sa sortie - le circuit est stable. Par conséquent, le circuit restera dans cet état indéfiniment, en se «souvenant» d'un bit, jusqu'à ce qu'il soit transféré de force dans un autre état.

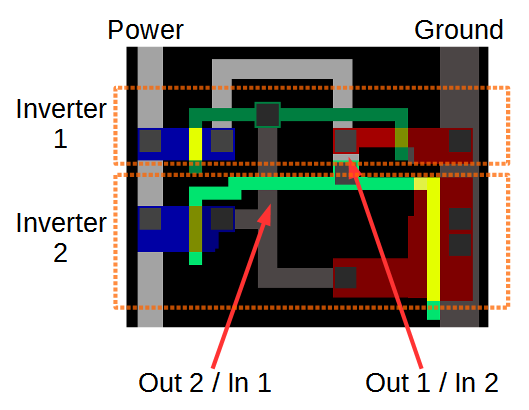

Deux onduleurs forment un registre pouvant stocker 1 bit

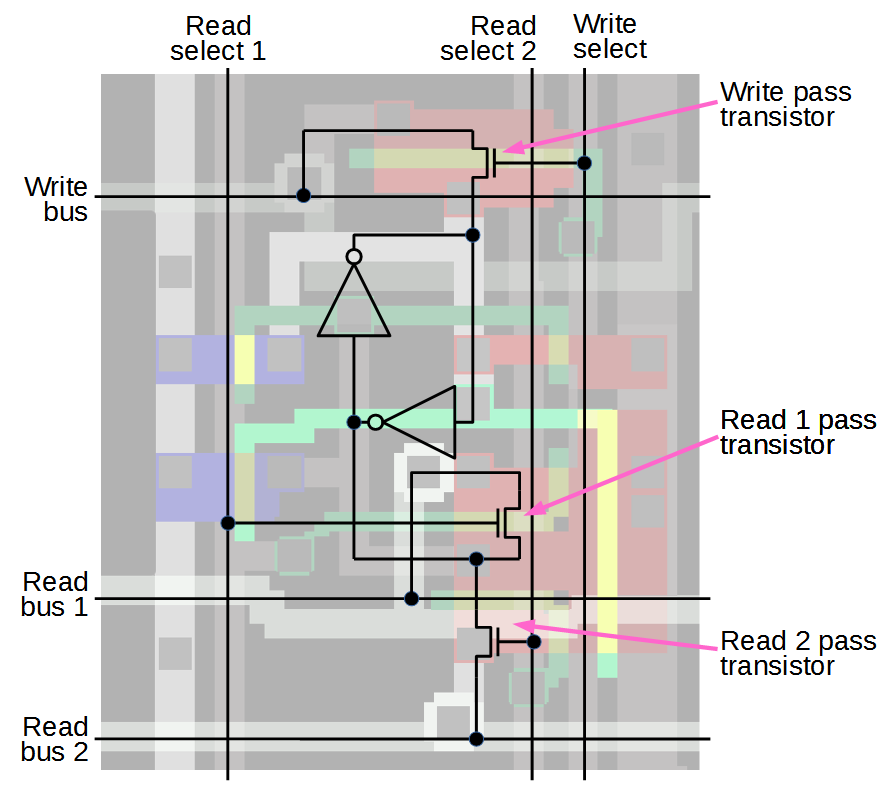

Deux onduleurs forment un registre pouvant stocker 1 bitPour créer un tel schéma dans la cellule de registre utilisée, des lignes de lecture et d'écriture sont ajoutées, ainsi que des lignes de sélection pour connecter la cellule aux lignes de bus. Lorsque la ligne d'enregistrement est activée, le bus est mis en contact avec l'onduleur, ce qui vous permet d'écraser la valeur actuelle avec un nouveau bit. De même, les transistors connectent le bit au bus de lecture lorsque la ligne de sélection correspondante est activée, vous permettant de lire la valeur stockée.

Schéma d'un bit du fichier de registre ARM1

Schéma d'un bit du fichier de registre ARM1Pour créer un fichier de registre, la cellule de registre doit être répétée 32 fois verticalement pour chaque bit et 25 fois horizontalement pour former chaque registre. Chaque registre a trois lignes horizontales - une ligne d'enregistrement et deux lignes de lecture. Chaque registre a trois lignes de contrôle verticales - une ligne de sélection d'enregistrement et deux lignes de sélection de lecture. Lors de l'activation des lignes de contrôle souhaitées, deux registres peuvent être lus et un registre peut être écrit à la fois. Dans le modèle de simulation - vous pouvez voir les lignes de contrôle verticales actives pour sélectionner les registres et les bits de données se déplaçant sur les lignes de bus horizontales.

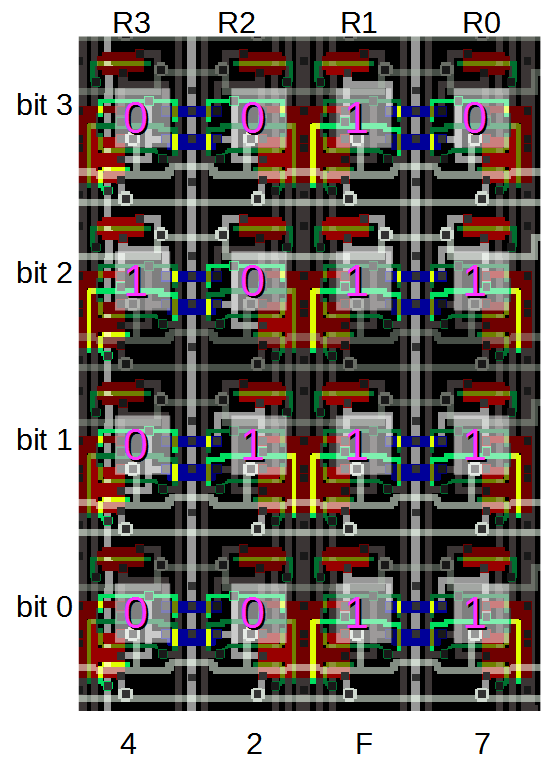

En regardant la cellule de mémoire dans le simulateur, vous pouvez déterminer quel onduleur est activé et déterminer si le bit 0 ou 1. est égal. Si l'entrée de l'onduleur supérieur est active, le bit est nul. Si l'entrée de l'onduleur inférieur est active, le bit est égal à un. Ainsi, après avoir soigneusement regardé, vous pouvez lire les valeurs des registres directement depuis le simulateur.

Image du fichier registre ARM1

Image du fichier registre ARM1Dispositif de changement rapide

Le dispositif de changement rapide effectue des décalages binaires et est un autre composant intéressant d'ARM1. La plupart des instructions utilisent un shifter qui vous permet de déplacer l'argument binaire vers la droite, la gauche ou d'alterner n'importe quel caractère (de 0 à 31 bits). Au début du simulateur, vous pouvez voir les lignes diagonales se déplacer vers la droite et la gauche dans un décalage rapide.

L'image ci-dessous montre la structure du dispositif de cisaillement. Les bits sont décalés verticalement par rapport au zéro et au trente et unième bits. Les bits de sortie sont décalés horizontalement entre le bit zéro du bas et le trente et unième bit du haut. Les lignes diagonales indiquent où les lignes verticales sont connectées aux lignes horizontales, générant un décalage dans la sortie. Différentes positions de la ligne diagonale entraînent des décalages différents. La ligne diagonale supérieure décale les bits vers la gauche et la ligne diagonale inférieure vers la droite. Pendant un quart de travail, les deux diagonales sont actives; il peut être imperceptible, mais dans la partie décalée du mot, la partie se déplace vers la droite, et souvent vers la gauche.

Structure du dispositif de cisaillement rapide

Structure du dispositif de cisaillement rapideAgrandissons la zone du dispositif de cisaillement pour mieux voir ses principaux composants. Il contient 32 par 32 coupes transversales de transistors, dont chacun relie une ligne verticale à une horizontale. Les grilles de transistor sont connectées par des lignes de commande diagonales; des transistors le long de la diagonale active relient les lignes verticales et horizontales correspondantes. Ainsi, en activant les diagonales correspondantes, les lignes de sortie sont connectées aux lignes d'entrée décalées d'un certain nombre de bits. Puisque les lignes d'entrée du microcircuit fonctionnent horizontalement, il y a 32 connexions entre les lignes d'entrée et les lignes de bits verticales correspondantes.

Zoom sur le dispositif de changement rapide ARM1

Zoom sur le dispositif de changement rapide ARM1Conclusion

Le microprocesseur ARM1 a conduit à l'architecture étonnamment réussie du processeur ARM, qui est le cœur de votre smartphone et de tout appareil mobile en général. L'architecture RISC simple de la puce ARM1 simplifie la compréhension des circuits du microprocesseur par rapport à la structure 80386. La simulation visuelle fascinante du microprocesseur ARM aide à comprendre ce qui se passe à l'intérieur.

Notre vidéo créée par cet article:

Inside the CPU: ARM1