Préface

Je suis très heureux de vous parler en détail de mon premier circuit intégré et de partager les rebondissements de ce projet, dans lequel j'étais engagé au cours de la dernière année. J'espère que mon succès en inspirera d'autres et aidera à lancer une révolution dans la production de puces maison. Quand j'ai commencé ce projet, je ne savais pas dans quoi je m'impliquais, mais à la fin j'ai appris plus que je n'ai pensé à la physique, la chimie, l'optique, l'électronique et bien d'autres domaines.

De plus, mes efforts ne se sont accompagnés que des critiques et du soutien les plus positifs du monde entier. Je suis sincèrement reconnaissant à tous ceux qui m'ont aidé, donné des conseils et inspiré pour ce projet. Surtout à mes parents incroyables qui non seulement me soutiennent et m'encouragent toujours dès qu'ils le peuvent, mais ont également fourni un lieu de travail et supporté le coût de l'électricité ... Merci!

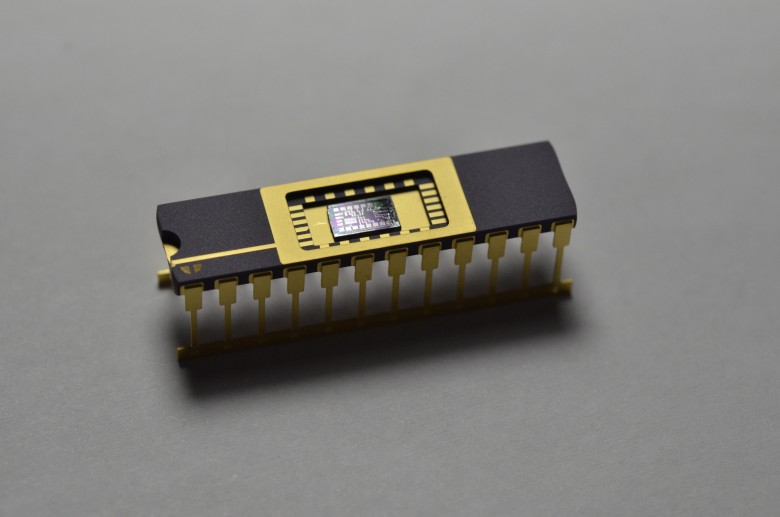

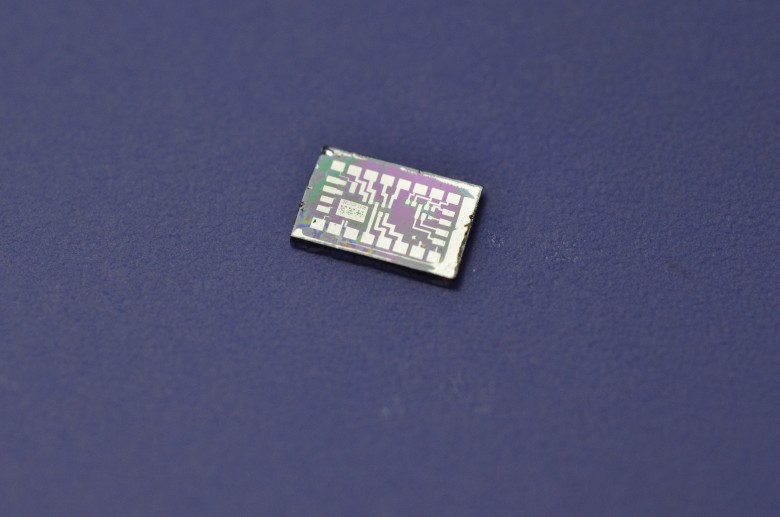

Sans plus tarder, je présente le premier circuit intégré (IC) fabriqué par la méthode lithographique dans des conditions domestiques (garage) - la puce PMOS de l'amplificateur différentiel double Z1.

Je dis «fait par méthode lithographique» parce que Jerry Ellsworth a fabriqué les premiers transistors et portes logiques (avec des connexions soigneusement posées par de l'époxy conducteur) et a montré au monde que c'était possible. Inspiré par son travail, je présente des circuits intégrés créés par un processus photolithographique standard évolutif. Inutile de dire que c'est une avancée logique par rapport à mon travail précédent, où j'ai

reproduit le transistor à effet de champ Jerry .

La conception

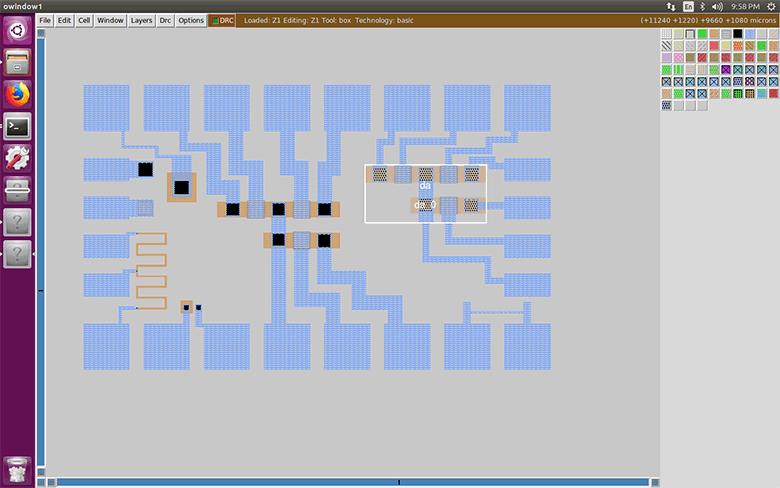

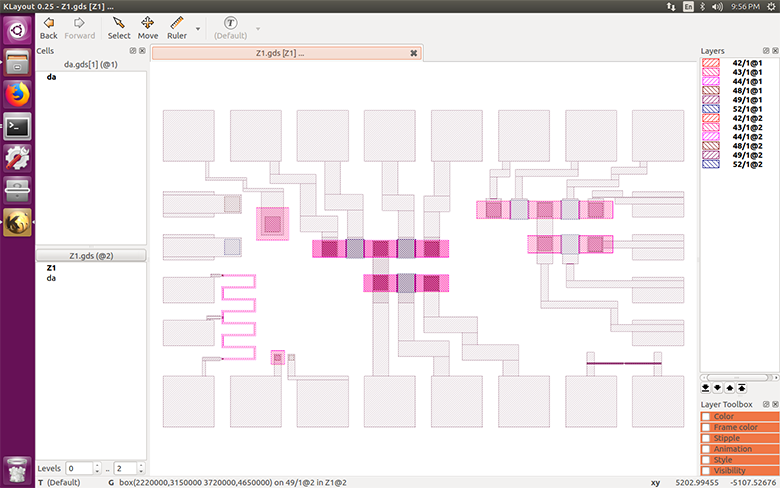

J'ai

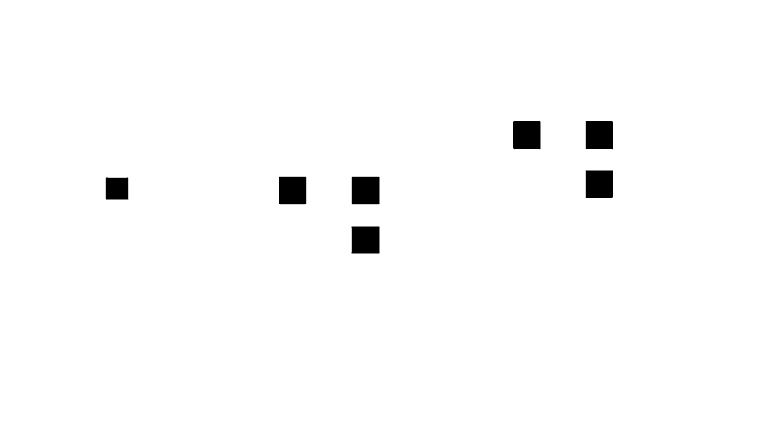

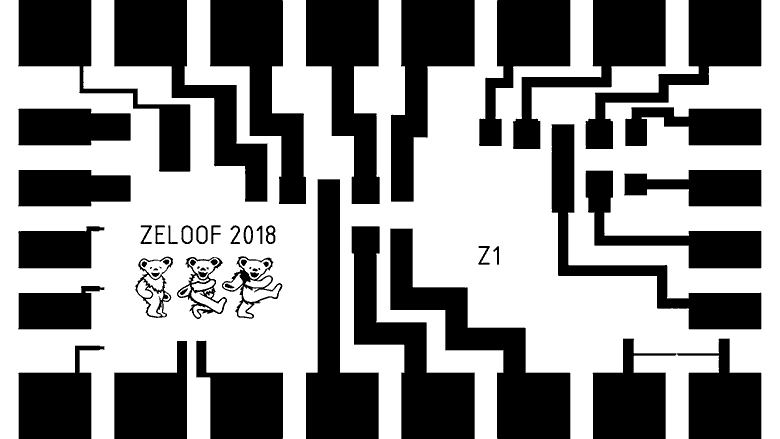

développé l'amplificateur Z1 lorsque je cherchais une puce simple pour tester et régler mon processus. La disposition a été réalisée en

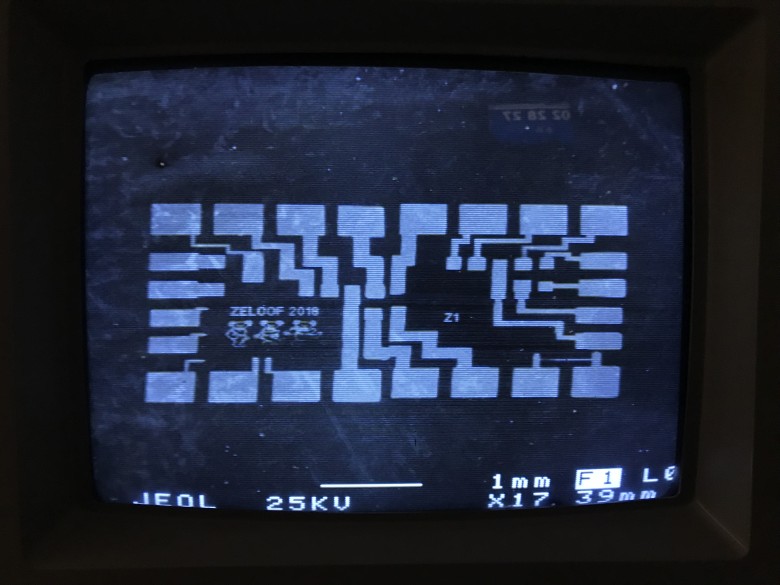

Magic VLSI pour le processus PMOS avec quatre masques (région active / dopée, oxyde de grille, fenêtre de contact et couche métallique supérieure). Le PMOS a un avantage sur le NMOS en ce qui concerne les impuretés ioniques dues à la fabrication dans un garage. Les masques sont conçus avec un rapport d'aspect de 16: 9 pour simplifier la projection.

Disposition Magic VLSI

Disposition Magic VLSI Génération de masques

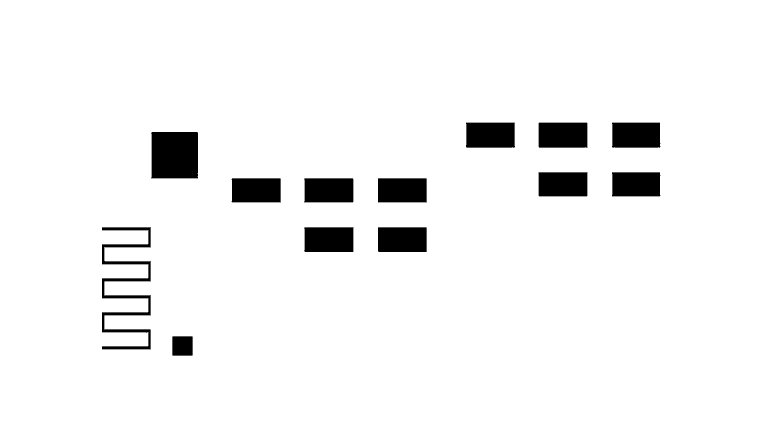

Génération de masques Zone active

Zone active Obturateur

Obturateur Contactez-nous

Contactez-nous Métal

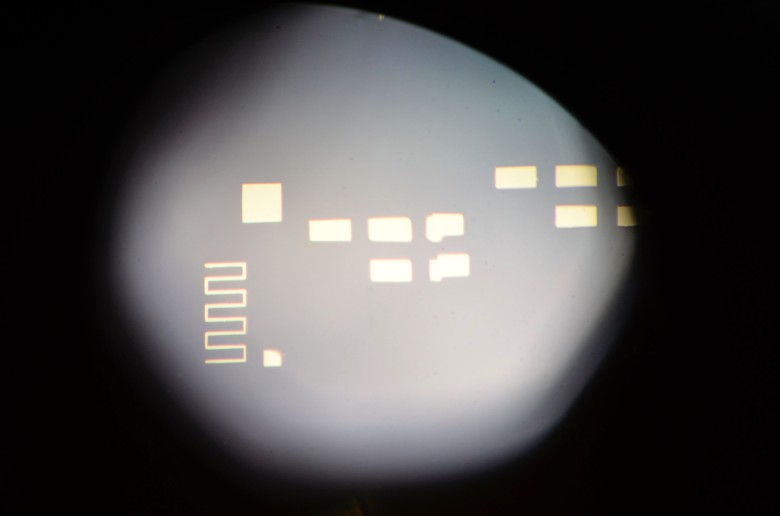

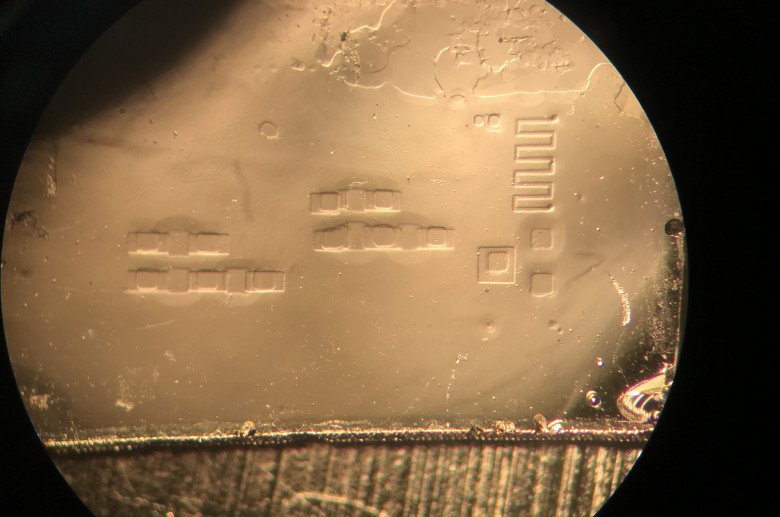

MétalLa taille de l'obturateur est d'environ 175 microns, bien que des éléments jusqu'à 2 microns soient fabriqués sur la puce pour vérification. Chaque section d'amplificateur (centre et droite) contient trois transistors (deux pour un

circuit push-pull avec une résistance de cathode commune et un comme source de courant / résistance de charge), ce qui signifie un total de six transistors par CI. Le côté gauche des résistances, condensateurs, diodes et autres éléments de test pour étudier les caractéristiques du processus. Chaque nœud des paires différentielles sort avec une broche distincte sur la trame de sortie, il peut donc être étudié et, si nécessaire, ajouter un décalage externe.

Fabrication

Le processus de fabrication comprend 66 étapes individuelles et dure environ 12 heures. Le rendement atteint 80% pour les gros articles, mais dépend fortement de la quantité de café que vous buvez un jour particulier. J'ai également enregistré une vidéo sur YouTube sur la

théorie de la production de microcircuits et

sur la fabrication de transistors MOS séparément .

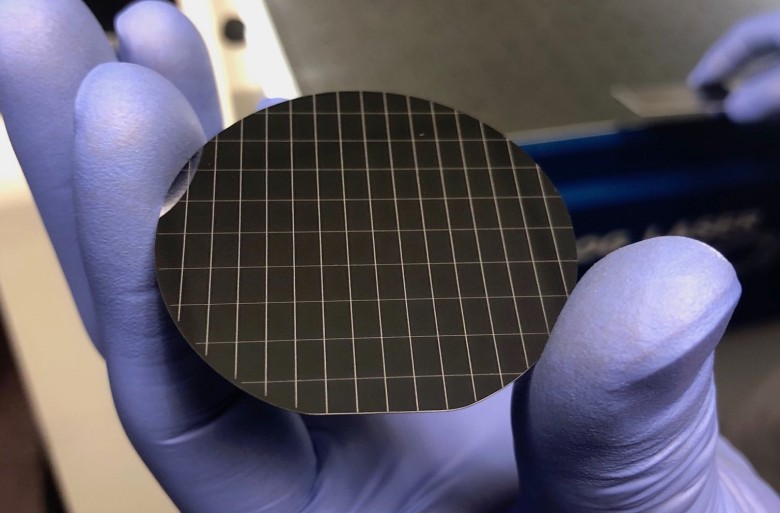

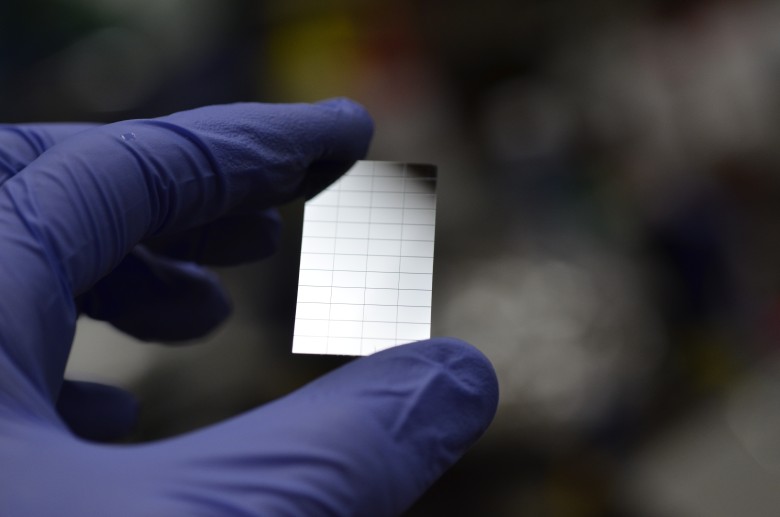

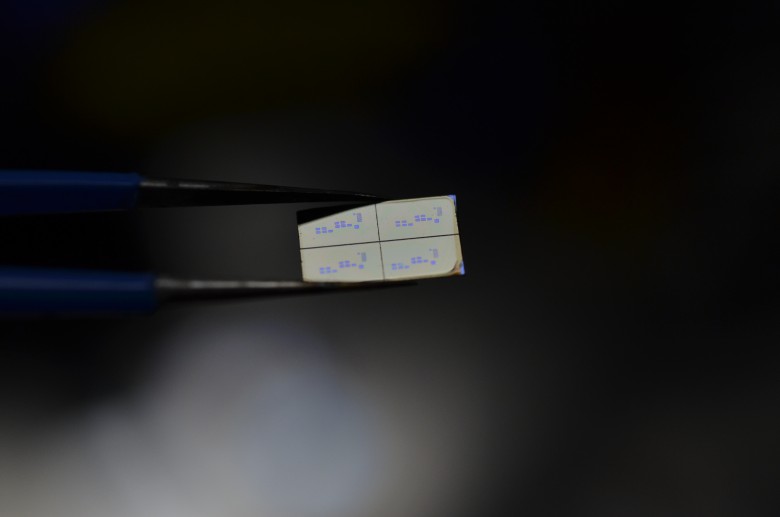

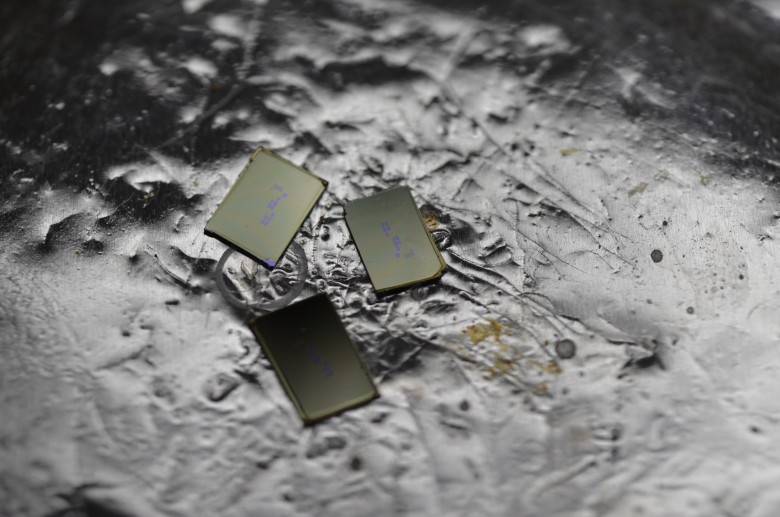

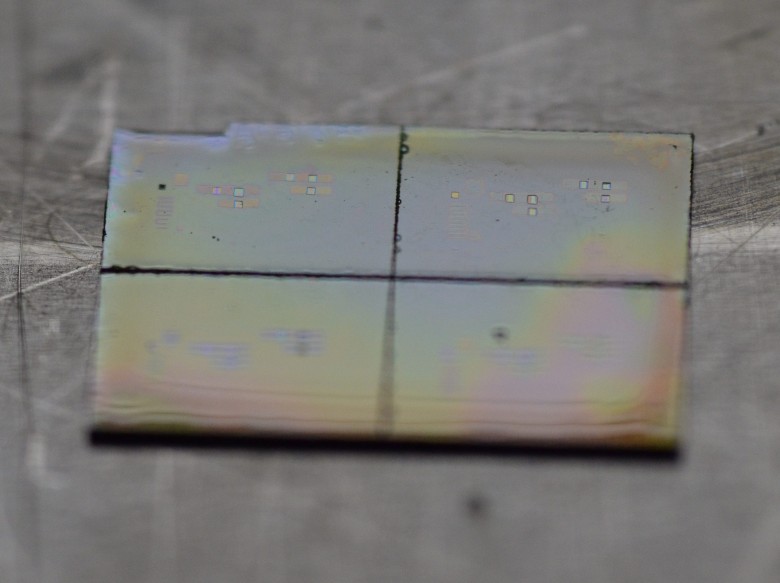

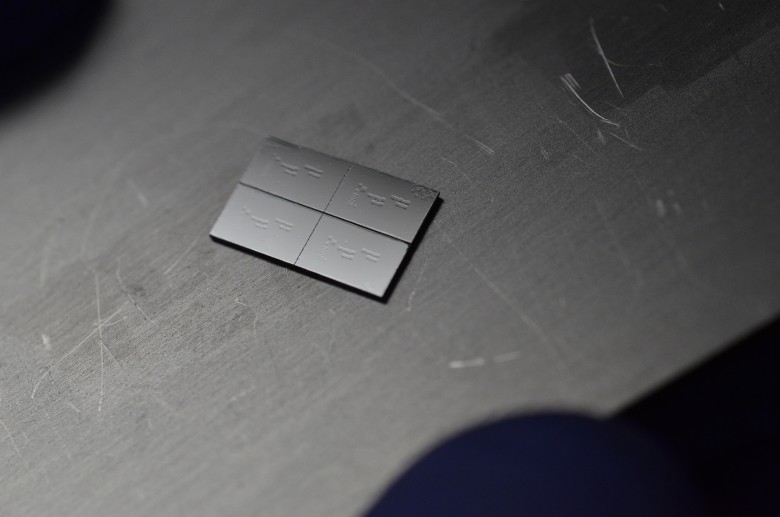

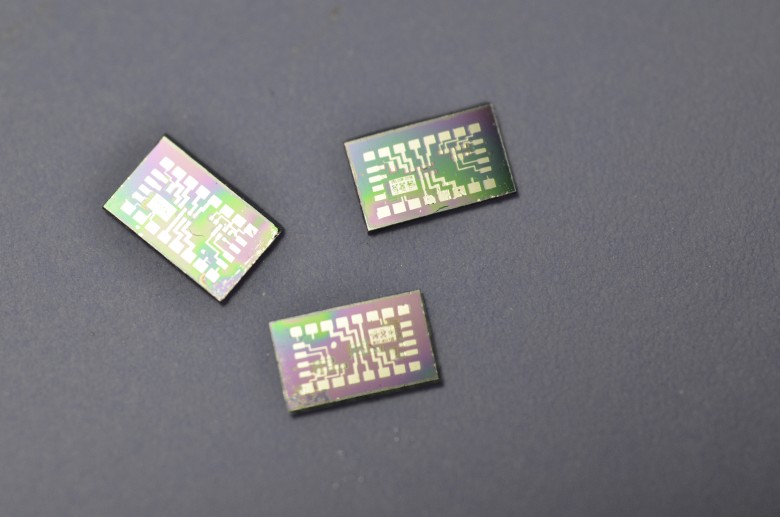

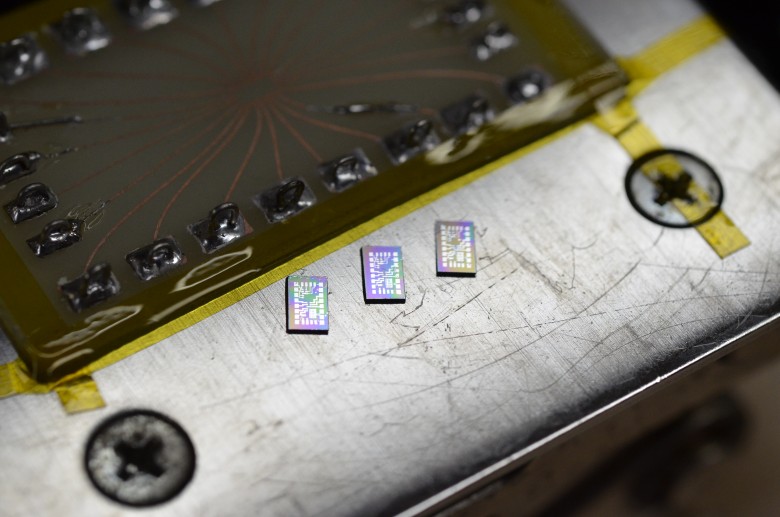

Les plaquettes de silicium de 50 mm (2 ") sont divisées en cristaux de 5,08 x 3,175 mm (environ 16 mm² de surface)

avec un laser à fibre Epilog . La taille du cristal est choisie pour s'adapter au boîtier DIP 24 broches Kyocera.

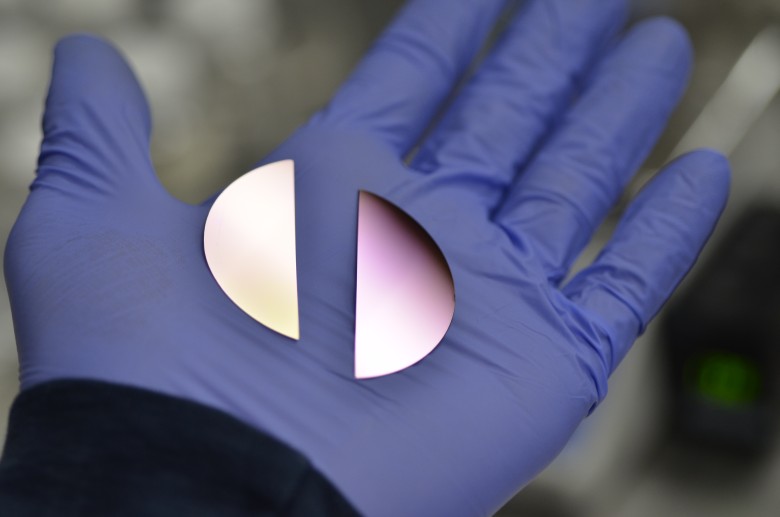

Plaque de type N 50 mm

Plaque de type N 50 mm Plaque de type N 50 mm

Plaque de type N 50 mmTout d'abord, l'oxyde natif est éliminé de la plaque par immersion rapide dans du fluorure d'hydrogène dilué, suivi d'un traitement intensif avec un mélange de gravure piranha (un mélange d'acide sulfurique et de peroxyde d'hydrogène), un mélange RCA 1 (eau, ammoniac, peroxyde d'hydrogène), un mélange RCA 2 (eau, acide chlorhydrique, peroxyde d'hydrogène) et immersion répétée dans le fluorure d'hydrogène.

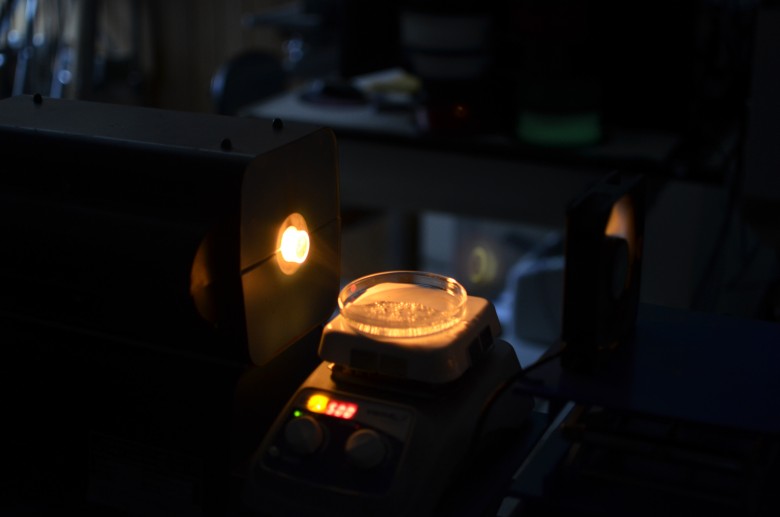

L'oxyde protecteur

croît thermiquement dans la vapeur d'eau de l'air ambiant (oxydation humide) jusqu'à une épaisseur de 5000 à 8000 Å.

Oxydation thermique humide

Oxydation thermique humide Oxydation thermique humide

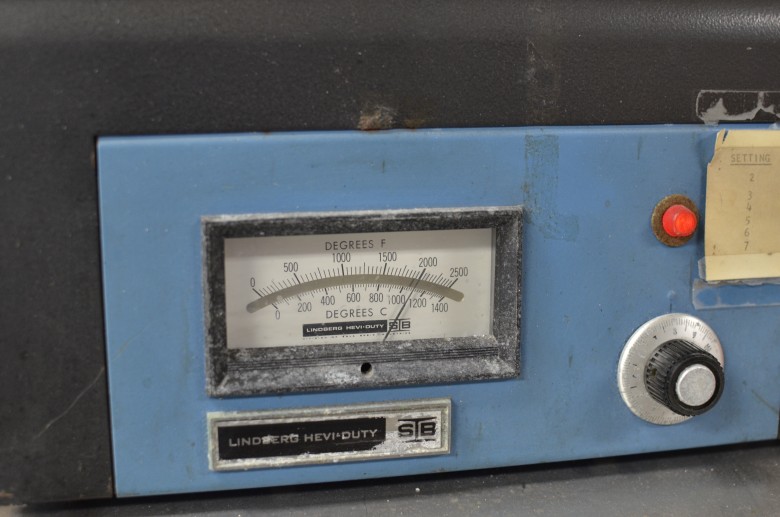

Oxydation thermique humide Four tubulaire

Four tubulaire Plaque oxydée

Plaque oxydéeLa plaque oxydée est prête à se former dans la région active / dopée (type P). La

résine photosensible

AZ4210 est appliquée sur un

sein tournant à environ 3000 tr / min, formant un film d'environ 3,5 microns d'épaisseur, qui est doucement séché à 90 ° C sur une plaque chauffante.

Processus de lithographie en détailLe masque de base est traité par mon

stepper photolithographique Mark IV dans l'ultraviolet avec un pas de 365 nm - et la structure est élaborée dans une solution d'hydroxyde de potassium.

Résister à la structure

Résister à la structure Résister à la structure

Résister à la structure 30 minutes de séchage

30 minutes de séchage Gravure de base

Gravure de baseAprès cela, la structure de réserve est solidifiée et

plusieurs autres astuces sont utilisées pour assurer une bonne adhérence et une résistance chimique lors de la prochaine gravure dans le fluorure d'hydrogène, qui transfère cette structure à la couche d'oxyde de grille et ouvre les fenêtres au silicium nu pour le dopage. Ces régions deviendront plus tard la source et le drain du transistor.

Les particules ferment l'obturateur

Les particules ferment l'obturateur Cristaux en alliage avec portes gravées

Cristaux en alliage avec portes gravéesAprès cela, l'alliage est effectué, c'est-à-dire l'introduction d'impuretés à partir d'une source solide ou liquide. En tant que source solide, un disque de nitrure de bore est utilisé, situé à proximité (moins de 2 mm) de la plaque dans un four tubulaire. Alternativement, vous pouvez préparer une source liquide d'acide phosphorique ou borique dans de l'eau ou un solvant - et enduire selon le processus standard d'

application / immersion dans le fluorure d'hydrogène / diffusion / élimination de la glaçure .

Les étapes de configuration ci-dessus sont ensuite répétées deux fois pour l'oxyde de grille et la couche de contact. L'oxyde de grille doit être beaucoup plus mince (moins de ~ 750 Å) que l'oxyde protecteur, de sorte que les zones entre le drain / la source sont gravées - et un oxyde plus mince y pousse. Puis, puisque toute la plaque a été oxydée lors de l'étape de dopage, les fenêtres de contact doivent être gravées pour établir le contact de la couche métallique avec les zones source / drain dopées.

Tous les transistors sont maintenant formés et prêts pour les interconnexions avec accès à la trame de sortie. La couche protectrice d'aluminium (400-500 nm) est

pulvérisée ou

thermiquement pulvérisée sur la plaque. Une alternative serait le processus de décollage, lorsqu'un photorésist est d'abord formé puis que le métal est déposé.

Métal projeté

Métal projeté Métal projeté

Métal projetéEnsuite, un motif de photolithographie est formé sur la couche métallique et gravé dans de l'acide phosphorique chaud se produit pour achever la fabrication du circuit intégré. Les dernières étapes avant le test sont l'inspection visuelle et le recuit à haute température de l'aluminium pour former des jonctions ohmiques.

La puce est maintenant prête pour l'emballage et les tests.

Je n'ai pas d'installation de microsoudeuse (j'accepte les dons!), Alors maintenant le processus de test se limite à palper la plaque avec une pince pointue ou à utiliser une carte à puce (difficile à aligner) avec une connexion au personnage. L'amplificateur différentiel est également testé empiriquement dans le circuit pour vérifier son fonctionnement.

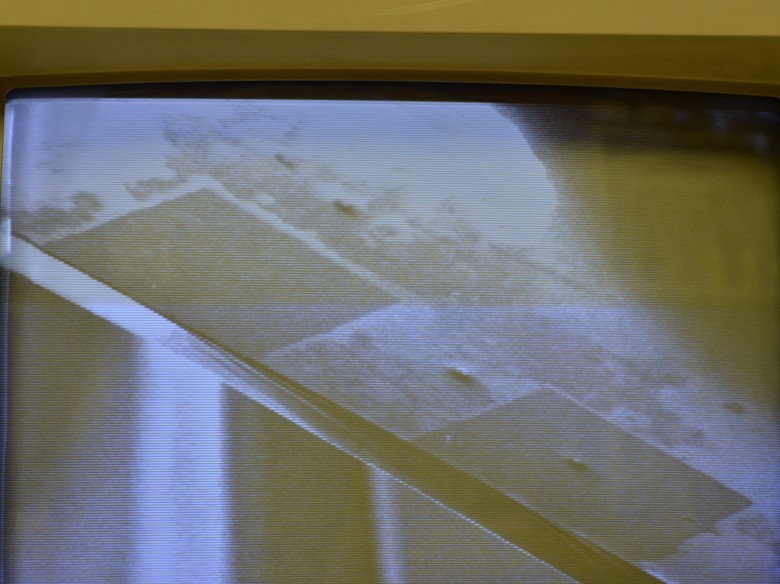

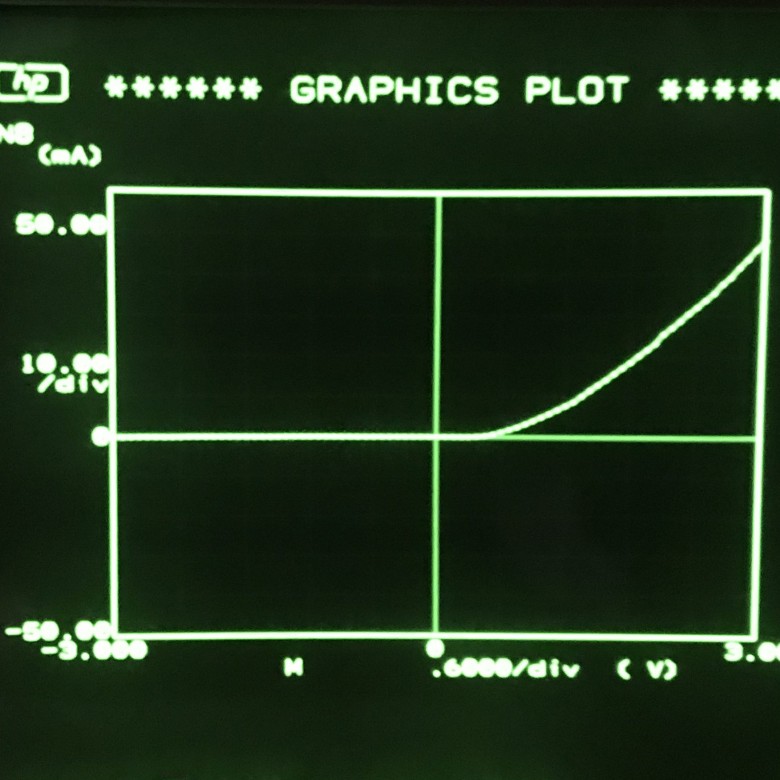

Courbe IV

Courbe IV Courbe IVCourbe FET Ids / Vds du précédent appareil NMOS

Courbe IVCourbe FET Ids / Vds du précédent appareil NMOSBien sûr, ces courbes sont loin d'être idéales (notamment en raison d'une résistance de contact excessive et d'autres facteurs similaires), mais je m'attends à une amélioration des performances si j'obtiens l'installation de la micro-soudure. Cela peut expliquer en partie certaines différences d'un cristal à l'autre. Bientôt, j'ajouterai de nouvelles courbes IV, des caractéristiques de transistor et d'amplificateur différentiel à

cette page .