Dans chaque article sur Habré consacré aux microprocesseurs nationaux, d'une manière ou d'une autre, la question des blocs IP sous licence et la mesure dans laquelle leur présence et leur absence réduisent la valeur, la domestication ou la sécurité du développement sont soulevées. Dans le même temps, de nombreux commentateurs ne comprennent pas très bien le sujet de la discussion, alors essayons de comprendre exactement comment fonctionnent les licences dans l'industrie microélectronique, quels sont les bons et les mauvais blocs sous licence et quel est le processus de développement d'un microcircuit, si la plupart des blocs y sont achetés.

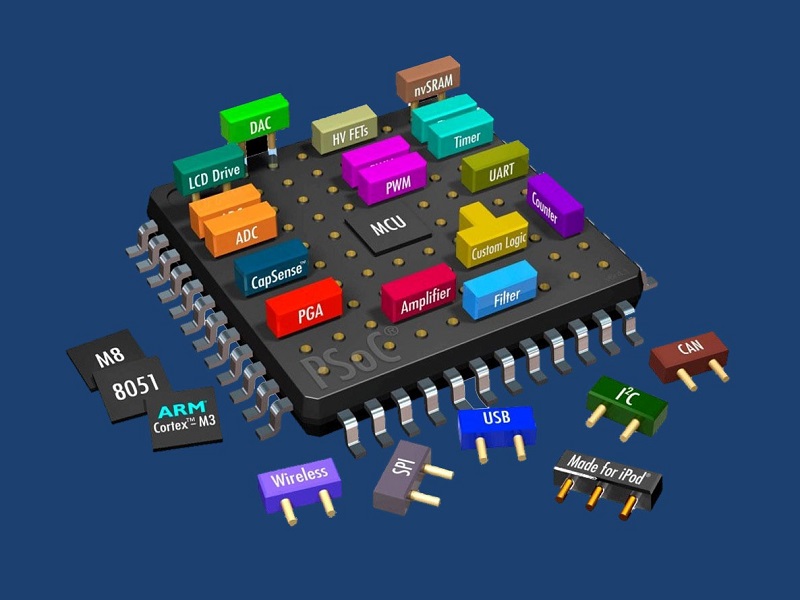

Tout microcircuit moderne est ce que l'on appelait fièrement «un système sur une puce» il y a quelque temps: même les régulateurs linéaires à trois pattes et les sources de tension ont un réglage numérique caché à l'utilisateur, que pouvons-nous dire des microprocesseurs et microcontrôleurs contenant des dizaines de blocs différents, le développement de chacun dont nécessite des compétences spécifiques et une vaste expérience pour contourner les pièges qui ne sont pas écrites dans les livres et articles. De plus, tout projet, en règle générale, a sa propre fonctionnalité de tueur, en raison de laquelle les développeurs s'attendent à obtenir un avantage sur les concurrents, et c'est cette fonctionnalité de tueur qui devrait être faite aussi bien que possible, et tous les autres blocs ne devraient tout simplement pas être pire que les autres.

Attention, la question est: est-il nécessaire de maintenir une équipe de développement coûteuse capable de réaliser indépendamment tous les blocs nécessaires?

Une question encore plus intéressante: si vous avez vous-même développé un système d’instruction à microprocesseur, devez-vous contenir une équipe de programmeurs qui

rédigera un compilateur pour cela ,

portera de nouveaux noyaux de systèmes d’exploitation populaires, fera beaucoup d’autres travaux difficiles, et très probablement, il ne mettra pas votre création sur un seul au niveau des architectures populaires, sur lesquelles beaucoup plus de personnes travaillent?

Et surtout: des réponses positives aux deux questions précédentes donneront-elles des avantages compétitifs à votre produit?

Digression lyriqueLe 5 juin, Morris Chang a pris sa retraite, un homme dont vous n'aviez jamais entendu parler, mais sans lequel il n'y aurait pas d'électronique moderne. Morris Chang est né en Chine, au plus fort de la guerre civile qu'il a quitté pour les États-Unis, est diplômé du MIT, puis a travaillé pendant de nombreuses années chez Texas Instruments et General Instruments. Au cours de ces années, une partie intégrante de toute entreprise de microélectronique était sa propre production, dont l'équipement était plusieurs fois moins cher qu'aujourd'hui, mais néanmoins, il était très cher. Voici comment Chang lui-même a écrit à ce sujet:

Lorsque j'étais à TI et à General Instrument, j'ai vu beaucoup de concepteurs de circuits intégrés souhaitant quitter et créer leur propre entreprise, mais la seule chose, ou la plus grande chose qui les a empêchés de quitter ces sociétés, était qu'ils ne pouvaient pas collecter suffisamment d'argent. pour former leur propre entreprise. Parce qu'à cette époque, on pensait que chaque entreprise avait besoin de fabrication, de fabrication de plaquettes, et c'était la partie la plus capitalistique d'une entreprise de semi-conducteurs, d'une entreprise de circuits intégrés. Et j'ai vu toutes ces personnes qui voulaient partir, mais qui ont été arrêtées par le manque de capacité à lever beaucoup d'argent pour construire une fabrique de wafers.

En 1985, Morris Chang était sur le point de prendre sa retraite, mais a plutôt accepté l'offre du gouvernement taïwanais de travailler à l'Industrial Technology Research Institute, un institut de recherche qui était censé aider à provoquer une révolution industrielle à Taiwan et à combler le fossé entre l'économie développée et les pays développés. En 1987, parallèlement à son travail chez ITRI, Chang a créé TSMC, une entreprise qui est devenue le plus grand fabricant de circuits intégrés au monde. Le modèle d'affaires de TSMC était à l'origine basé sur le fait que l'entreprise ne développait rien, mais ne produisait que les développements d'autres personnes, et ce fut l'une des premières étapes de la création d'un écosystème moderne pour le développement et la production de microcircuits, connu sous le nom de modèle Fabless.

La fin de la digression lyriqueQu'est-ce que Fabless?

Fabless est un modèle de développement et de production de microcircuits dans lequel la société de développement n'a pas sa propre production et utilise les services d'une usine tierce qui collabore également avec d'autres développeurs (et a parfois ses propres produits).

La présence d'usines tierces peut réduire radicalement le seuil d'entrée sur le marché de la microélectronique (dont Morris Chang avait rêvé à un moment donné), de centaines à des millions de dollars, en raison de l'absence de besoin d'acheter et de maintenir des équipements pour la production. Il permet également de réduire encore ce seuil grâce à la formation d'un marché pour les fournisseurs de blocs fonctionnels complexes (ils sont également Silicon IP). Si vous produisez des jetons dans votre propre usine, vous ne pouvez compter que sur vos propres forces et devez contenir une équipe capable de créer tous les blocs nécessaires. Si l'usine est utilisée non seulement par vous, mais aussi par d'autres entreprises, alors quelqu'un a déjà résolu la plupart des tâches typiques avant vous, et vous pouvez utiliser les résultats du travail de quelqu'un d'autre - ou revendre votre propre solution à quelqu'un d'autre, après avoir préalablement convenu du prix et des conditions afin que personne n'est resté dans le perdant. Bien sûr, il est peu probable que vous vendiez votre savoir-faire à des concurrents directs, mais il existe de nombreuses situations où vous pouvez gagner sans être impliqué dans un conflit d'intérêts. C'est par la possibilité et le désir de réutiliser les résultats de la résolution de problèmes typiques que le marché des blocs IP est apparu, dont la taille en 2017 était proche de quatre milliards de dollars et continue de croître rapidement.

Comment est-ce rentable?

IP de l'acheteur - principalement une économie. Selon diverses estimations, l'achat de blocs IP est généralement deux à cinq fois moins cher que l'auto-développement. En outre, l'achat vous permet généralement de réduire considérablement le temps de développement, car vous n'avez pas besoin de produire indépendamment des puces de test et de corriger les erreurs.

Pour le développeur IP - la possibilité de créer une entreprise qui fonctionne sur une solution de niche et de réduire considérablement le coût de faire des affaires. Une partie importante du coût du microcircuit est le coût du marketing, de l'emballage, des tests, du support technique, des logiciels d'application et enfin des modèles de photos pour la production de masse, etc. etc. Si vous ne produisez pas de produits finis, mais ne vendez que des blocs, vous n'avez pas toutes ces dépenses.

Usine - une opportunité pour attirer plus de clients. Les grandes usines s'efforcent de créer un écosystème de fournisseurs de blocs IP autour d'eux, car leur utilisation peut accélérer considérablement la conception et, tout aussi important, l'automatiser autant que possible. Un riche portefeuille de composants prêts à l'emploi est d'une grande aide dans la conception du produit final, car il vous permet de faire seul votre savoir-faire et de ne pas dépenser de précieuses ressources pour tout développer en général - en particulier dans une situation où il existe déjà une solution prête à l'emploi développée par des personnes qui a investi dans son développement beaucoup plus de temps et d'expérience que vous ne pouvez vous le permettre. En conséquence, une large sélection de PI prêts à l'emploi peut être un facteur sérieux dans le choix d'une usine particulière pour la production de votre projet.

Comment ça marche?

Examinons la licence des cœurs en utilisant l'exemple d'un système personnalisé sphérique sur une puce. Le système contiendra un cœur de processeur, des bus pour combiner le cœur et les périphériques, une certaine quantité de mémoire cache, des interfaces pour communiquer avec le monde extérieur (par exemple CAN et I2C), PLL, DAC et ADC. Pour la pureté de l'expérience, supposons que tout sera acheté, sans développement indépendant. «Hypothèse stupide», dites-vous, et vous n'aurez pas tout à fait raison. En réalité, bien sûr, de telles situations sont extrêmement rares, mais il est tout à fait possible d'imaginer que la caractéristique de tueur du produit ne sera pas un bloc en soi, mais une combinaison spécifique de blocs existants. Par exemple, vous êtes le premier acheteur d'un bloc (par conséquent, les concurrents ne l'ont pas déjà) ou vous avez créé un bloc existant à utiliser dans un segment qui ne lui est pas caractéristique (par conséquent, les concurrents de ce segment n'ont rien de similaire).

Commençons donc par ...

... non, pas du cœur du processeur, mais de la liaison analogique. Par exemple, prenez le convertisseur analogique-numérique (ADC) - une unité typique de la plupart des microcontrôleurs et de tout autre système qui traite des données du monde extérieur.

L'ADC est un bloc analogique, ce qui signifie que ses paramètres dépendent sérieusement non seulement de ses circuits, mais également de la façon dont ces circuits sont mis en œuvre sur une puce. Si nous prenons le fichier fini avec la topologie d'un processus technique et le produisons dans une autre usine avec les mêmes normes de conception, nous pouvons obtenir des paramètres complètement différents (sans parler du transfert vers d'autres normes de conception). Cependant, la culture des «seconds fournisseurs», connue depuis le milieu du siècle, existe toujours; par exemple, l'usine Towerjazz propose des copies de certains processus de fabrication TSMC.

L'ADC est un excellent exemple de bloc IP dur lié à un processus spécifique. Pour acheter une telle unité, vous devez savoir exactement sur quelle technologie votre produit final sera fabriqué et, comme mentionné ci-dessus, la disponibilité du Hard IP nécessaire peut être un sérieux avantage concurrentiel pour l'usine.

Comment est livré Hard IP? C'est une question intéressante, et pour y répondre, il est nécessaire de discuter sous quelle forme un tel bloc est développé. Dans le cas de la plupart des blocs analogiques, le développement des circuits s'effectue au niveau des transistors individuels, c'est-à-dire que les fichiers de sortie seront le fichier du circuit électrique et le fichier avec la topologie. De plus, les caractéristiques du schéma et de la topologie peuvent avoir une valeur commerciale sérieuse, ce que, bien sûr, je ne veux pas donner de côté. Et pour que le client ne puisse pas effectuer de rétro-ingénierie du schéma par topologie, la topologie n'est généralement pas non plus transmise.Par conséquent, dans le cas habituel, les fichiers livrés ressemblent à ceci:

- Au lieu d'un circuit électrique, le client reçoit un modèle comportemental de haut niveau qui ne révèle pas les fonctionnalités de mise en œuvre. Un tel modèle peut être écrit en Verilog-A. Une alternative est que certains systèmes de CAO (par exemple, Cadence Virtuoso) prennent en charge le cryptage des circuits électriques, c'est-à-dire que le client pourra utiliser votre circuit (ou le fichier verilog-A), mais ne pourra pas ouvrir et afficher le contenu.

- Disposition dimensionnelle de la topologie, avec des conclusions externes marquées et une description du nombre de niveaux de métallisation qu'un bloc occupe.

- Environnement de test pour la vérification des principaux paramètres.

- La documentation

Dans ce cas, bien sûr, la participation d'un tiers est nécessaire, à laquelle vous pouvez transférer la topologie sans crainte de concurrence et de rétro-ingénierie. Ce tiers est l'usine et son rôle d'intermédiaire entre les clients et les sous-traitants est un élément important de l'écosystème de développement de puces sans usine. L'usine, bien sûr, devrait avoir une réputation limpide (il s'agit de signets) et, idéalement, elle ne devrait rien produire de semblable à elle seule, car travailler dans une usine d'une entreprise concurrente est en tout cas un plaisir douteux. Samsung réussit à produire des processeurs en même temps pour lui-même et Apple, mais d'autres grandes usines se concentrent généralement sur leur propre production (comme Intel) ou abandonnent complètement l'auto-développement (comme TSMC). La volonté de se débarrasser de ce conflit d'intérêts a d'ailleurs été l'un des moteurs de l'attribution d'AMD à Globalfoundries (le deuxième acteur sur le marché des usines).

Digression lyriqueSoit dit en passant, en Russie, il n'y a pas d'usines de jeu pur en Russie. De plus, pour absolument tous les acteurs du marché, la production de leurs propres produits est une priorité, et toutes les puces entièrement nationales produites par des développeurs sans usine sont fabriquées dans les installations de leurs concurrents potentiels - ou dans des usines pure play à l'étranger.

La fin de la digression lyriqueDe plus, il y a un autre détail important de l'interaction fournisseur-usine: l'usine entre votre bloc IP dans sa propre base de données et vérifie en outre tous les projets entrants pour la présence de votre topologie (que quelqu'un pourrait obtenir de vous aussi bien qu'illégalement), et vérifiez avec vous si la personne qui demande la production a une licence (car de nombreuses licences bon marché impliquent l'utilisation de l'unité dans un seul projet). La présence d'un chèque par l'usine permet au développeur Hard IP de choisir n'importe quelle option de licence pratique - liée au nombre de projets, au nombre de puces vendues, au moment du lancement des puces en production, etc. etc. Mais plus sur les types de licences dans la partie suivante.

Comme Hard IP dans un système typique sur une puce, vous aurez besoin d'ADC, de PLL, de couches physiques d'interfaces d'E / S.

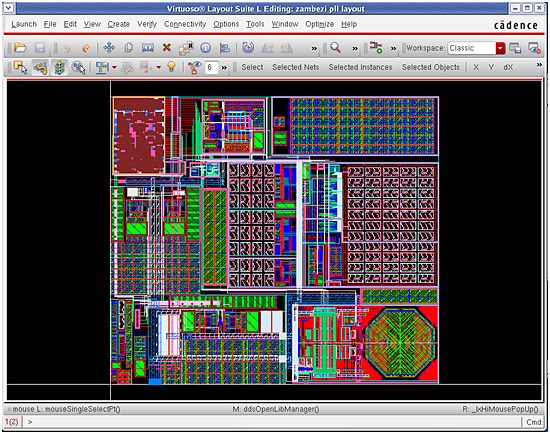

Fenêtre CAD Cadence Virtuoso Layout Suite avec la topologie du bloc IP dur analogique (c'est PLL, si quelqu'un est intéressé). Les limites entre les sous-unités individuelles (qui sont généralement faites par des personnes différentes) et, par exemple, un élément très rare pour les circuits intégrés - l'inductance dans le coin inférieur droit, sont clairement visibles. Et en haut à gauche se trouve un bloc numérique (probablement de contrôle) et son interface multi-bits pour le reste.

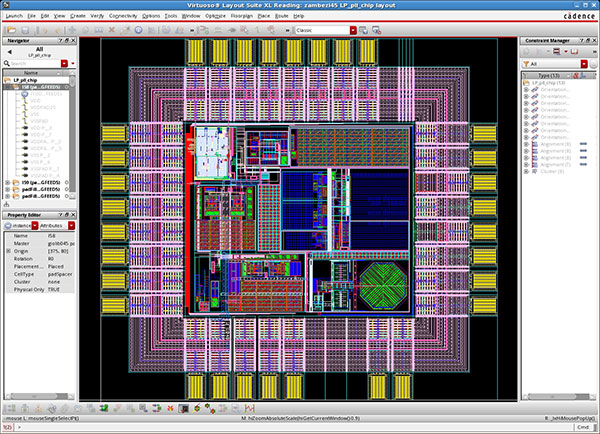

C'est la même chose, mais déjà sous la forme d'une puce finie (par exemple, pour les tests). Les borniers d'E / S et les anneaux les reliant aux terrains et aux fournitures sont clairement visibles.

Le terme «Hard IP» est également utilisé en relation avec les blocs IP pour FPGA. Dans ce cas, il est entendu que le code de bloc a été optimisé pour être utilisé dans un modèle FPGA particulier et synthétisé pour y être placé.

IP souple

Le prochain bloc que nous considérerons est le cœur du processeur. En fait, presque n'importe quel circuit numérique peut être à sa place, par exemple, une unité de codage de signal avec un code Reed-Solomon, mais les cœurs de processeur sont les plus largement entendus et ils représentent une bonne moitié de l'ensemble du marché (y compris en raison de la complexité et du coût élevé).

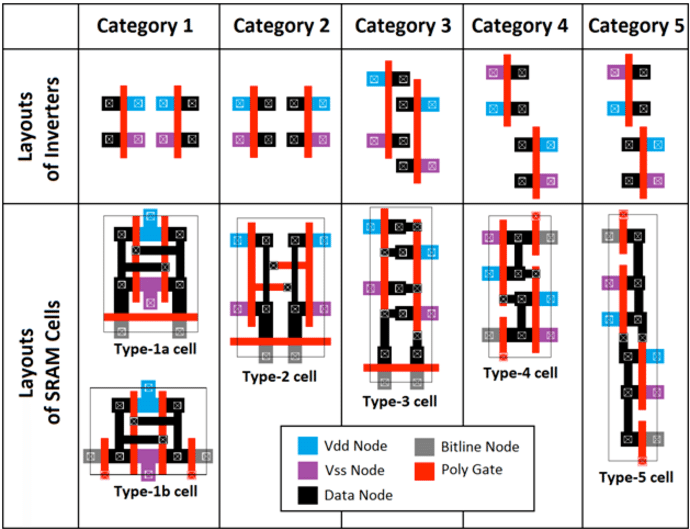

La principale différence entre le développement de circuits numériques et le développement de circuits analogiques est que les circuits numériques sont généralement écrits dans des langages spéciaux de haut niveau - Verilog ou VHDL, puis un système de CAO spécial synthétise le circuit électrique et la topologie à partir de ce code. Ainsi, jusqu'au moment de la synthèse, le code n'est pas lié à une technologie spécifique, et le même bloc peut être produit dans différentes usines (ou cousu dans le FPGA) ou dans différentes versions de la même technologie (par exemple, optimisé pour une vitesse élevée ou une faible consommation d'énergie) . En fait, cela est utilisé par des sociétés de développement, comme, par exemple, ARM. Ces blocs numériques qui ne sont pas liés à une technologie spécifique sont appelés Soft IP.

Voici le schéma d'un bit additionneur:

Et voici à quoi ressemble un additionneur huit bits dans une conception de puce:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .