La taille des transistors dans les microcircuits modernes diminue inexorablement - malgré le fait qu'ils parlent de la mort de la loi de Moore depuis plusieurs années, et que la limite physique de la miniaturisation est déjà proche (plus précisément, elle a déjà été contournée avec succès à certains endroits). Cependant, cette diminution n'est pas vaine et l'appétit des utilisateurs croît plus vite que les capacités des développeurs de puces. Par conséquent, en plus de la miniaturisation des transistors, d'autres technologies souvent non moins avancées sont utilisées pour créer des produits microélectroniques modernes.

Dans ma dernière phrase, j'ai délibérément utilisé l'expression «produit microélectronique» au lieu du mot «microcircuit», car cet article se concentrera sur le fait qu'à l'intérieur du boîtier du CPU ou du GPU, il peut y avoir non pas un cristal, mais tout un système de plusieurs puces, donc et appelé: un système dans un package ou un système dans un package.

Le terme «système dans un boîtier» est beaucoup moins connu que le terme connexe «système sur puce», que les développeurs aiment tromper avec n'importe quoi. De plus, maintenant presque toutes les puces (à l'exception des plus simples) sont en quelque sorte un système sur une puce, et l'époque des jeux de microprocesseurs et même des puces individuelles des ponts sud et nord appartient au passé. Les avantages des systèmes sur puce sont assez évidents: moins de boîtiers sur la carte, moins de surface (et donc moins cher), moins d'inductances et de capacités parasites (ce qui signifie que le produit fonctionnera mieux et plus rapidement), plus facile pour l'utilisateur (plus pratique à mettre en œuvre et moins d'espace pour l'erreur), moins cher en production (au lieu de plusieurs microcircuits spécialisés, un plus universel peut être produit).

Mais les systèmes sur puce ont aussi leurs pièges.

Premièrement, lorsque vous essayez de tout pousser sur un seul cristal à la fois, vous courez le risque d'obtenir une puce d'une telle taille (et avec tellement de pattes) qu'elle ne rentrera dans aucun cas. De plus (comme le suggère un technologue professionnel dans les commentaires), une très grande puce risque de ne pas entrer dans la taille du champ du scanner photolithographique. Vous pouvez contourner cette limitation, mais elle est très difficile techniquement et, par conséquent, très coûteuse.

Deuxièmement, plus la taille de la puce est grande, plus le pourcentage de rendement est faible, surtout si pour la production, vous devez assembler plusieurs fenêtres sur un masque photo. Et cela, bien sûr, affecte également le coût.

Troisièmement, si votre système est composé de composants hétérogènes, les combiner tous sur une seule puce peut être trop difficile, trop cher ou trop mauvais pour la qualité du système. Par exemple, la DRAM nécessite des condensateurs spéciaux, les ajouter à un processus de fabrication «normal» peut être déraisonnablement cher pour l'usine (qui, de ce fait, sera obligée d'augmenter les prix pour les clients). Les composants de radiofréquence ou de puissance sur le silicium peuvent avoir des paramètres bien pires que sur les matériaux A3B5 (arséniure de gallium et ses analogues), et la connexion des pièces numériques et analogiques sur le même cristal crée un problème de bruit.

La combinaison de tous les facteurs mentionnés ci-dessus a conduit au fait que la tendance «mettre tout-en-un sur un cristal» a été remplacée par une approche plus équilibrée, ainsi que par le développement rapide de technologies pour l'emballage des cristaux dans un boîtier.

Performance et rendement

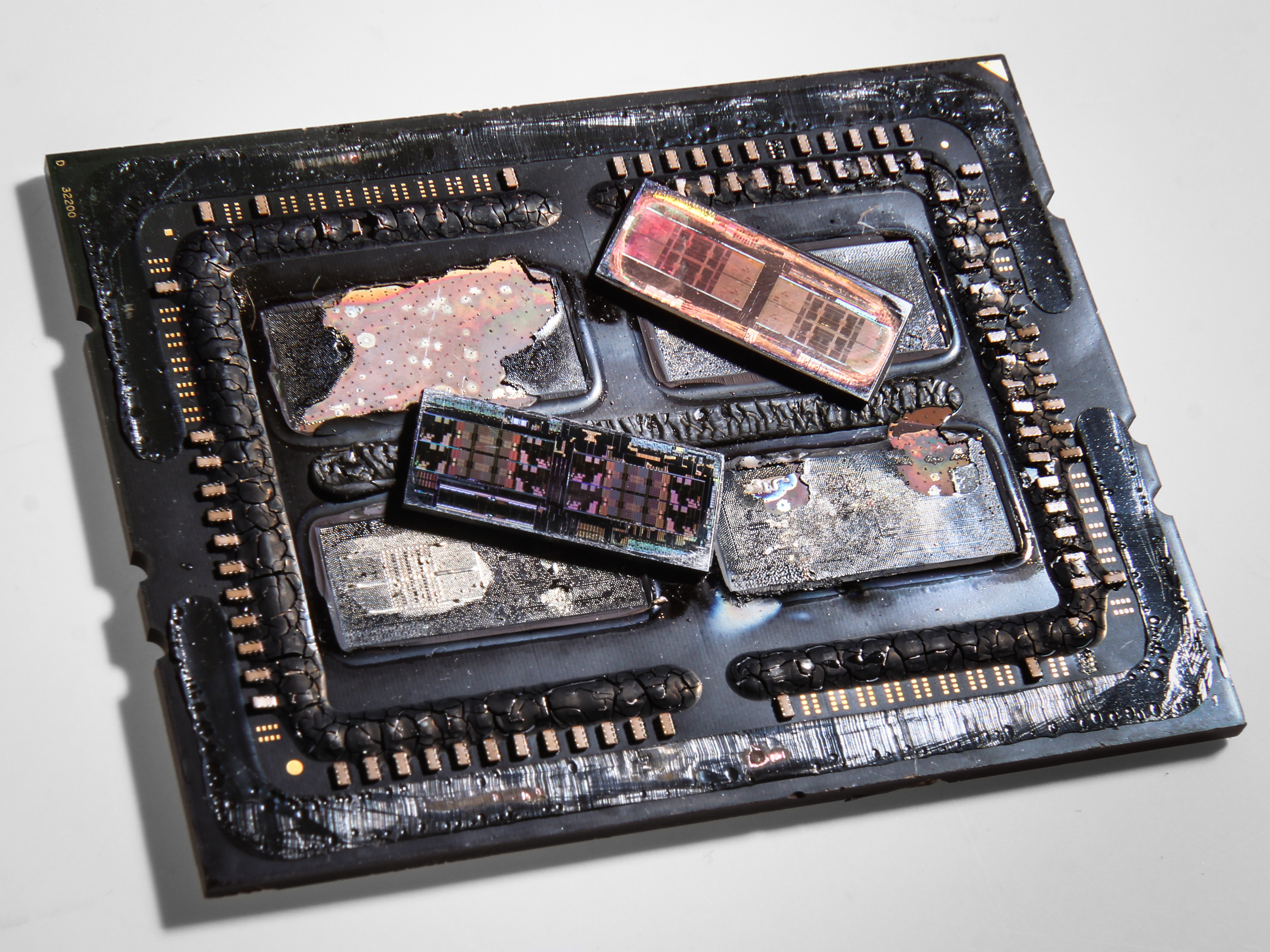

Le premier exemple qui me vient à l'esprit est, bien sûr, les microprocesseurs AMD (voir KDPV). Les systèmes dans le cas des produits multicœurs sont considérés comme l'une des raisons importantes de la récente montée en puissance de la société, sur fond de problèmes Intel avec le lancement d'un nouveau processus technique en raison du faible rendement des énormes puces.

La figure montre une puce Intel Xeon à 28 cœurs. La taille de ces processeurs atteint 456 millimètres carrés, tandis que la taille maximale des puces AMD est d'environ 200 millimètres carrés pour une puce à huit cœurs, et les produits avec plus de cœurs sont assemblés à partir de plusieurs cristaux identiques sur une carte de circuit imprimé à deux couches située dans le boîtier du processeur.

Sur cette figure, vous pouvez voir la conception de la carte à l'intérieur du boîtier des processeurs EPYC et Threadripper (alias KDPV). Quatre cristaux à huit cœurs sont situés sur une carte à deux couches. Dans le cas de Threadripper, avec la moitié des cœurs désactivés. Pourquoi les cristaux sont-ils si irrationnellement utilisés?

Tout d'abord, produire un type de cristal peut être moins cher que plusieurs autres.

Deuxièmement, il en va de même pour le reste du faisceau - la désactivation inutile peut être moins coûteuse et plus technologique que le développement et la production de plusieurs modèles différents.

Troisièmement, le pourcentage de rendement approprié pour une puce de 200 millimètres, très probablement, n'est pas non plus idéal, et une telle conception du produit final permet l'utilisation de cristaux dans lesquels tous les noyaux ne fonctionnent pas. Intel fait exactement la même chose, mais leurs problèmes de sortie sont beaucoup plus importants en raison de cristaux plus gros.

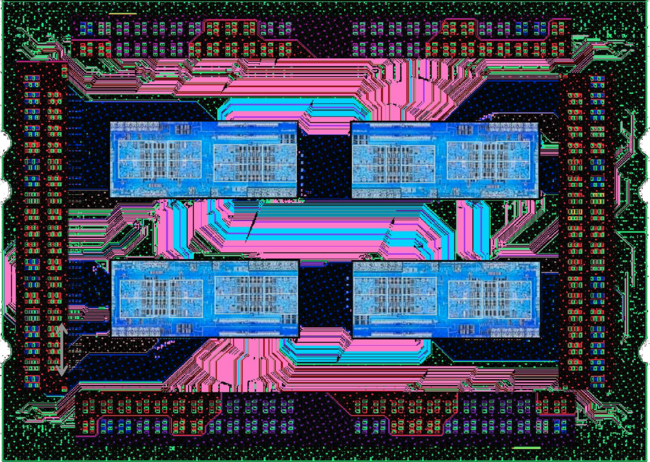

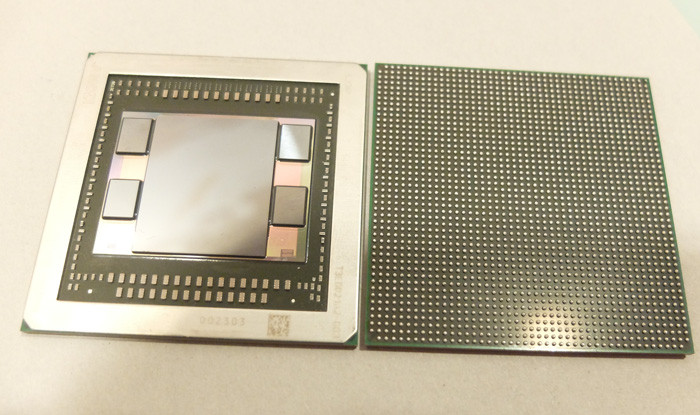

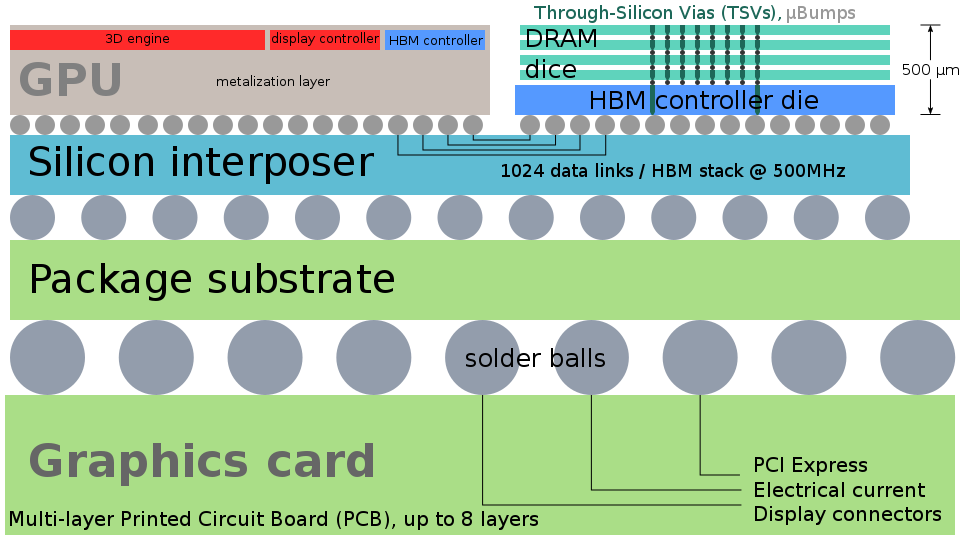

Et voici un exemple encore plus intéressant, également d'AMD. AMD Fiji est un GPU avec mémoire haute vitesse intégrée située directement dans le châssis. Pourquoi est-ce important? Parce que des lignes beaucoup plus courtes du processeur à la mémoire permettent d'atteindre des vitesses élevées et donc des performances supérieures. Contrairement à l'exemple précédent, les cristaux à l'intérieur du boîtier sont différents. De plus, il n'y en a pas cinq, comme cela peut sembler à première vue, mais bien plus - vingt-deux. Voici une section de la structure:

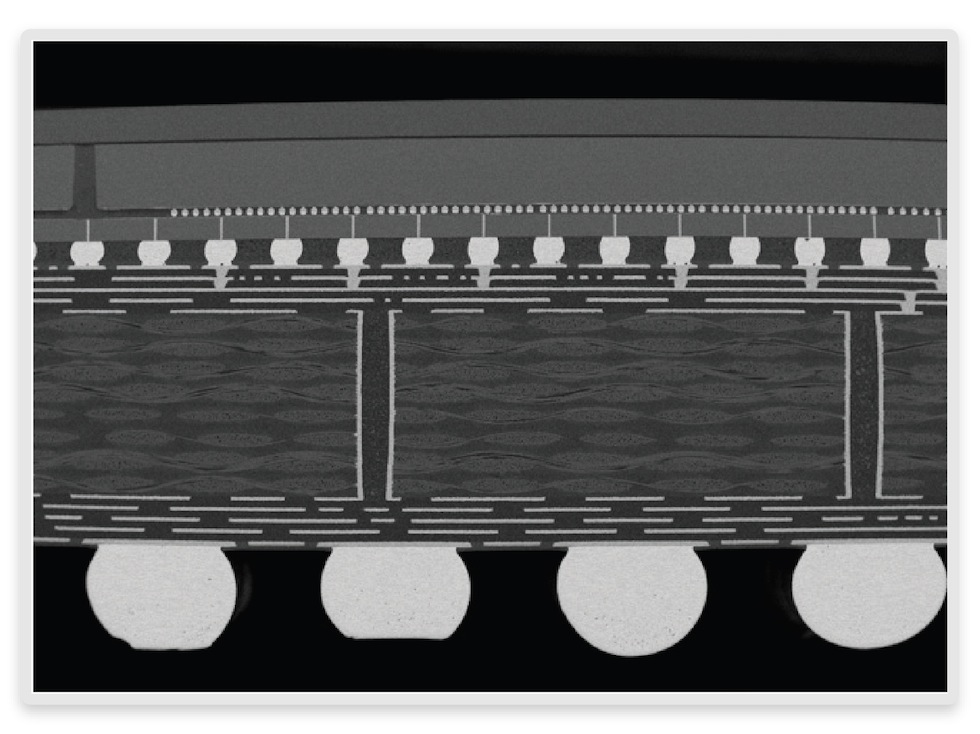

La couche supérieure est la puce GPU elle-même et la «tablette» de plusieurs (dans ce cas, quatre) puces de mémoire connectées à l'aide de TSV (via-silicium-via) - des colonnes conductrices qui traversent le cristal sur toute l'épaisseur.

Les TSV ressemblent à ceci, schématiquement et à l'échelle réelle.

La technologie TSV, qui est apparue à l'origine uniquement pour les matrices de mémoire (après tout, il n'y a jamais trop de mémoire, non?), Est désormais de plus en plus répandue, notamment grâce à la prochaine puce située sous le GPU et la mémoire.

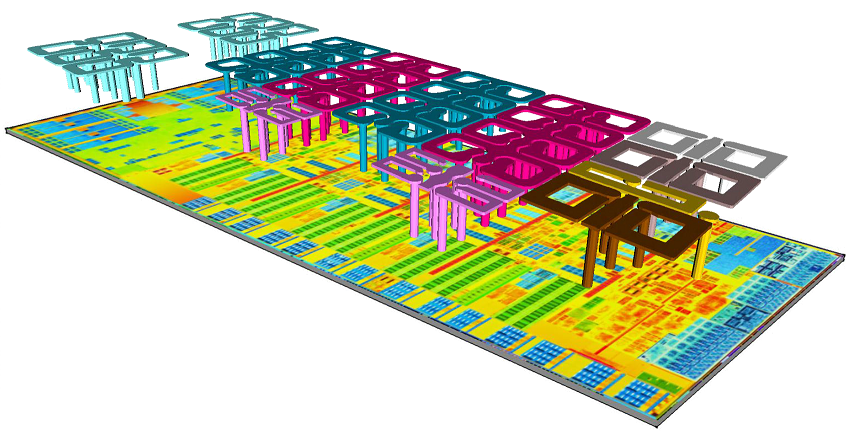

Silicon Interposer est un substitut pour une carte de circuit imprimé multicouche composée d'un cristal de silicium et contenant plusieurs couches de métallisation et TSV pour connecter les puces en haut et le boîtier. L'utilisation de silicium permet d'obtenir des tailles d'éléments (unités de microns) nettement plus petites qu'une carte de circuit imprimé, mais en même temps, les normes de conception peuvent être assez rigoureuses pour que cette puce de connexion ait un rendement élevé et un prix abordable. Les dimensions plus petites des éléments signifient moins d'influence des paramètres parasites des connexions, et les TSV déjà mentionnés sont beaucoup plus compacts que les vias sur la carte de circuit imprimé et permettent à des centaines voire des milliers de contacts d'être transportés à travers l'interposeur vers le boîtier. Avec les MEMS, ces puces d'interconnexion sont un nouveau marché important pour les usines obsolètes avec des plaquettes de 100 à 150 millimètres de diamètre.

Un autre pionnier de l'intégration 3D est Xilinx. Technologiquement, ses FPGA sont proches des produits AMD (en particulier ceux avec mémoire intégrée), et les motivations sont également similaires: les FPGA sont un créneau du marché où une transition précoce vers un nouveau processus de fabrication peut donner un sérieux avantage sur ses concurrents. Selon diverses estimations, à un stade précoce de la vie d'une technologie, la réduction de la taille des cristaux de trois à quatre fois peut augmenter le rendement de deux à trois fois, de quelques dizaines de pour cent à plus de la moitié. De plus, les FPGA sont une structure régulière sur laquelle il est pratique de suivre les défauts technologiques. Par conséquent, les fabricants de FPGA sont des «premiers clients» typiques pour les nouveaux processus de fabrication, et Xilinx, du fait que leurs produits contiennent plusieurs petits cristaux au lieu d'un en taille réelle, peut lancer de nouveaux modèles plusieurs mois plus rapidement que ses concurrents.

Voici une coupe transversale de l'intérieur du FPGA Xilinx. La puce supérieure fait en fait partie du FPGA avec de très petits contacts (40-45 microns) avec l'interposeur connectant plusieurs puces ensemble, et en bas se trouve la base du boîtier, qui a une douzaine de couches de ses propres interconnexions métalliques.

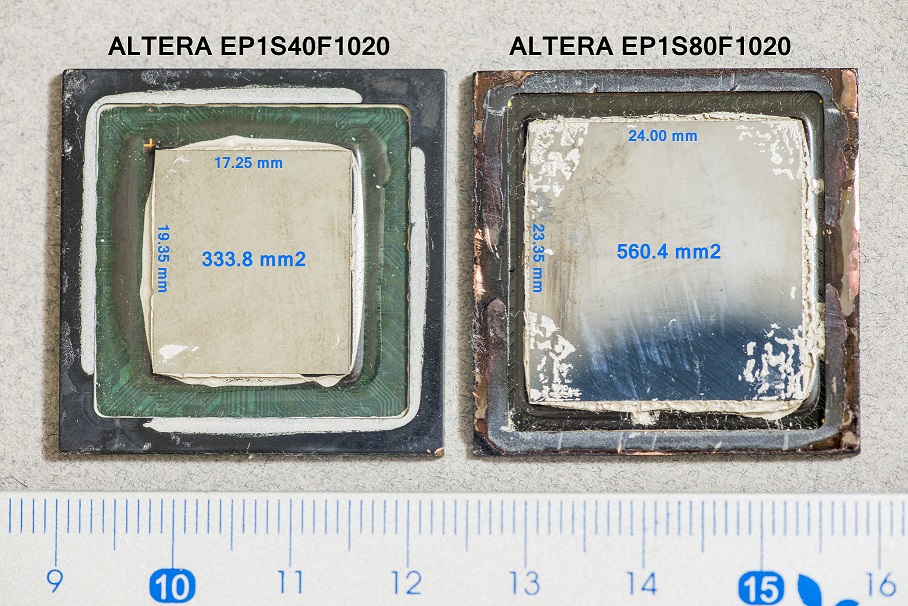

A titre de comparaison - FPGA Altera sur un énorme cristal. Cinq cent soixante millimètres carrés, Carl! Si soudainement ce poste est lu par des technologues en production microélectronique, assurez-vous qu'ils n'ont pas de crise cardiaque.

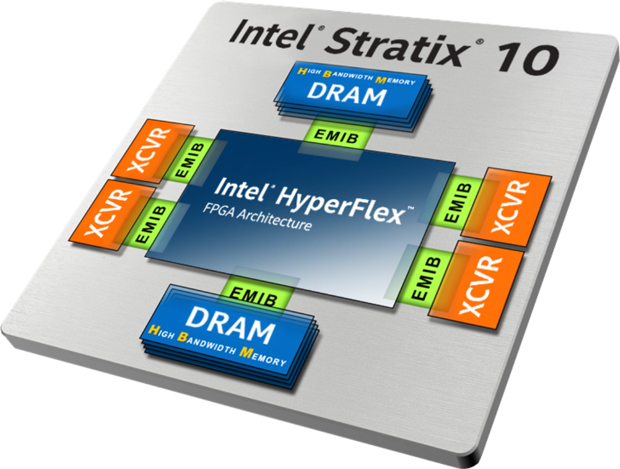

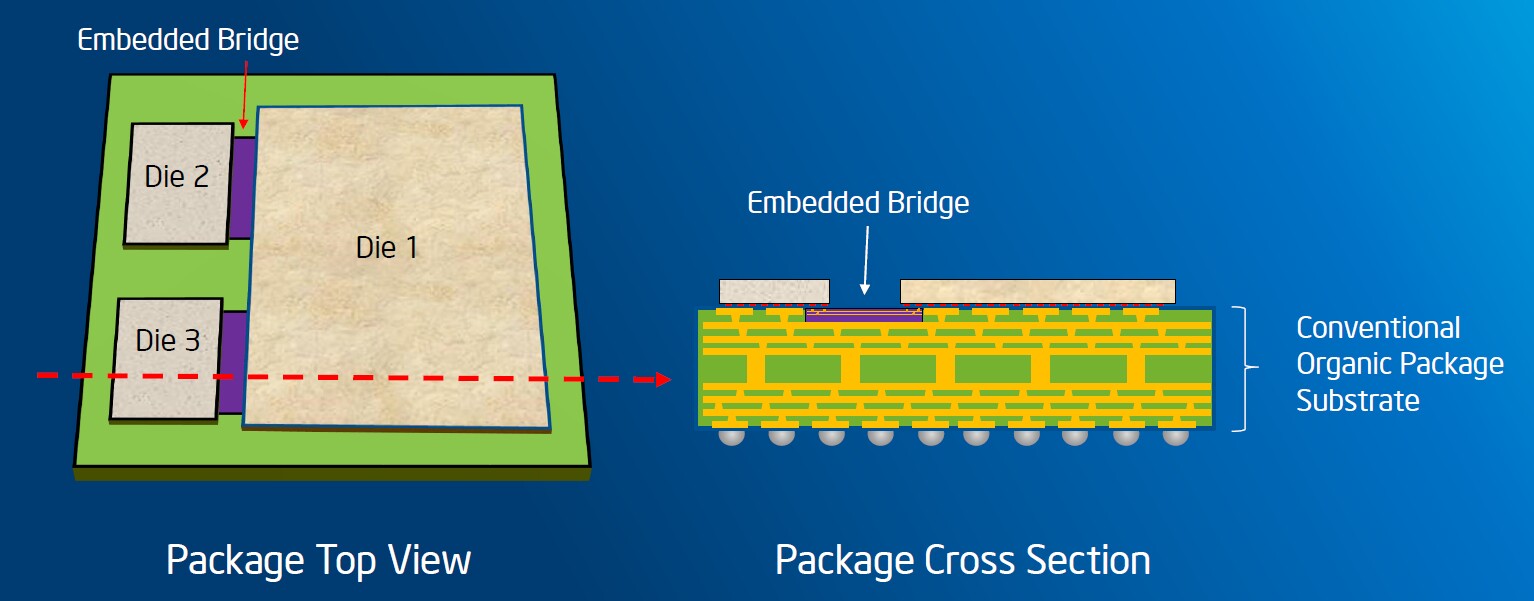

Cependant, Intel / Altera, bien sûr, ne reste pas immobile, observant le succès de ses concurrents. Leur dernier développement dans les systèmes fermés est le pont d'interconnexion multi-puces intégré (EMIB). Il est pratique de le regarder en utilisant le FPGA Intel Stratix 10.

Comme vous pouvez le voir, EMIB interconnecte (un!) Puce FPGA, mémoire (et ici structures à plusieurs étages) et cristaux périphériques. Alors, quel est cet EMIB? Un peu plus haut, j'ai écrit sur l'interposeur de silicium qu'en raison d'un processus technique plus difficile, il a un prix beaucoup plus bas qu'une puce de taille similaire fabriquée à l'aide d'une technologie mince. Néanmoins, l'interposeur est énorme. Est-il possible de le réduire?

La réponse d'Intel est oui. L'idée d'EMIB est d'utiliser plusieurs petits au lieu d'un grand interposeur et, à son tour, de les intégrer directement dans le substrat corporel.

Voici une petite sélection de produits créés à l'aide d'interposeurs en silicium. Faites attention à leurs dimensions colossales selon les normes microélectroniques et au fait que, comme nous l'avons vu ci-dessus, les puces de combat de Xilinx sont divisées en plusieurs petits morceaux.

Plus que de simples performances.

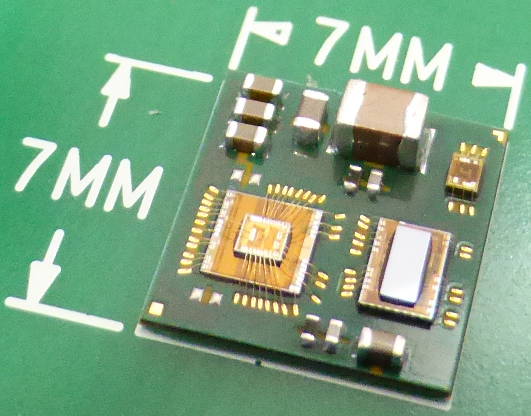

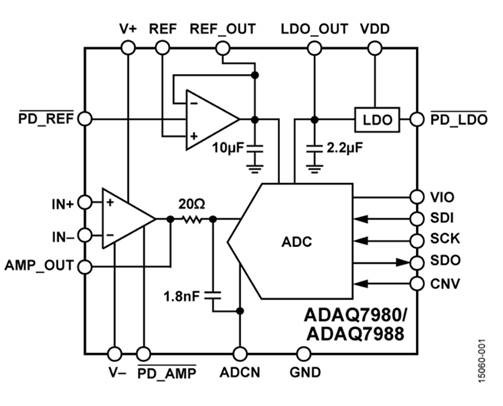

La figure ci-dessous montre l'intérieur d'un boîtier ADC Analog Devices et un schéma de circuit. Cela ressemble à une carte de circuit imprimé complètement ordinaire pour l'ADC, seulement plus petite, non? C'est vrai, c'est ça, seulement en raison de l'utilisation de composants à cadre ouvert, les erreurs associées aux éléments parasites ont été réduites, et le fait que la carte est développée dans Analog Devices leur permet de gagner beaucoup de temps client et en même temps être sûr que l'utilisateur ne se trompe pas en choisissant les mauvais composants ou carte mal câblée.

Cependant, il y a une petite astuce dans la figure ci-dessus: voir des cristaux posés sur deux étages? Le cristal supérieur est une puce avec les composants actifs de l'ADC lui-même et (apparemment) un amplificateur opérationnel double, et le cristal inférieur est les composants passifs (condensateurs et résistances). L'exécution sur un cristal séparé vous permet de les rendre beaucoup plus grands (et donc de réduire les erreurs) sans augmenter (et donc augmenter le coût) du cristal principal.

Tout cela peut être fait sur une seule puce (ce qui, en fait, n'est pas rare, en particulier pour les ADC intégrés dans les microcontrôleurs), mais une telle puce sera beaucoup plus grande (ce qui signifie, comme nous l'avons découvert, il y a un risque de diminuer le pourcentage d'utilisation), et la technologie pour lui devra prendre en charge toutes les options supplémentaires nécessaires. De plus, la combinaison de différents blocs sur le même cristal entraînera la nécessité de s'assurer qu'ils ne s'influencent pas mutuellement (par exemple, se débarrassent en quelque sorte du bruit sur le substrat cristallin).

Caractéristiques supplémentaires du boîtier

Comme nous l'avons déjà découvert, l'emballage d'éléments dissemblables (y compris les composants CMS passifs) dans un seul boîtier vous permet de réduire considérablement les dimensions du produit final et même d'augmenter sa vitesse. Mais que se passe-t-il si nous utilisons le boîtier lui-même comme élément fonctionnel de l'appareil?

En 2013, les processeurs Intel (microarchitecture Haswell) ont mis en œuvre un régulateur de tension intégré (FIVR - régulateur de tension entièrement intégré), dans lequel la partie active du régulateur a été implémentée sur la puce du processeur, et la partie passive (condensateurs et inductances) a été intégrée dans le boîtier.

L'inductance intégrale est un casse-tête pour tous les développeurs de puces, car les bobines sur la puce sont obtenues non seulement avec les meilleurs paramètres, mais aussi énormes (ce qui signifie qu'ils sont très chers, en particulier avec les technologies minces). Et il s'agit de bobines de signal sans noyau, il n'est pas question de transmission de puissance. Intel a réussi à contourner ce problème en intégrant des dizaines de petites bobines parallèles fonctionnant à une fréquence de 160 MHz dans le boîtier du microprocesseur. Ils ont ainsi pu considérablement simplifier les besoins en énergie du microprocesseur.

Cependant, quelque chose s'est mal passé avec ce développement, et il n'y avait plus de processeurs Intel FIVR dans la prochaine génération de processeurs Haswell. Depuis lors, il y a eu des rumeurs selon lesquelles ils retourneraient à la FIVR, mais jusqu'à présent, ils sont restés des rumeurs.

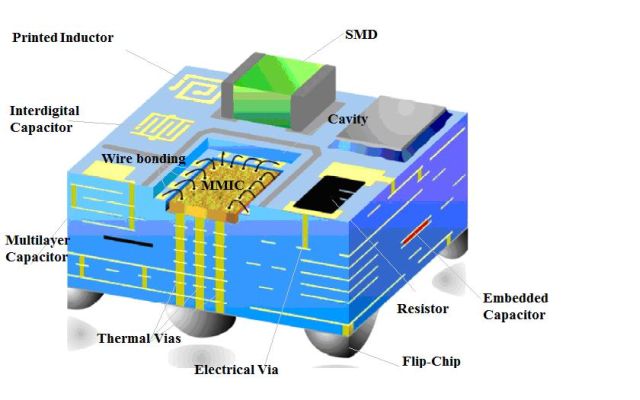

Cependant, même sans Intel, le sens d'intégration des composants passifs dans le boîtier se développe activement, par exemple dans les boîtiers de type LTCC (céramique basse température). Là, bien sûr, il y a des limites et des pièges (associés, par exemple, à l'exactitude des notations), mais cette technologie est en demande et se développe activement. Le boîtier LTCC en couches ressemble à ceci:

La figure montre tous les types d'éléments passifs réalisés en céramique multicouche, et même un dissipateur thermique en métal (c'est le cas pour un circuit hyperfréquences puissant). En fait, c'est un mélange du boîtier avec une carte de circuit imprimé en céramique. Ces pièces sont très populaires pour les modules RF, et elles sont également relativement bon marché dans la production à petite échelle.

Quoi d'autre?

Il y a beaucoup d'applications potentielles pour les systèmes dans le cas, et il est presque impossible de les énumérer toutes; en outre, quelque chose de nouveau fait constamment son apparition, notamment du fait que ces technologies sont beaucoup plus abordables que les transistors 10-7-5-3 nanomètres.

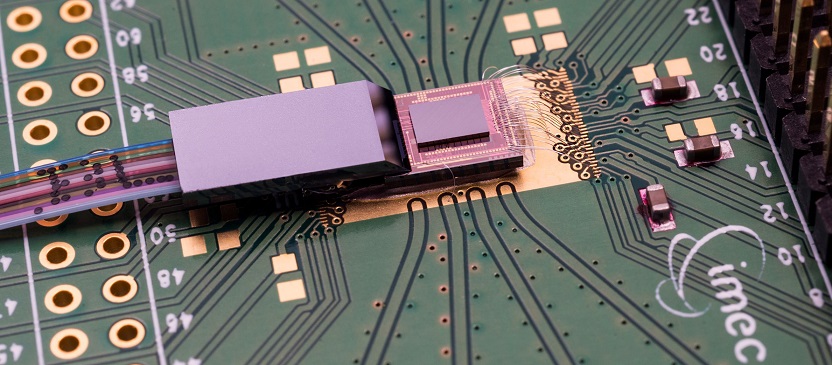

Un bon exemple des nouvelles applications et propriétés qu'ouvre l'intégration de puces hétérogènes dans un seul boîtier est une variété de systèmes optiques où le SiP vous permet d'assembler un récepteur ou un émetteur (généralement fabriqués sans silicium), ainsi que leurs circuits d'alimentation et de contrôle. Dans l'illustration ci-dessous - un prototype de lien optique à 400 Gb / s (et promesse avant térabit), assemblé à l'institut de recherche belge IMEC.

En outre, des applications en perspective telles que des systèmes dans le cas envisagent des éléments tels que des interpozers avec des capillaires intégrés pour le refroidissement liquide (non seulement des processeurs de jeu, mais également des touches d'alimentation et des lasers), des unités MEMS intégrées dans le cas, et bien plus encore pas dans le cadre étroit de la loi de Moore. En outre, l'Internet des objets omniprésent est considéré comme un marché important pour les systèmes dans le cas où les petites tailles, l'absence de pertes (principalement d'énergie, pas de temps) sur les éléments parasites et la capacité d'intégrer des composants passifs, par exemple, des parties du chemin radio, dans le microcircuit sont importants.