La semaine dernière, Intel a annoncé l'acquisition d'eASIC, qui développe des outils de développement basés sur FPGA pour des «ASIC structurels». Les ASIC structurels sont un croisement entre les FPGA conventionnels et les ASIC conventionnels; ils vous permettent de réduire le temps de commercialisation du produit et de réduire son coût.

Intel utilise la technologie eASIC

depuis 2015 dans des versions personnalisées des processeurs Xeon; eASIC (120 personnes) fera désormais partie du Intel Programmable Solutions Group (PSG).

Même ceux qui, il y a longtemps, se sont «fait des amis» du FPGA et de l'ASIC ne refusent pas d'expliquer ce que sont les «ASIC structurels». La puissance de calcul de l'ordinateur n'est pas limitée au CPU ou au GPU, il existe d'autres classes de processeurs, comme par exemple le FPGA - ils sont développés par Altera, acquis par Intel. Dans les FPGA, des millions de portes peuvent être programmées de manière flexible pour implémenter les fonctionnalités requises. En fait, la plupart des CPU et GPU sont initialement simulés sur des FPGA pour tester les performances. Les FPGA sont un moyen simple de modéliser des circuits d'interconnexion, et leur portée est large. Les FPGA peuvent également contenir des unités matérielles standard, telles que des cœurs ARM ou des émetteurs-récepteurs pour les communications externes.

Un autre exemple est l'ASIC (Application Specific Integrated Circuit), une puce conçue pour effectuer un ensemble de tâches bien défini. L'ASIC est optimisé au maximum pour ses tâches et la logique de son travail ne peut pas être modifiée. Souvent, le CPU et le GPU sont classés comme ASIC dans le sens où leur microarchitecture est également fixe, mais ils sont conçus pour résoudre une variété de problèmes et sont universels, tandis que les ASIC sont créés pour des types de calculs clairement définis. Caractéristiques de l'ASIC: ils sont rapides, économiques, mais relativement coûteux et difficiles à fabriquer.

Les ASIC structurels d'EASIC peuvent être appelés une solution en demi-teinte. Les ingénieurs créent un prototype en utilisant FPGA, mais ne perdent pas de temps à optimiser ses circuits, mais fabriquent une puce avec une architecture fixe sur la base. Pour cette raison, il fonctionne plus rapidement qu'un échantillon avec des blocs personnalisés, même s'il perd les avantages de l'efficacité énergétique. Cependant, le temps pour son développement est comparable au FPGA, pas à l'ASIC - il économise jusqu'à 6 mois. La contribution d'eASIC est que l'optimisation de la couche monocouche est utilisée pour remplacer le routage SRAM par un système de bout en bout, ce qui réduit considérablement les coûts de production. eASIC fournit également des bibliothèques de cellules fixes, également monocouches, ce qui réduit encore la consommation, la taille des cristaux et les délais de commercialisation. En outre, les concepteurs peuvent ignorer les procédures standard lors de la création d'ASIC, telles que l'équilibrage de la synchronisation, l'analyse de l'intégrité du signal, le test d'atténuation de la puissance, etc. Ainsi, les «ASIC structurels» peuvent être décrits comme des FPGA qui ne peuvent pas être programmés davantage, qui ont les meilleures qualités des FPGA et des ASIC.

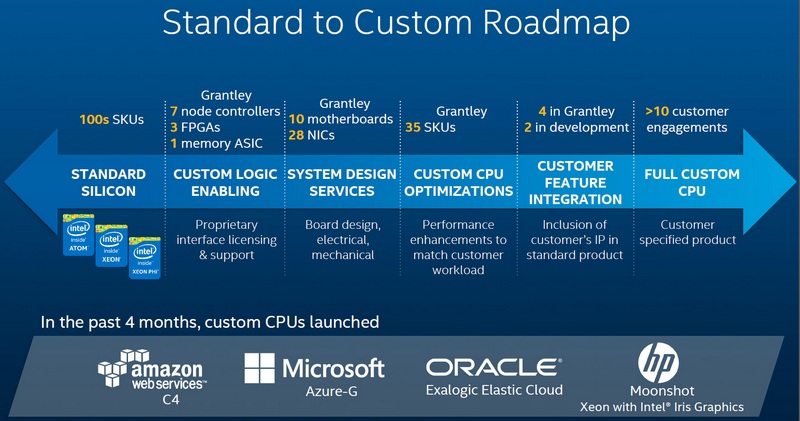

Le graphique montre la situation actuelle et les perspectives dans le domaine des processeurs Intel Xeon personnalisés

Le graphique montre la situation actuelle et les perspectives dans le domaine des processeurs Intel Xeon personnalisésIntel a besoin de la technologie eASIC pour intégrer une logique programmable dans les processeurs Xeon afin d'améliorer les performances, la consommation d'énergie et le prix. Parallèlement au Xeon standard, Intel propose désormais des options personnalisées à ses principaux clients. Comme nous pouvons le voir sur le diagramme, la profondeur de personnalisation augmentera. Avec l'acquisition d'eASIC, ce processus va s'accélérer et se développer. Il semble que l'approche «CPU as ASIC» puisse nous apporter beaucoup de choses intéressantes.