1. Introduction

Nous connaissons tous le problème du poulet et des œufs: les employeurs ne veulent pas embaucher des diplômés sans expérience de travail, mais où, alors, les diplômés peuvent-ils acquérir une expérience de travail? En microélectronique, ce problème est particulièrement aigu compte tenu de l'énorme expérience spécifique requise. Depuis l'époque soviétique, nos universités sont réputées pour la formation théorique la plus large, qui devrait aider le diplômé dans toute situation difficile de la vie. Cependant, l'industrie moderne nécessite une expérience pratique. Nous ajoutons ici le manque de motivation, qui conduit au fait que 15% des diplômés travaillent dans la spécialité, et nous constatons la pénurie de personnel la plus sévère de l'industrie, qui est très exigeante sur la qualité du personnel. Mais si chaque élève pouvait «faire clignoter une ampoule» de son propre cristal, la situation pourrait évoluer d'une manière complètement différente.

Figure 1. KDPV

Qu'est-ce qui empêche de tels géants de la formation en microélectronique nationale, tels que MEPhI et MIET, d'agir de manière similaire à leurs collègues étrangers (par exemple, le MIT ou l'UZH), à savoir en donnant aux étudiants diplômés la possibilité de produire leurs propres cristaux? Bien sûr, on peut supposer que la production de son propre cristal est une tâche extrêmement longue, compliquée et coûteuse, et donc elle est coûteuse pour un institut et impossible pour un étudiant. Mais ce n'est pas le cas. Jetons un coup d'œil à l'une des technologies disponibles sur le marché national de la microélectronique, dont la connaissance permettra à l'étudiant de devenir beaucoup plus attrayant en termes d'emploi futur, et dont l'offre pour l'étudiant permettra à l'université d'augmenter considérablement sa note aux yeux des candidats et des employeurs.

2. Qu'est-ce que BMK?

BMK est un cristal matriciel de base. N'est-ce pas devenu plus clair? Ensuite, faites un pas de côté et examinez le cycle de production de fabrication de puces personnalisées (ASIC) grandement simplifié:

- Développement de description de schéma

- Création d'une topologie

- Transférer les fichiers technologiques vers l'usine et attendre que les cristaux soient prêts

- Mesures des cristaux obtenus

- Boîtier

- À vendre

Il y a ici deux points très «longs» - le développement du schéma et l'attente des résultats de l'usine. Différentes méthodologies sont utilisées pour réduire le temps de développement, et dans un environnement étudiant, la meilleure solution est le travail d'équipe, mais nous nous intéressons au deuxième point - les heures de travail de l'usine. Étant donné que la centrale microélectronique est une production très inerte, tout devrait être conforme au plan. Pas à temps pour la date de lancement de la production? La prochaine tentative se fera au cours du trimestre. La production elle-même, selon la complexité du produit, peut durer jusqu'à six mois. De plus, ces six mois sont le cycle de production approuvé sur des machines hautement automatisées, et non la négligence du personnel. Comment réduire ces conditions? En introduisant une certaine base commune dans tous les régimes produits, de sorte que l'étape de l'introduction des différences soit rapide.

Cette base commune est le BMK - un cristal avec des transistors pré-arrangés, dont le but fonctionnel est déterminé par les couches de métallisation, qui permettent aux transistors d'être interconnectés. Ces interconnexions forment la fonctionnalité unique du cristal.

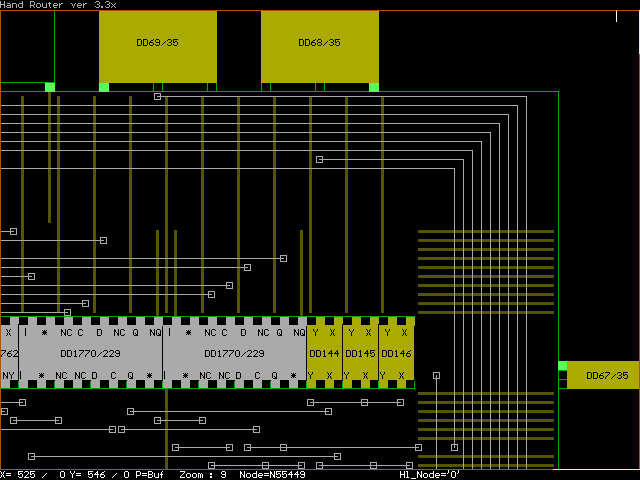

Figure 2. Hand Router v3.3, originaire des entrailles de NICEVT, créé dans les années 1980 et 1990.

Sur un BMK, en utilisant différents schémas de métallisation, il est possible de produire des centaines de microcircuits différents pour diverses organisations. Dans ce cas, BMK devient lui-même un produit de production de masse pour l'usine et les étapes de finition - couches de métallisation, peuvent être rapidement modifiées en fonction des besoins du client. Ainsi, nous obtenons des «lancements» de nouveaux produits plus fréquents dans la production et des prix plus bas. Pour le développement des étudiants, ces deux points sont extrêmement pertinents.

3. Pourquoi BMK?

Comparons les avantages de l'utilisation de différentes méthodes de formation et voyons ce qui donne le plus d'effet au moindre coût.

Tableau 1. Comparaison de l'effet éducatif de l'apprentissage à l'aide de diverses méthodes

Encodage d'en-tête sinon, il ne rentre pas dans la largeur de la mise en page.

A - Développement orienté FPGA

B - BMK sans FPGA et avec une vraie version

C - BMK utilisant FPGA et avec une vraie version

D - ASIC sans FPGA et sans véritable release

E - ASIC avec FPGA et aucune version réelle

F - ASIC avec FPGA et version réelle

G - Programme de formation en cours au MEPhI, kaf. 27

| Composant de route | Un | B | C | D | E | F | G |

|---|

| Énoncé du problème | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Programmation RTL | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Programmation RTL basée sur ASIC | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Travaillez avec la CAO moderne | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| Comprendre le code spécifique au FPGA | ■ | □ | ■ | □ | ■ | ■ | ○ |

| Comprendre le synthétiseur | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Comprendre les exigences de contrainte | ○ | ■ | ■ | □ | □ | ■ | □ |

| Comprendre l'importance du placement et du traçage | ○ | ■ | ■ | □ | □ | ■ | □ |

| Test | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Création d'un environnement de vérification | ■ | ■ | ■ | □ | ■ | ■ | □ |

| Simulation multi-coins | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Modélisation de l'extraction | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Boîtier | □ | ■ | ■ | □ | □ | ■ | □ |

| Circuit analogique | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Travailler avec des installations de mesure | □ | ■ | ■ | □ | □ | ■ | ○ |

| Travailler en laboratoire | ■ | ■ | ■ | □ | □ | ■ | ○ |

| Coût | 1 | 2 | 3 | 0 | 1 | 4 | 0 |

■ - est présent dans le programme;

□ - absent du programme;

○ - des options sont possibles.

Ce tableau est rempli uniquement à partir de ma vision de la façon dont la présence d'une étape particulière dans un projet de diplôme sphérique dans le vide affecte la diligence des étudiants. En réalité, quelqu'un peut maîtriser tout l'itinéraire sans aide pédagogique, tandis que quelqu'un est incapable d'écrire un multiplexeur sur Verilog. La ligne "coût" reflète le positionnement en haut, mais en aucun cas les multiplicateurs. De plus, le «coût» ne prend pas en compte le coût réel du CAD, pour un certain nombre de raisons différentes.

Maintenant, il devient clair qu'à moindre coût supplémentaire, la voie visant à la sortie de BMK, en utilisant des FPGA et avec une sortie réelle couvre exactement le même ensemble de compétences qui est nécessaire pour la sortie d'ASIC. Le reste des itinéraires, bien que couvrant nominalement un large éventail de compétences, dans la pratique, ils ne sont pas exécutés consciencieusement par les étudiants en raison du manque de motivation pour appliquer une grande quantité d'effort sans aucun résultat visible.

4. Surveillance du marché

À ce jour, la conception de microcircuits d'entrée de gamme est devenue une tâche assez simple: tout le monde a entendu parler des FPGA (circuits intégrés logiques programmables), des synthétiseurs à partir de code, des programmes pour organiser les composants et des traces ultérieures du microcircuit. Dans le même temps, de nombreux développeurs novices ont du mal à imaginer ce qu'est BMK, comment travailler avec lui et quels avantages il offre. Malheureusement pour les fabricants de BMK, cette situation conduit aux résultats suivants:

«L'analyse de 2009 montre les sorties de certains consommateurs en raison de l'élargissement du champ d'application des FPGA importés sur la base des permis délivrés.» (C) le rapport annuel d'Anstrem OJSC pour 2009.

Il existe de nombreux fabricants de BMK sur le marché de la microélectronique moderne: nationaux et étrangers. En particulier, dans l'État de l'Union de la Russie et du Bélarus, il existe au moins six fabricants de microcircuits qui proposent leurs BMC pour le développement: Angstrem OJSC, IEC NN, Progress NIIMA JSC, Technological Center Scientific and Production Center, Physics Physics OJSC et Integral Minsk ".

Habituellement, des systèmes de CAO spécialisés de sociétés bien connues telles que Cadence, Synopsis ou Mentor Graphics sont utilisés pour le développement de microcircuits, mais dans le cas de BMC, tout est un peu plus compliqué. Ce logiciel ne fournit pas de support officiel pour BMK, en tant que type de microcircuit séparé, mais il est possible de le faire fonctionner dans le bon mode en utilisant diverses astuces. Dans cette situation, les développeurs BMK doivent développer leurs propres itinéraires de conception uniques, qui utilisent parfois des logiciels OpenSource, par exemple, Yosis, ainsi que des logiciels développés de manière indépendante.

- Dans le cas d'Angstrom OJSC, il est très difficile de trouver les informations exactes et le CAD utilisé. Cependant, il y a des conditions préalables pour croire que leur «Nevod» CAD n'est plus utilisé et que la transition vers l'utilisation des produits Cadence est terminée.

- IEC NN, OJSC NPO Fizika, JSC NIIMA Progress et Integral ne fournissent pas d'informations sur le CAD utilisé, cependant Integral a PDK sous Cadence, nous pouvons donc conclure que le reste de l'itinéraire est également là.

- NPK "Technological Center" utilise leur "Ark" CAD, qui met en œuvre presque tout le parcours de conception. Dans tous les cas, cela est approuvé sur leur site Web.

5. Combien de valves suffisent pour tout le monde?

Une raison populaire de refus de travailler avec BMK est l'incertitude quant à savoir si le schéma développé s'intégrera dans ce BMK et à quelle vitesse tout cela fonctionnera. Bien sûr, c'est bien quand il y a une série BMK avec une bibliothèque de conception unique, et vous pouvez passer à un cristal plus spacieux ou plus rapide si nécessaire, mais ce n'est pas toujours possible. Ici, par exemple, tout est clair sur TSMC: il existe de nombreuses entreprises qui déclarent ouvertement la vitesse de leurs circuits effectués sur l'un ou l'autre de ceux-ci. processus. Et notre BMK? Où puis-je obtenir une liste des produits créés sur la base de BMK et voir leurs performances?

Quelques exemples:

- BMK numérique-analogique. Environ 300 portes + 8 transistors de puissance. Un schéma de minuterie de 2 minutes avec deux niveaux de protection est implémenté. Surveillance de la charge sur les miroirs de courant, transistors de puissance pour contrôler la charge. Réduction de la consommation d'énergie, travail avec quartz 32,768 kHz, gamme de tensions d'alimentation de 1,8V à 9V.

- Numérique heureux. BMK persistante. 100 000 valves. Promotions logiques. destination + NCO (oscillateur à commande numérique). Phase de la batterie 40 bits, sinus - 12 bits. Deux registres contrôlent la fréquence sinusoïdale, le contrôle parallèle et série. La sortie est parallèle.

- BMK numérique-analogique. Environ 400 portes + DAC de 10 catégories. Générateur sinus 7 bits avec sortie courant.

- Digital BMK. De 1500 à 3000 vannes. Différents terminaux du canal multiplex GOST 26765.52-87.

- Digital BMK. Environ 500 portes. Un générateur à huit canaux pour contrôler les enroulements primaires des transformateurs.

- Digital BMK. Environ 3000 portes. Circuit majoritaire pour bus 8 bits.

Malheureusement, les spécificités du marché conduisent au fait que la grande majorité des développements chez BMK restent inconnus du grand public. Les données publiques ne donnent pas une idée claire de la vitesse et les chiffres indiqués dans les brochures semblent ambigus. Cependant, pour les tâches d'apprentissage de la technologie, beaucoup n'est pas nécessaire et il est beaucoup plus facile d'avoir une certaine expérience derrière elle pour donner une estimation approximative de la complexité d'un système particulier.

6. Processus de développement

Passons au plus intéressant. Nous avons: BMK pour ~ 3k valves (1 valve = 2 transistors CMOS) avec architecture de canal, câblage dans une couche métallique et une sous-couche de silicium polycristallin; enthousiasme; approbation de la direction de l'entreprise pour l'autoformation des employés.

L'idée du futur cristal est née de l'oisiveté, à savoir de la lecture d'un forum, où, en particulier, il y a eu une conversation sur des solutions compactes pour le calcul des codes sinus. Ce sujet m'a paru intéressant et j'ai décidé de voir ce qui peut être fait dans ce sens.

Voyons maintenant ce qui a été fait, ce qui n'a pas été fait, quelles erreurs et quelles conclusions ont été tirées.

6.1 Conception

Des études de surface ont montré qu'il existe un algorithme de calcul des valeurs sinusoïdales qui, à partir des opérations mathématiques, ne nécessite que la sommation, la soustraction et le décalage vers la droite. Il s'est avéré que ce n'est pas seulement un algorithme, mais toute une famille appelée CORDIC (ordinateur numérique à rotation coordonnée). Ceux qui sont intéressés par les détails du fonctionnement de l'algorithme peuvent se référer à la liste des références à la fin de l'article, mais je préciserai seulement qu'en utilisant cet algorithme, il est possible de calculer non seulement le sinus, mais aussi le cosinus, l'arc tangent, multiplier et diviser les arguments, et compter certaines fonctions hyperboliques.

Ayant étudié de nombreuses publications sur cet algorithme et systématisant ces connaissances dans ma tête, j'ai pensé que vous pouvez essayer de mettre en œuvre cet algorithme sur un BMK avec une capacité d'environ 3 k valves.

Alors, que finissons-nous avec l'architecture des circuits?

- Algorithme CORDIC pipeliné étendu pour le calcul du sinus.

- 4 bits supplémentaires dans les bus de données internes pour compenser les erreurs d'arrondi.

- Totalisateur cumulatif 11 bits pour la valeur de phase.

- L'incrément de phase est réglé par le bus parallèle.

- Format des données de sortie: 7 bits + signe, bus parallèle.

Tout semble aller bien, mais que se passe-t-il si vous ne compensez pas les erreurs d'arrondi? Et voici quoi (en comparant le bus interne 11bit et 8bit):

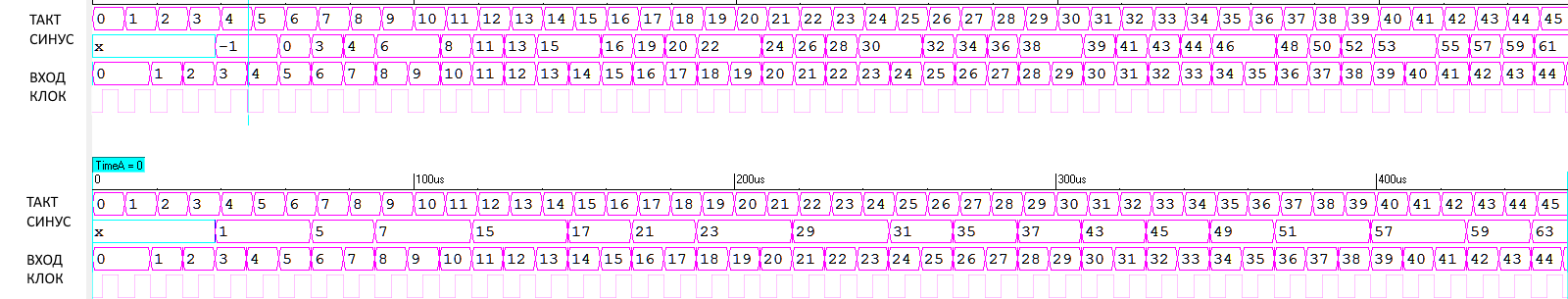

Figure 3. Comparaison de la sortie de l'algorithme CORDIC lors de l'utilisation de bus internes de 11 bits et 8 bits, respectivement.

Si vous faites attention aux deuxièmes lignes de données, vous pouvez voir que les erreurs d'arrondi peuvent effectivement réduire la qualité de vos calculs.

Si à l'avenir nous attachons cette puce au DAC 7 bits, nous obtenons un générateur de sinus complètement adapté (DDS, à notre avis - synthèse numérique directe). Dans ce cas, nous aurons la possibilité de moduler la fréquence du sinus, mais il n'y aura pas de possibilité de modulation de phase.

En général, l'itinéraire pour travailler avec de petits BMC est quelque peu différent de l'itinéraire de conception actuel. Si vous y réfléchissez, les différences deviennent évidentes: avec un volume de soupape aussi petit, il est nécessaire d'utiliser chaque soupape de manière extrêmement efficace, et le paradigme principal du design moderne n'est pas du tout cela. Elle dit que le produit doit à chaque étape être architecturalement compatible avec les systèmes modernes de test, vérification, mesure automatisés. Dans ce cas, la question de l'efficacité des vannes reste en dehors des supports, comme le surcoût nécessaire. En effet, dans les années de développement dynamique des technologies de production, la réflexion sur l'efficacité était superflue. Donc, quand (et si) nous atteignons toujours la limite physique et cessons d'augmenter la densité de transistors sur le cristal, alors les problèmes d'efficacité de l'utilisation de la zone nous reviendront en pleine croissance. Eh bien, avec les petits BMK, ils sont déjà à pleine hauteur, et donc la conclusion: dans le BMK des petits réservoirs, vous pouvez et devez utiliser des conceptions complexes en utilisant divers schémas de génération de blocs délicats, divers verrous, rétroactions et autres, pour l'utilisation de qui dans la route moderne un ingénieur principal lui aurait déchiré les mains.

Le principal problème avec l'utilisation de telles choses est que pour les utiliser, l'ingénieur doit clairement être conscient de ce qu'il fait et pourquoi. Cependant, s'il y a compréhension, le gain peut être fantastique. S'il n'y a pas de compréhension ... eh bien, vous pouvez tirer dans la jambe avec un million de façons efficaces différentes.

À quoi ressemblait l'itinéraire de conception dans mon cas:

- Cartographie manuelle sous forme de graphique d'éléments de bibliothèque

- Estimation du volume de circuit résultant

- Traitement du circuit jusqu'à ce que le volume du circuit dépasse 80% de la capacité BMK

- Cela comprend également des travaux sur la création de nouveaux éléments de bibliothèque, leur test et leur intégration dans l'itinéraire de conception

- Elaboration des tests du circuit

- Traçage manuel des circuits

Les concepteurs expérimentés ici peuvent immédiatement objecter que plusieurs étapes importantes ont été manquées, mais j'ai vraiment oublié de mentionner quoi que ce soit.

La conception manuelle montre très bien l'importance d'une bibliothèque de composants de qualité. Les premières variantes du circuit ne rentrent pas dans le cristal simplement par le volume de la logique, mais dans le cas d'un canal BMC - celui où le câblage passe par les canaux disposés entre les "rangées" de transistors - environ 30% du volume du circuit est occupé par des interconnexions. Par conséquent, j'ai dû étendre quelque peu la bibliothèque, en fonction de la topologie obtenue dans ce projet particulier. Cette approche a permis de sauver un nombre important de portes et de poser plus ou moins librement toutes les routes.

Le remplissage final du cristal est de 72%, un autre tiers du cristal est allé au câblage. Ensuite, les fichiers ont été transférés à l'usine et je suis retourné à mes projets de travail actuels.

Avec la méthode de conception «manuelle», les points suivants doivent être rappelés:

- Vous ne pouvez pas utiliser des éléments de bibliothèque sans réfléchir en fonction de leur fonction. Il est nécessaire d'étudier la composition de cet élément au niveau du transistor, qu'il soit numérique ou analogique. Quelles sont ses capacités porteuses en termes d'entrées et de sorties, qu'il soit purement logique CMOS, ou TG, ou autre chose.

- Il faut prendre en compte et coordonner la puissance des éléments et leur charge.

- Si vous avez un déclencheur synchrone, vous devez le synchroniser avec des signaux de puissance égale.

- Si vous utilisez un type de signal sans amplification intermédiaire et qu'il est chargé sur de nombreux consommateurs, le signal peut échouer considérablement. Cela peut être insignifiant dans des conditions normales, mais il est essentiel lors du test du WWF (facteurs externes).

Aucun système de modélisation ne peut remplacer votre propre cerveau. En général, vous ne pouvez pas exécuter une simulation si vous ne comprenez pas vous-même le fonctionnement du circuit.

6.2 Mesures

Une étape extrêmement importante dans le travail avec un cristal est ses mesures. On distingue trois types de mesures: technologiques, fonctionnelles, électriques. Les premiers vérifient que la plante n'est pas arrachée et que le cristal est technologiquement correctement fabriqué. Ces derniers vérifient que la théorie (c'est-à-dire la modélisation) converge avec la pratique (cristal réel). , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

. 4 (!) . , , . , ?) " ".

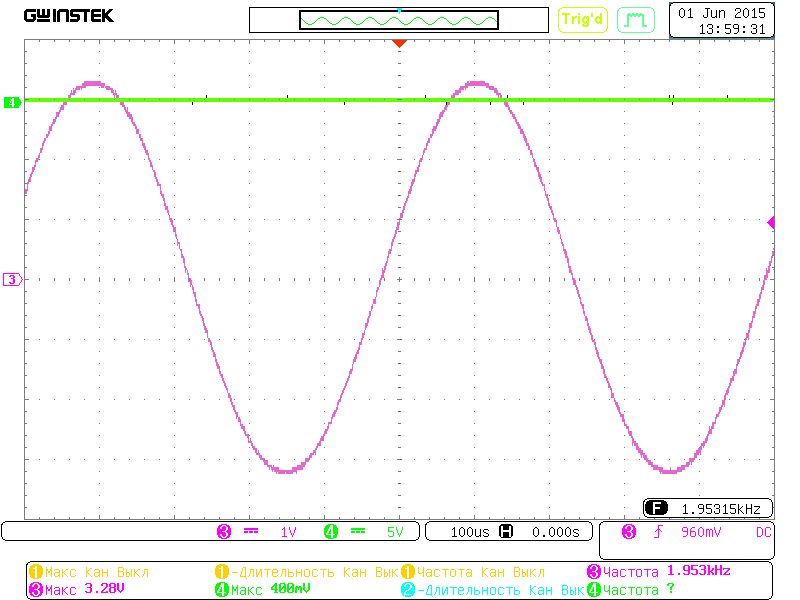

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

Remarque .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

Littérature

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf