Bonjour

L'article passe en revue l'architecture du système de mémoire virtuelle ARMv7.

En-tête de spoilerLes subtilités de la mise en cache, du DMA, du LPAE et similaires ne sont pas prises en compte ici. Pour une description plus détaillée, reportez-vous à la littérature à la fin de l'article.

Présentation

Le système de mémoire virtuelle effectue plusieurs tâches. Premièrement, il vous permet de placer les processus utilisateur dans des espaces mémoire séparés, isolés les uns des autres. Cela vous permet d'augmenter la fiabilité du système, les erreurs d'un processus n'affectent pas le fonctionnement des autres processus. Deuxièmement, le système d'exploitation peut fournir au processus plus de mémoire que le système. Les pages de mémoire inutilisées sont poussées dans un stockage permanent et les nécessaires sont chargées à partir de là, formant l'illusion d'une plus grande quantité de mémoire qu'elle ne l'est réellement. Troisièmement, l'espace virtuel continu facilite l'écriture de logiciels personnalisés. Tous les processus sont exécutés dans le même espace, le système d'exploitation leur cache la configuration réelle de la mémoire dans le système.

Définitions

Les définitions suivantes sont utilisées dans l'article:

Adresse virtuelle - L'adresse utilisée par le cœur du processeur. Le pointeur de pile, le compteur d'instructions, le registre de retour utilisent une adresse virtuelle.

Adresse physique - L'adresse de sortie sur le bus du processeur.

Une page est une unité d'adressage de mémoire virtuelle.

Section - un analogue de la page, a une plus grande taille.

Une trame est une unité d'adressage de mémoire physique.

Table de pages - un tableau d'enregistrements pour la traduction d'adresses.

ASID est l'identifiant de l'espace d'adressage.

TLB - tampon de traduction rapide des adresses.

MMU est une unité de gestion de mémoire.

TLB

TLB est un tampon matériel très rapide contenant les résultats des dernières traductions d'adresses. La requête du noyau pour traduire l'adresse de la page et l'ASID actuel arrive dans le TLB. S'il y a une entrée valide, les autorisations d'accès à cette mémoire sont vérifiées, la méthode d'accès et l'adresse de trame correspondante sont renvoyées à la MMU. Si l'accès à la mémoire est refusé, une exception matérielle est levée. Si un échec TLB s'est produit (aucun enregistrement n'a été trouvé), le comportement supplémentaire est sensible à la casse par TTBCR. Une recherche peut être effectuée dans les tables de pages ou une exception est levée.

Il est important de noter que lors de la manipulation des tables de pages, vous devez réinitialiser correctement le TLB, car des informations non pertinentes peuvent y être stockées.

La mise à jour des entrées dans le TLB est transparente pour le programmeur à tour de rôle.

Il est également possible de télécharger et de sécuriser certaines entrées dans le TLB pour éviter leur éviction.

Figure 1. TLB

Figure 1. TLBTableaux de pages

ARMv7 est une architecture 32 bits, nous avons donc 4 Go de mémoire virtuelle adressable.

Les tableaux de pages sont divisés en 2 niveaux - L1 et L2.

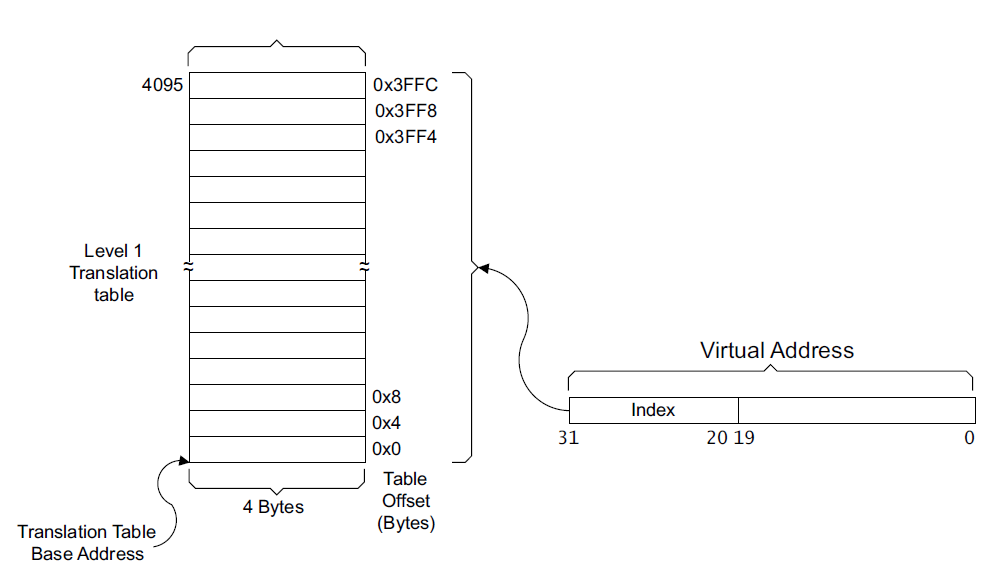

Le tableau L1 décrit les 4 Go d'espace d'adressage. Il se compose de 4096 enregistrements 32 bits, chacun décrivant 1 Mo. Les entrées du tableau sont sélectionnées par les 12 bits de poids fort de l'adresse virtuelle.

Fig. 2 Recherchez les entrées dans le tableau L1

Fig. 2 Recherchez les entrées dans le tableau L1La table L1 est située dans la mémoire physique et alignée sur une bordure de 16 Ko. Il existe 4 options pour ces entrées: pour décrire les pages, les sections et les supersections. Eh bien, un enregistrement vide, pour une mémoire qui n'est pas encore mappée.

Fig. 3 Types d'entrées en L1

Fig. 3 Types d'entrées en L1Les bits 0 et 1 indiquent le type d'enregistrement 00b-Fault, 01b est le descripteur de page, 10b est le descripteur de section (et la supersection).

Si la mémoire physique est paginée, alors la table L1 stocke l'adresse de la table L2 (physique, alignée à 1Kb). Le bit 9 est déterminé par le fabricant (implémentation définie), les bits [8: 5] - pour le mécanisme de domaine (obsolète dans ARMv7), SBZ - zéros.

Si nous décidons de diviser la mémoire en sections, alors dans L1 il est nécessaire d'écrire l'adresse physique correspondante. La section fait directement référence à la zone de mémoire physique alignée de 1 Mo. Pas besoin de table L2. La supersection est un cas particulier de partitionnement, l'entrée dans la table L1 doit être répétée 16 fois, l'alignement des blocs alloués de mémoire physique et virtuelle est également de 16 Mo.

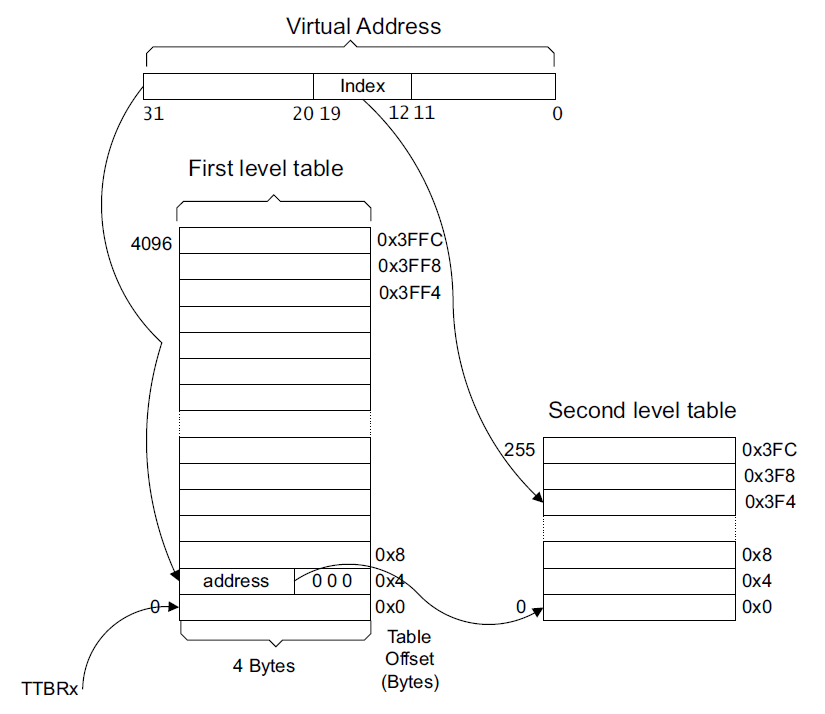

Le tableau L2 comprend 256 entrées de 32 bits. Il doit être aligné sur 1 Ko.

Fig. 4 Recherchez les entrées dans le tableau L2

Fig. 4 Recherchez les entrées dans le tableau L2Les indices du tableau L2 sont formés à partir des 8 bits moyens [19:12] de l'adresse virtuelle. Chaque entrée de table contient l'adresse de la trame.

Fig. 5 Types d'entrées en L2

Fig. 5 Types d'entrées en L2Les pages peuvent être de deux tailles: 64 Ko (grande page) et 4 Ko (petite page).

Les bits AP et APX définissent les autorisations de lecture / écriture en mode privilégié / non privilégié (noyau / utilisateur). Les bits TEX, C, B, S sont responsables du type de mémoire, de sa mise en cache et de la mise en mémoire tampon en lecture-écriture. Le bit nG - nonGlobal permet d'accéder à la page pour tous les processus ou pour un seul ASID spécifique.

L'utilisation de grandes pages réduit le nombre d'entrées dans le TLB. Au lieu de 16 entrées (4Kb * 16 = 64Kb), une seule y sera stockée. Cependant, 16 entrées identiques doivent être saisies dans le tableau L2.

La possibilité d'adresser différentes tailles de blocs permet, d'une part, d'allouer de la mémoire avec la granularité souhaitée, d'autre part, de réduire le nombre d'appels aux tables de pages dans une mémoire relativement lente.

Registres

Pour contrôler le système (y compris la MMU) dans l'architecture ARM, un coprocesseur spécial CP15 est conçu. Pour la gestion de la mémoire sont une douzaine et demi de ses registres. Nous sommes intéressés par plusieurs d'entre eux - Control, TTBR0 / 1, TTBCR, ContextID.

Dans le registre de contrôle, le bit le moins significatif est responsable de la mise sous / hors tension de la MMU, tout est simple.

La paire de registres TTBR0 / 1 contient les adresses physiques des tables du premier niveau. À ces adresses, la MMU commence à rechercher la page souhaitée.

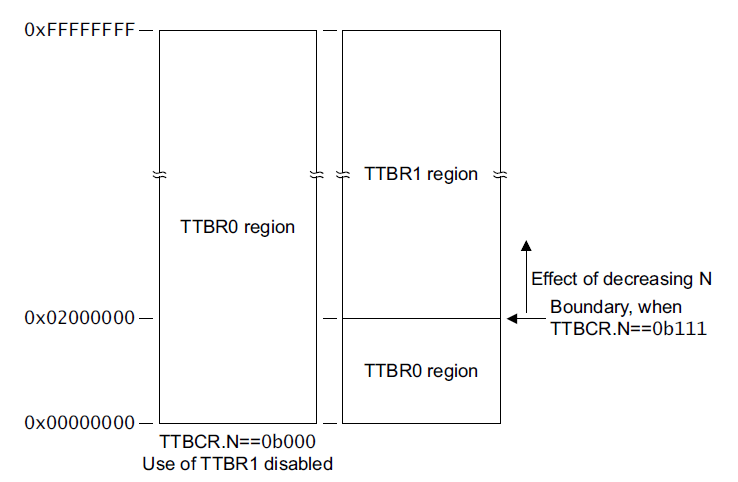

Le registre TTBCR vous permet de diviser tout l'espace d'adressage en 2 parties entre TTBR0 et TTBR1. Chacun d'eux diffusera sa partie des adresses. Les bits [2: 0] sont utilisés pour définir la taille. Le nombre enregistré (de 0 à 7 décimal) masque la partie la plus ancienne des adresses virtuelles. Si sa valeur est «0», toutes les adresses sont diffusées via TTBR0. Si «1», les adresses 31 bits sont masquées et les 2 Go d'espace virtuel inférieurs passent par TTBR0, les supérieurs par TTBR1. «2» - 31 et 30 bits sont masqués et la division en 1 Go et 3 Go est obtenue, respectivement. Ainsi, la partie inférieure des adresses peut être utilisée pour les applications utilisateur, surchargeant le registre TTBR0 pour un nouveau processus, et la partie supérieure peut être laissée pour les besoins du système.

Fig. 6 Espace d'adressage divisé

Fig. 6 Espace d'adressage diviséLes bits [5: 4] sont responsables du comportement manqué TLB - recherche dans les tables de pages ou une exception.

Le registre ContextID contient le champ ASID du processus en cours. Il doit être modifié avec le contenu du registre TTBR0 lors du changement de contexte.

Traduction d'adresse

L'algorithme de conversion des adresses virtuelles en adresses physiques est le suivant:

- Recherchez l'adresse virtuelle et l'ASID demandés dans le tampon TLB

- Si le TLB n'a pas l'adresse requise, une recherche matérielle est effectuée dans les tableaux de pages

Si le noyau a précédemment demandé une page virtuelle, elle est stockée dans le TLB. Dans ce cas, le MMU le sort du cache et rien ne doit être fait. Si la page est demandée pour la première fois (ou si elle a été forcée à partir de là - le TLB n'est pas très grand), alors la recherche dans les tables L1-L2 est effectuée. Ainsi, le mappage des adresses virtuelles et physiques est le suivant:

- Dans le registre TTBR0 \ TTBR1, l'adresse de la table L1 est recherchée.

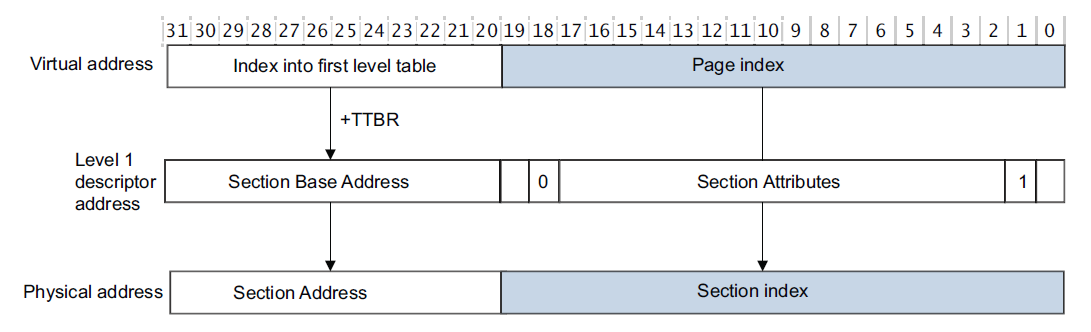

- Les 10 premiers bits de l'adresse virtuelle forment un index dans le tableau.

- a) Si l'enregistrement correspond à la section (supersection), les attributs de la section sont vérifiés et, si tout est OK, l'adresse physique résultante est composée de l'adresse de base de la section (supersection) et des 20 (24) bits inférieurs de l'adresse virtuelle.

En-tête de spoiler Fig. 7 Traduction d'adresse en super section

Fig. 7 Traduction d'adresse en super section

b) Si l'enregistrement est une table L2, la recherche s'y poursuit. La partie centrale de l'adresse virtuelle de la page constitue l'index de la table.

En-tête de spoiler Fig. 8 Traduction d'adresse dans le tableau L2

Fig. 8 Traduction d'adresse dans le tableau L2

- Mise à jour TLB en cours

Au total, le sous-système de mémoire virtuelle se compose des parties suivantes:

- Plusieurs registres de contrôle CP15

- Tableaux de pages contenant des règles de traduction d'adresses

- TLB - cache d'émissions réussies

- MMU est une unité de traduction d'adresses.

Littérature

Manuel de référence de l'architecture ARM Édition ARMv7-A et ARMv7-R

Guide du programmeur ARM Cortex-A Series