Technologies microélectroniques modernes - comme «Ten Little Indians». Le coût de développement et d'équipement est si élevé qu'à chaque nouvelle étape, quelqu'un tombe. Après la nouvelle du refus de GlobalFoundries de développer le 7 nm, il en restait trois: TSMC, Intel et Samsung. Et que sont exactement les «normes de conception» et où se trouve cette taille très appréciée de 7 nm? Et est-il là du tout?

Figure 1. Transistor Fairchild FI-100, 1964.Les tout premiers transistors MOS en série sont entrés sur le marché en 1964 et, comme les lecteurs sophistiqués peuvent le voir sur le dessin, ils n'étaient

presque pas différents des plus ou moins modernes - à l'exception de la taille (regardez le fil pour l'échelle).

Pourquoi réduire la taille des transistors? La réponse la plus évidente à cette question s'appelle la loi de Moore et stipule que tous les deux ans le nombre de transistors sur une puce doit être doublé, ce qui signifie que les dimensions linéaires des transistors devraient diminuer d'un facteur deux. «Must» - selon les observations de Gordon Moore (et d'autres ingénieurs) dans les années 70. D'après la loi de Moore, de nombreux autres facteurs composent la feuille de route de la microélectronique ITRS. La formulation la plus simple et la plus approximative des méthodes de mise en œuvre de la loi de Moore (également connue sous le nom de loi de miniaturisation de Dennard) est qu'une augmentation du nombre de transistors sur une puce ne devrait pas conduire à une augmentation de la densité de la consommation d'énergie, c'est-à-dire qu'avec une diminution de la taille des transistors, la tension d'alimentation et le courant de fonctionnement devraient être proportionnellement réduits.

Le courant traversant le transistor MOS est proportionnel au rapport de sa largeur à sa longueur, ce qui signifie que nous pouvons maintenir le même courant, en réduisant proportionnellement ces deux paramètres. De plus, en réduisant la taille du transistor, nous réduisons également la capacité de la grille (proportionnelle au produit de la longueur et de la largeur du canal), ce qui rend le circuit encore plus rapide. En général, dans un circuit numérique, il n'y a pratiquement aucune raison de rendre les transistors plus grands que la taille minimale. Ensuite, les nuances commencent que dans les transistors à canal p logiques sont généralement légèrement plus larges que ceux à canal n afin de compenser la différence de mobilité des porteurs de charge, et en mémoire, au contraire, les transistors à canal n sont plus larges afin que la mémoire puisse être écrite normalement via une clé incomplète, mais c'est vraiment nuances, et globalement - plus la taille du transistor est petite - mieux c'est pour les circuits numériques.

C'est pourquoi la longueur du canal a toujours été la plus petite taille dans la topologie du microcircuit et la désignation la plus logique.

Il convient de noter ici que le raisonnement ci-dessus sur la taille n'est pas valable pour les circuits analogiques. Par exemple, en ce moment sur le deuxième moniteur de mon ordinateur, il y a une paire de transistors appariés utilisant la technologie 150 nm, 32 pièces de 8/1 microns chacune. Ceci est fait afin de garantir l'identité de ces deux transistors, malgré la variation technologique des paramètres. La zone est d'importance secondaire.Les technologues et les topologues ont le soi-disant système lambda de tailles de topologie typiques. Il est très pratique pour étudier le design (et a été inventé à l'Université de Berkeley, si je ne me trompe pas) et transférer des designs d'une usine à l'autre. En fait, il s'agit d'une généralisation des tailles typiques et des limites technologiques, mais un peu rugueuse, de sorte que cela fonctionne exactement dans n'importe quelle usine. Sur son exemple, il est pratique de regarder les tailles typiques des éléments de la puce. Les principes au cœur du système lambda sont très simples:

- si le décalage d'éléments sur deux masques photolithographiques différents a des conséquences catastrophiques (par exemple, un court-circuit), alors la marge de taille pour éviter les incohérences doit être d'au moins deux lambdas;

- si le déplacement des éléments a des conséquences indésirables mais non catastrophiques, la marge de taille doit être d'au moins un lambda;

- la taille minimale autorisée des fenêtres du masque photo est de deux lambdas.

Il ressort en particulier du troisième paragraphe que le lambda dans les anciennes technologies est la moitié de la norme de conception (plus précisément, la longueur du canal du transistor et les normes de conception sont deux lambdas).

Figure 2. Exemple de topologie effectuée par un système lambda.Le système lambda a parfaitement fonctionné sur les anciennes normes de conception, vous permettant de transférer facilement la production d'une usine à l'autre, d'organiser des fournisseurs de deuxième puce et de faire des choses beaucoup plus utiles. Mais avec la concurrence croissante et le nombre de transistors sur une puce, les usines ont commencé à s'efforcer de rendre la topologie un peu plus compacte, donc maintenant vous ne pouvez pas respecter les règles de conception correspondant à un système lambda "propre", sauf dans les situations où les développeurs les rendent rugueux indépendamment, en tenant compte de la probabilité de production puce dans différentes usines. Cependant, au fil des ans, l'industrie a développé une connexion directe «normes de conception = longueur de canal de transistor», qui a réussi jusqu'à ce que les transistors atteignent des dizaines de nanomètres.

Figure 3. Coupe schématique du transistor.Cette figure montre une section TRÈS simplifiée d'un transistor plan (plat) conventionnel, montrant la différence entre la longueur de canal topologique (Ldrawn) et la longueur de canal effective (Leff). D'où vient la différence?

Parlant de la technologie microélectronique, la photolithographie est presque toujours mentionnée, mais beaucoup moins souvent sont d'autres opérations technologiques non moins importantes: gravure, implantation ionique, diffusion, etc. etc. Pour notre conversation avec vous, un rappel du fonctionnement de la diffusion et de l'implantation ionique n'est pas superflu.

Figure 4. Comparaison de la diffusion et de l'implantation ionique.Avec la diffusion, tout est simple. Vous prenez une plaquette de silicium sur laquelle à l'avance (à l'aide de la photolithographie) un dessin est appliqué, couvrant d'oxyde de silicium les endroits où l'impureté n'est pas nécessaire et ouvrant ceux où elle est nécessaire. Ensuite, vous devez placer l'impureté gazeuse dans la même chambre avec le cristal et chauffer à une température à laquelle l'impureté commence à pénétrer dans le silicium. En ajustant la température et la durée du processus, il est possible d'obtenir la quantité et la profondeur d'impuretés souhaitées.

L'inconvénient évident de la diffusion est que l'impureté pénètre dans le silicium dans toutes les directions de la même manière, que vers le bas, de ce côté, réduisant ainsi la longueur effective du canal. Et nous parlons maintenant de centaines de nanomètres! Alors que les normes de conception étaient mesurées en dizaines de microns, tout allait bien, mais bien sûr, cet état de choses ne pouvait pas durer longtemps, et la diffusion a été remplacée par l'implantation ionique.

Lors de l'implantation ionique, un faisceau d'ions impureté accélère et est dirigé sur une tranche de silicium. Dans ce cas, tous les ions se déplacent dans une direction, ce qui élimine pratiquement leur propagation sur les côtés. En théorie, bien sûr. En pratique, les ions se répartissent néanmoins un peu à l'écart, quoique à des distances beaucoup plus courtes que lors de la diffusion.

Néanmoins, si nous revenons au modèle de transistor, nous verrons que la différence entre la longueur topologique et la longueur effective du canal commence précisément à cause de ce petit fluage. Elle, en principe, pourrait être négligée, mais ce n'est pas la seule raison de la différence. Il y a encore des effets de canal courts. Il y en a cinq et, de diverses manières, ils modifient les paramètres du transistor si la longueur du canal se rapproche de diverses restrictions physiques. Je ne les décrirai pas tous, je m'attarderai sur le plus pertinent pour nous - DIBL (Drain-Induced Barrier Lowering, diminution induite par le drainage de la barrière de potentiel).

Afin d'entrer dans l'évier, un électron (ou trou) doit surmonter la barrière potentielle de la jonction pn de l'évier. La tension de grille réduit cette barrière, contrôlant ainsi le courant à travers le transistor, et nous voulons que la tension de grille soit la seule tension de commande. Malheureusement, si le canal du transistor est trop court, la jonction pn de drain commence à influencer le transistor, ce qui, d'une part, réduit la tension interstitielle (voir la figure ci-dessous), et d'autre part, la tension aux bornes du transistor commence à affecter non seulement la tension de grille , mais aussi au drain, car l'épaisseur de la jonction pn de drain augmente proportionnellement à la tension au drain et, par conséquent, raccourcit le canal.

Figure 5. Effet d'abaissement de barrière induit par le drain (DIBL).

Source - Wikipedia.De plus, une diminution de la longueur du canal conduit au fait que les porteurs de charge commencent à passer librement de la source au drain, contournant le canal et formant un courant de fuite (mauvais courant dans la figure ci-dessous), qui est également une consommation électrique statique, dont l'absence était l'une des raisons importantes du succès précoce du CMOS -technologies, plutôt inhibitrices par rapport aux concurrents bipolaires de l'époque. En fait, chaque transistor de la technologie moderne a une résistance parallèle à lui, dont la valeur est la plus petite, plus la longueur du canal est petite.

Figure 6. L'augmentation de la consommation d'électricité statique due aux fuites dans les technologies à canal court.

Source - Synopsys.Figure 7. Proportion de la consommation d'électricité statique des microprocesseurs selon différentes normes de conception.

Source - B. Dieny et. al., «Effet de transfert de spin et son utilisation dans les composants spintroniques», International Journal of Nanotechnology, 2010Maintenant, comme vous pouvez le voir sur la figure ci-dessus, la consommation statique dépasse considérablement la dynamique et constitue un obstacle important à la création de circuits à faible puissance, par exemple pour l'électronique portable et l'Internet des objets. En fait, à peu près au moment où il est devenu un problème important, la commercialisation du muhlezh avec les normes de conception a commencé, car les progrès en lithographie ont commencé à dépasser les progrès en physique.

Pour lutter contre les effets indésirables du canal court à des normes de conception de 800 à 32 nanomètres, de nombreuses solutions technologiques différentes ont été inventées, et je ne les décrirai pas toutes, sinon l'article atteindra des tailles très indécentes, mais à chaque nouvelle étape, je devais introduire de nouvelles solutions - supplémentaires dopage des zones adjacentes aux jonctions pn, dopage en profondeur pour éviter les fuites, transformation locale du silicium des transistors en silicium-germanium ... Pas une seule étape n'a été franchie pour réduire la taille des transistors. oh oui.

Figure 8. La longueur effective du canal dans les technologies de 90 nm et 32 nm. Les transistors sont tournés à la même échelle. Les demi-cercles sur les figures sont une forme d'adéquation faible supplémentaire des drains (LDD, drain légèrement dopé), conçue pour réduire la largeur des jonctions pn.

Source - Synopsys.Les tailles et les distances de métallisation typiques entre les éléments pendant la transition de 90 nm à environ 28 nm ont diminué proportionnellement à une diminution de la norme de conception, c'est-à-dire que la taille typique de la prochaine génération était de 0,7 par rapport à la précédente (de sorte que, selon la loi de Moore, pour obtenir une réduction de surface deux fois). Dans le même temps, la longueur du canal a diminué au mieux à 0,9 par rapport à la génération précédente, et la longueur effective du canal n'a pratiquement pas changé du tout. Il ressort clairement de la figure ci-dessus que les dimensions linéaires des transistors n'ont pas changé du tout de 90 nm à 32 nm, et tous les jeux des technologues étaient autour de la réduction du chevauchement des volets et des zones dopées, ainsi que du contrôle des fuites statiques, ce qui n'était pas autorisé. le canal est plus court.

En conséquence, deux choses sont devenues claires:

- descendre en dessous de 25-20 nm sans percée technologique ne fonctionne pas;

- il est devenu de plus en plus difficile pour les spécialistes du marketing de brosser un tableau des progrès de la technologie avec la loi de Moore.

La loi de Moore est généralement un sujet controversé, car ce n'est pas une loi de la nature, mais une observation empirique de certains faits de l'histoire d'une entreprise particulière, extrapolés aux progrès futurs de l'ensemble de l'industrie. En fait, la popularité de la loi de Moore est inextricablement liée aux spécialistes du marketing d'Intel, qui en ont fait leur bannière et, en fait, ont fait avancer l'industrie pendant de nombreuses années, l'obligeant à se conformer à la loi de Moore où, peut-être, cela valait la peine d'attendre un peu.Comment les spécialistes du marketing ont-ils découvert la situation? Très élégant.

La longueur du canal du transistor est bonne, mais comment pouvez-vous en estimer le gain dans la zone, ce qui donne la transition vers de nouvelles normes de conception? Il y a assez longtemps, l'industrie utilisait la zone d'une cellule de mémoire à six transistors, le bloc de construction de microprocesseur le plus populaire. Ce sont ces cellules qui se composent généralement d'une mémoire cache et d'un fichier de registre pouvant occuper un demi-cristal, et c'est pourquoi le schéma et la topologie d'une cellule à six transistors sont toujours soigneusement léchés à la limite (souvent des personnes spéciales qui le font), c'est donc une très bonne mesure densité d'emballage.

Figure 9. Schéma d'une cellule de mémoire statique à six transistors.Figure 10. Différentes options de topologie pour une cellule de mémoire statique à six transistors. Source - G. Apostolidis et. al., «Design and Simulation of 6T SRAM Cell Architectures in 32nm Technology», Journal of Engineering Science and Technology Review, 2016Ainsi, pendant longtemps dans les descriptions des technologies, le nombre de normes de conception a été accompagné du deuxième chiffre - la zone de la cellule de mémoire, qui, en théorie, devrait être dérivée de la longueur du canal. Et puis il y a eu une intéressante substitution de concepts. À une époque où la mise à l'échelle directe a cessé de fonctionner et la longueur du canal a cessé de diminuer tous les deux ans selon la loi de Moore, les spécialistes du marketing ont réalisé qu'il était possible de ne pas dériver la zone de la cellule mémoire des normes de conception, mais de dériver le nombre de normes de conception de la zone de la cellule mémoire!

Autrement dit, «auparavant, nous avions une longueur de canal de 65 nm et une zone de cellule de mémoire de X, et maintenant la longueur de canal est de 54 nm, mais nous avons réduit la métallisation, et maintenant la zone de cellule est devenue X / 5, ce qui correspond à peu près à une transition de 65 à 28 nm. Alors disons à tout le monde que nous avons des normes de conception de 28 nm, et nous ne parlerons à personne de la longueur de canal de 54 nm? " En toute honnêteté, la «métallisation piquante» est également une réalisation importante, et pendant un certain temps après le début des problèmes de miniaturisation des transistors eux-mêmes, la largeur minimale de métallisation, la taille du contact avec le transistor ou toute autre figure sur la topologie correspondait aux normes de conception énoncées. Mais ensuite, les danses ont commencé avec les transistors FinFET, dans lesquels les dimensions clés n'avaient rien à voir avec la résolution de la lithographie, les taux de miniaturisation des transistors et tout le reste ont finalement divergé, et la zone des cellules de mémoire est restée la seule figure normale, sur la base de laquelle nous sommes maintenant informés de «10», « 7 ”et“ 5 ”nanomètres.

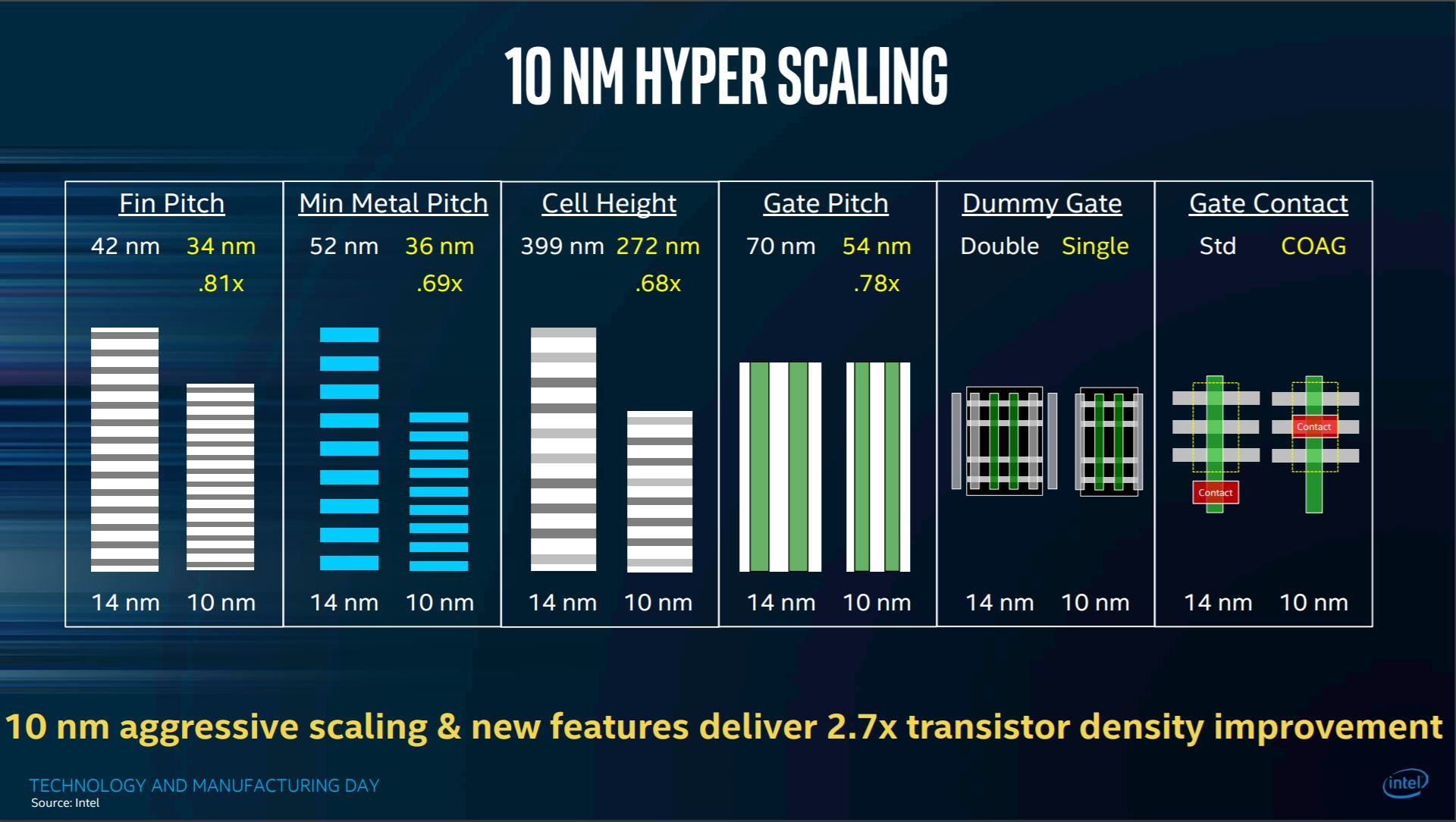

Source - Intel.Voici un excellent exemple de cette «nouvelle mise à l'échelle». On nous montre comment les tailles caractéristiques de la cellule mémoire ont changé. De nombreux paramètres, mais pas un mot sur la longueur et la largeur du canal du transistor!

Comment ont-ils résolu le problème de l'impossibilité de réduire la longueur du canal et de contrôler les fuites de la technologie?

Ils ont trouvé deux façons. Le premier est au niveau du front: si la cause des fuites est une grande profondeur d'implantation, réduisons-la, de préférence radicalement. La technologie du silicium sur isolant (SIC) est connue depuis très longtemps (et a été activement utilisée toutes ces années, par exemple, dans les processeurs AMD 130-32 nm, le processeur du décodeur Sony Playstation 3 90 nm, ainsi que dans l'électronique radiofréquence, électrique ou spatiale), mais avec une diminution des normes de conception, elle a eu un second souffle.

Figure 12. Comparaison des transistors réalisés à l'aide des technologies conventionnelles volumétriques et FDSOI (SOO entièrement épuisées).

Source - ST Microelectronics .Comme vous pouvez le voir, l'idée est plus qu'élégante - l'oxyde est situé sous une couche active très mince, éliminant le courant de fuite nocif sur la vigne! Dans le même temps, en raison d'une diminution de la capacité des jonctions pn (quatre des cinq côtés du cube de drainage ont été supprimés), la vitesse augmente et la consommation d'énergie diminue. C'est pourquoi maintenant la technologie FDSOI 28-22-20 nm est activement annoncée comme une plate-forme pour les puces Internet des objets - la consommation est vraiment réduite plusieurs fois, sinon d'un ordre de grandeur. Et pourtant, cette approche permet à l'avenir de mettre à l'échelle le transistor plat conventionnel à un niveau de 14-16 nm, ce que la technologie volumétrique ne permettra plus.

Néanmoins, le FDSOI ne tombe pas particulièrement en dessous de 14 nm, et la technologie a également d'autres problèmes (par exemple, le coût extrêmement élevé des substrats SOI), en rapport avec lesquels l'industrie est arrivée à une autre solution - les transistors FinFET. L'idée d'un transistor FinFET est également assez élégante. Voulons-nous que la majeure partie de l'espace entre le drain et la source soit contrôlée par l'obturateur? Entourons donc cet espace d'un volet de tous les côtés! Eh bien, pas tous, trois suffiront.

Figure 13. Structure FinFET.

Source - A. Tahrim et.al., «Design and Performance Analysis of 1-Bit FinFET Full Adder Cells for Subthreshold Region at 16 nm Process Technology», Journal of Nanomaterials, 2015Figure 14. Comparaison de la consommation d'énergie de différentes options d'additionneur effectuées sur des transistors planaires et sur FinFET.

Source - A. Tahrim et.al., «Design and Performance Analysis of 1-Bit FinFET Full Adder Cells for Subthreshold Region at 16 nm Process Technology», Journal of Nanomaterials, 2015Dans FinFET, le canal n'est pas plat et est situé directement sous la surface du substrat, mais forme une ailette verticale (Fin est l'ailette), dépassant de la surface et entourée d'un obturateur sur trois côtés. Ainsi, tout l'espace entre le drain et la source est contrôlé par un obturateur, et les fuites statiques sont fortement réduites. Les premiers FinFET à être produits en masse étaient Intel aux normes de conception de 22 nm, le reste a été tiré par d'autres fabricants de premier plan, y compris un apologiste KNI tel que Global Foundries (ancien AMD).

La verticalité du canal dans FinFET, entre autres, vous permet d'économiser sur la zone cellulaire, car FinFET avec un canal large est assez étroit en projection, et cela, à son tour, a encore aidé les spécialistes du marketing avec leurs histoires sur la zone de la cellule mémoire et sa double diminution à chaque nouvelle étape "normes de conception", non plus liée aux dimensions physiques du transistor.Figure 15. Topologies des différentes options pour les cellules de mémoire (5T-9T) en technologie avec FinFET. Source - M. Ansari et. al., «Une cellule SRAM 7T à seuil proche avec des marges d'écriture et de lecture élevées et un temps d'écriture faible pour les technologies FinFET inférieures à 20 nm», VLSI Journal on Integration, Volume 50, juin 2015.Voici des exemples de différentes options pour les cellules de mémoire dans la technologie avec FinFET. Vous voyez comment la largeur géométrique du canal est beaucoup plus petite que la longueur? Vous pouvez également voir que, malgré toutes les perturbations, le système lambda chez les topologues est toujours utilisé pour les estimations quantitatives. Et qu'en est-il des nombres absolus?Figure 16. Certaines tailles de transistors dans les technologies 14-16 nm.

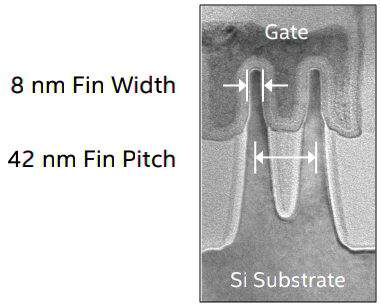

Source - actes de la conférence ConFab 2016.Comme le montre la figure, la longueur du canal topologique dans les technologies FinFET à 16 nm est toujours supérieure à 20-25 nm, qui ont été mentionnées ci-dessus. Et c'est logique, car la physique ne peut pas être dupe. Mais une autre conclusion, plus intéressante, peut être tirée de la même figure: si vous regardez de plus près, il devient clair que la taille minimale disponible dans les transistors n'est pas la longueur du canal, mais la largeur des ailettes. Et ici, une drôle de découverte nous attend: la largeur des ailettes dans la technologie de processus Intel de 16 nm est (rouleau de tambour!) HUIT nanomètres. Figure 17. Dimensions des ailettes dans la technologie de traitement Intel 14 nm.

Figure 17. Dimensions des ailettes dans la technologie de traitement Intel 14 nm.

Source - wikichip.orgComme vous pouvez le voir, ici les commerçants, attachés à la taille de la cellule mémoire, se sont trompés et sont maintenant obligés d'exprimer le chiffre plus qu'ils ne le pouvaient. En fait, bien sûr, dans des conditions de changement fondamental dans la structure du transistor et dans l'attente des utilisateurs d'entendre une sorte de métrique, l'utilisation d'une métrique qui reflète la densité d'emballage était probablement la seule bonne décision, et les commerçants avaient finalement raison, même si cela conduit parfois à situations drôles où les mêmes normes de conception dans différentes entreprises sont appelées différemment. Par exemple, en lisant les informations selon lesquelles TSMC a déjà lancé le 7 nm et Intel retarde à nouveau le début de la production du 10 nm, il convient de rappeler que le TSMC 7 nm et le Intel 10 nm sont en fait les mêmes normes de conception en termes de et la densité d'emballage, et la taille des transistors individuels.Et ensuite? En fait, personne ne le sait. La loi de Moore s'est épuisée il y a assez longtemps, et si il y a dix ans, la réponse à la question «et ensuite?» peuvent être trouvés dans les rapports des centres de recherche, on entend de plus en plus souvent que les développements prometteurs doivent être abandonnés, car ils s'avèrent excessivement difficiles à mettre en œuvre. Cela s'est déjà produit avec des plaquettes d'un diamètre de 450 millimètres, c'est en partie le cas avec la lithographie EUV (que les scientifiques ont utilisé pendant vingt ans), et cela se produira probablement avec des transistors sur graphène et nanotubes de carbone. Une autre percée technologique est nécessaire, mais le chemin à parcourir, malheureusement, n'est pas encore visible. Il est arrivé au point que le nouveau directeur de TSMC Mark Liu a appeléLa direction la plus prometteuse dans le développement de la technologie microélectronique n'est pas la réduction de la taille des transistors, mais l'intégration 3D. L'intégration «vraie» 3D, plutôt que de combiner plusieurs puces dans un même boîtier, sera en effet une étape importante dans le développement de la microélectronique, mais la loi de Moore, comme la loi de réduction de la taille des transistors, semble être complètement morte.