Le quadruple débit de données (QDR-IV) est une norme de mémoire haute performance pour les applications réseau et est idéal pour la prochaine génération de périphériques réseau, d'équipements de communication et de systèmes informatiques.

QDR-IV SRAM dispose d'une unité intégrée de détection et de correction d'erreurs (ECC) pour garantir l'intégrité des données. Cette unité est capable de traiter toutes les erreurs de mémoire sur un seul bit, y compris celles causées par les rayons cosmiques et les particules alpha. Par conséquent, les modules de mémoire auront un taux d'erreur de programme (SER) ne dépassant pas 0,01 échecs / Mo. QDR-IV est équipé d'une fonction de parité d'adresse programmable qui garantit l'intégrité des données sur le bus d'adresse.

Caractéristiques distinctives de la mémoire QDR SRAM:

- Le module de correction d'erreurs intégré garantit l'intégrité des données et élimine les erreurs logicielles

- Les modules sont disponibles en deux versions: QDR-IV HP (débit de données 1334 Mtrans / s) et QDR-IV XP (débit de données 2132 Mtrans / s)

- Deux ports de données de mémoire DDR1 bidirectionnels indépendants

- Fonction d'inversion de bus pour réduire le bruit lors de la connexion des lignes d'entrée et de sortie

- Le schéma de négociation intégré (ODT) réduit la complexité des cartes

- Entraînement asymétrique pour améliorer la synchronisation de la capture du signal

- Puissance du signal d'E / S: 1,2 V à 1,25 V (logique émetteur-récepteur haute vitesse (HSTL) / logique terminée (SSTL)), 1,1 V à 1,2 V (POD2)

- Boîtier FCBGA3 361 broches

- Largeur du bus: x18, x36 bits

Présentation

L'Assistant DDRx est un outil facile à utiliser dans HyperLynx qui vous permet de contrôler par lot les formes d'onde temporelles et d'analyser l'intégrité du signal des protocoles DDR JEDEC standard. L'assistant DDRx peut être lancé à la fois au stade de l'analyse pré-topologique selon le scénario «what if» et sur une carte entièrement tracée. De plus, l'outil vous permet d'importer la plupart des formats de modèles créés par les principaux fournisseurs de puces.

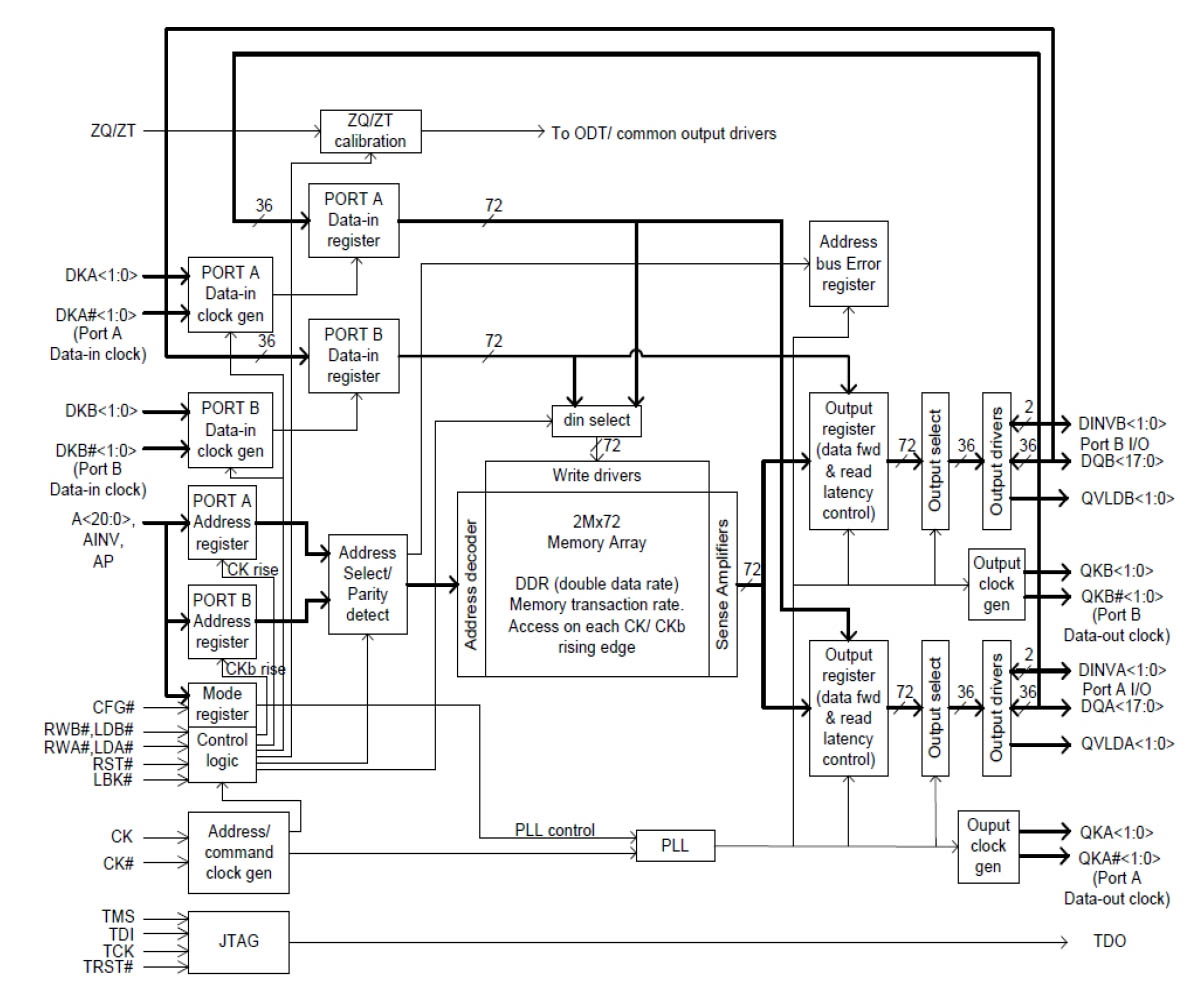

L'assistant DDRx vous permet de vérifier tous les bits du bus mémoire pour vérifier la conformité avec l'intégrité du signal, ainsi que la conformité aux exigences de synchronisation entre les signaux. Cet article détaille l'utilisation de l'assistant interactif pour analyser les projets mettant en œuvre le protocole QDR4 (Fig. 1).

Fig. 1. L'architecture interne de QDR sur l'exemple du module CY7C4142KV13 (cliquable)

Fig. 1. L'architecture interne de QDR sur l'exemple du module CY7C4142KV13 (cliquable)Premier aperçu de QDR-IV dans HyperLynx DDRx WIZARD

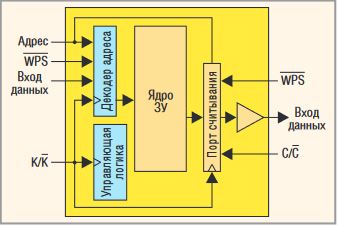

Le protocole QDR-IV définit deux paires unidirectionnelles d'un signal d'échantillonnage de données: l'une pour la lecture de données, l'autre pour l'écriture, qui prennent en charge indépendamment les unes des autres les opérations et les opérations de lecture et d'écriture simultanées, et les ports peuvent fonctionner à différentes fréquences (Fig.2). Ainsi, le risque de dysfonctionnement est totalement éliminé.

Fig. 2. Disponibilité de ports de lecture et d'écriture séparés dans l'architecture QDR SRAM

Fig. 2. Disponibilité de ports de lecture et d'écriture séparés dans l'architecture QDR SRAMPour ce protocole, l'assistant DDRx utilisera des portes distinctes pour lire et écrire des données. QDR IV est généralement implémenté à l'aide d'un bus x36 ou x18 bits (voir Fig. 3a et 3b).

L'assistant DDRx active la simulation QDR-IV en trois étapes:

- Vérification de la lecture des données

- Vérification des enregistrements de données

- Vérification d'adresse / de bus de contrôle

Étant donné que les vérifications d'adresse / de bus de contrôle peuvent être effectuées indépendamment des vérifications de lecture / écriture de données, cela peut vous faire gagner du temps en combinant cette étape avec l'une des étapes de test des données. Ce qui suit décrit les trois scénarios pour ces tests.

Caractéristiques technologiques

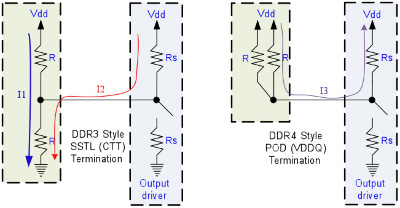

QDR-IV prend en charge la technologie de pseudo-drain ouvert (POD) et la logique de terminaison SSTL (Stub Series Terminated Logic) (figure 4).

Fig. 4. Différences entre POD et SSTL

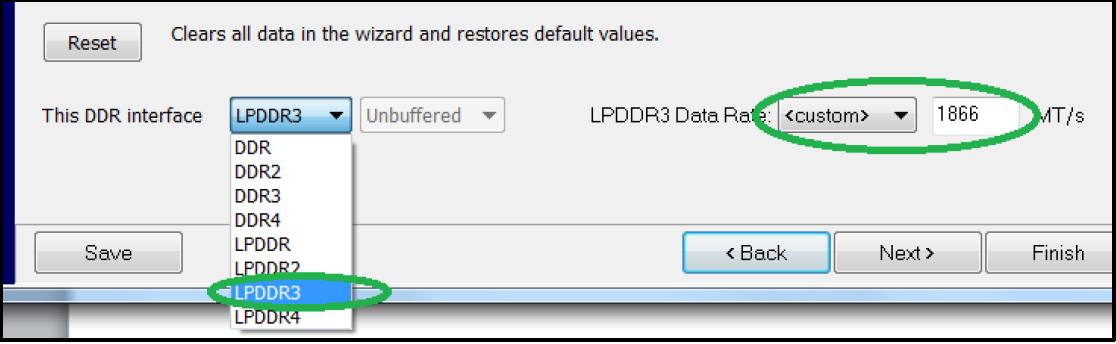

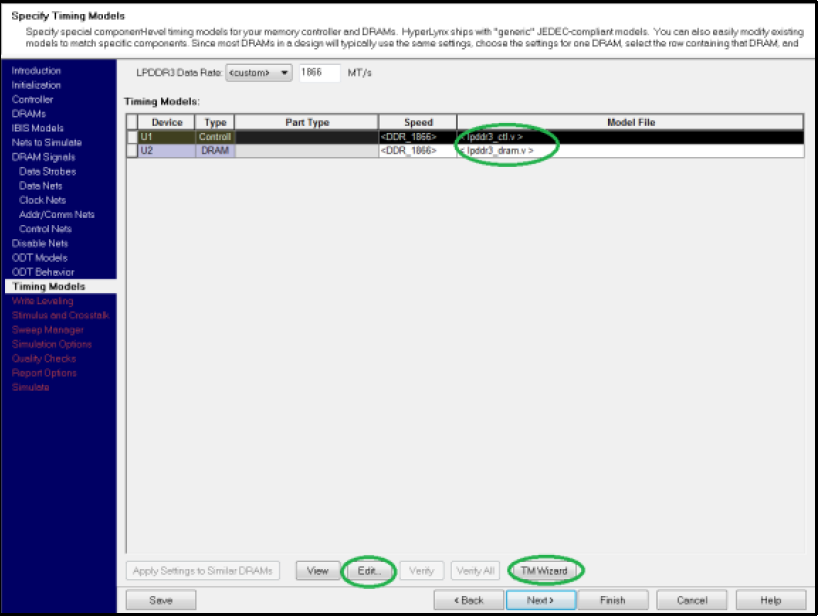

Fig. 4. Différences entre POD et SSTLQuelle que soit la norme logique utilisée, sélectionnez

LPDDR3 comme technologie (Fig.5), car il n'y a pas de support pour la

formation Vref , comme c'est le cas avec le module POD du DDR4. À la place, des valeurs fixes Vref et Vinh / Vinl sont utilisées, similaires à DDR3 et LPDDR3. Étant donné que QDR-IV utilise un double débit pour les signaux d'adresse tels que LPDDR3, il est recommandé de sélectionner cette option. Ensuite, saisissez le taux de transfert des données utilisateur, par exemple 1866 MT / s ou 2133 MT / s, où MT / s est le nombre de mégatransfert par seconde (mégatransfert par seconde).

Fig. 5. Le choix d'une logique standard

Fig. 5. Le choix d'une logique standardSignal de données: opération de lecture

Pour les opérations de lecture de signaux de données, la DRAM contrôlera les signaux DQ en conjonction avec les signaux QK stroboscopiques différentiels. Ainsi, la configuration se concentre sur l'opération de lecture des données et affecte les circuits (signaux) nécessaires à la porte QK correspondante.

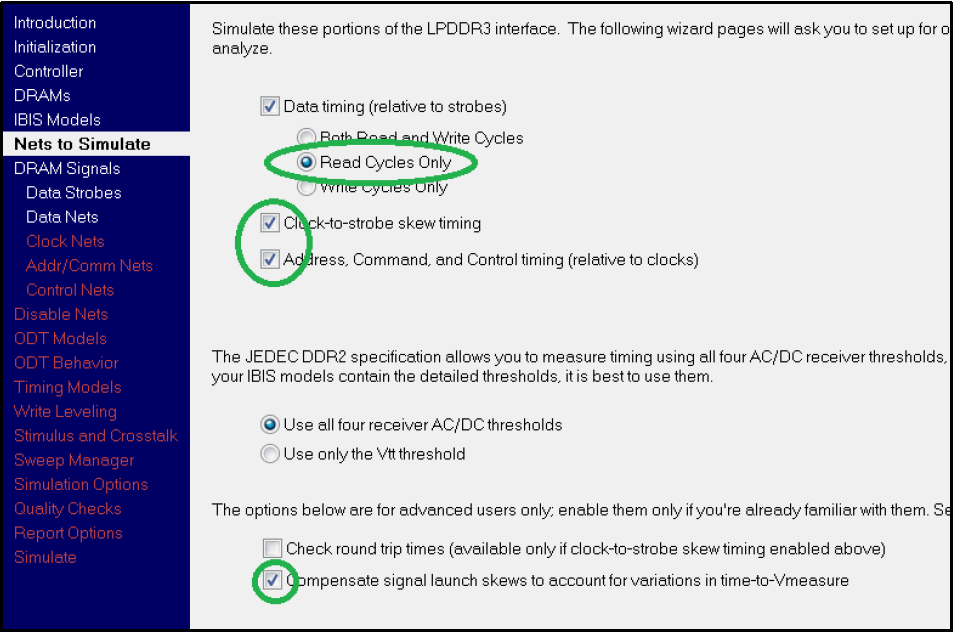

Dans la section

Filets à simuler (figure 6), cochez la case «

Cycles de lecture uniquement ». Les

cases à cocher Clock-to-strobe et Address checks sont facultatives.

Vérifiez également l'installation des

asymétries de lancement du signal de compensation pour prendre en compte les variations du délai de mise à jour .

Fig. 6. Lecture des données

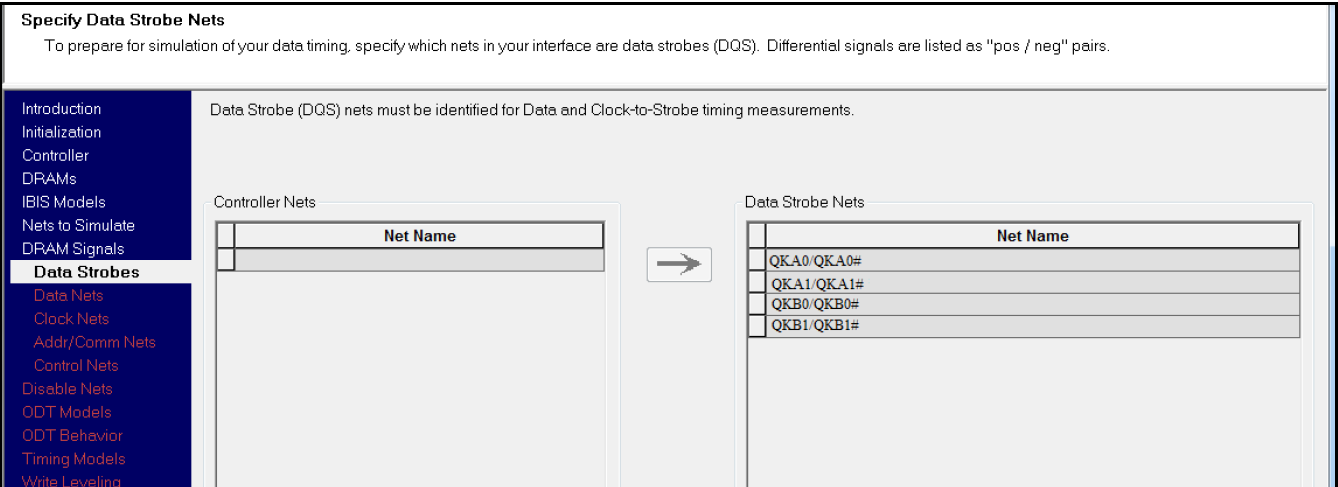

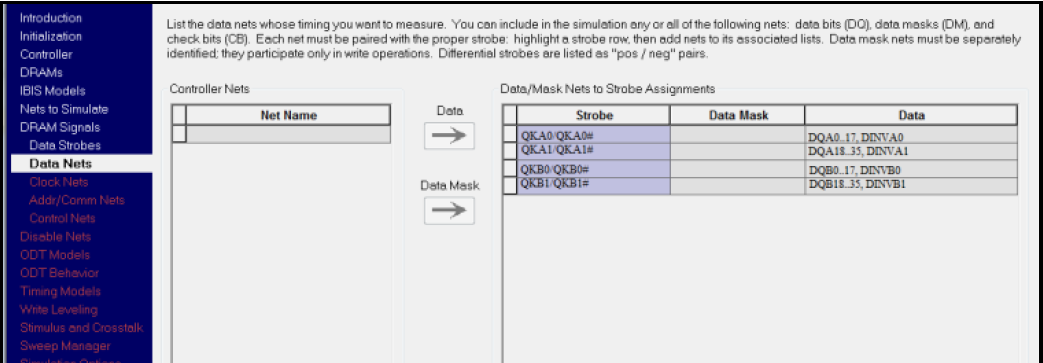

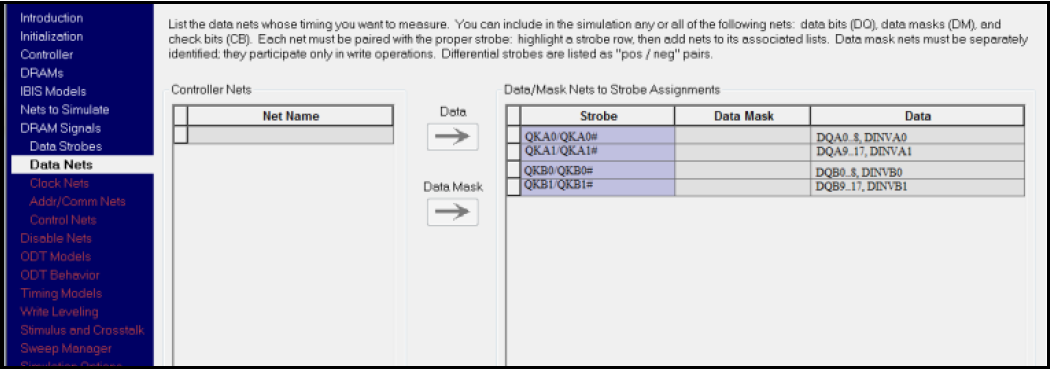

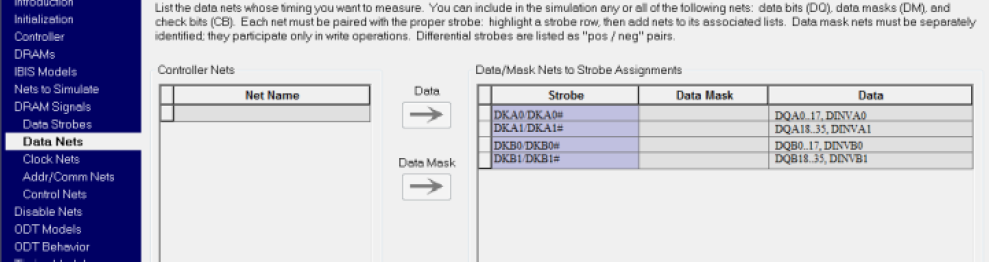

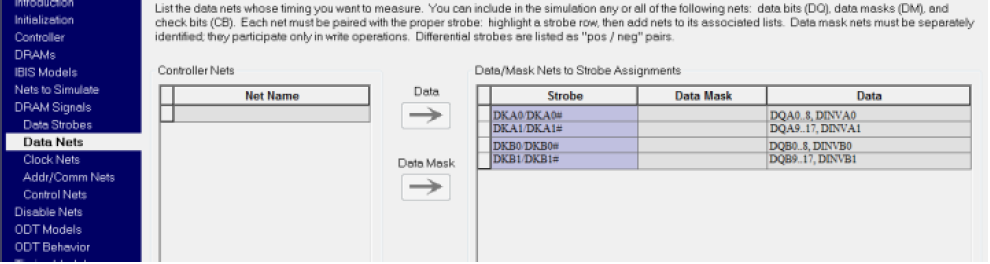

Fig. 6. Lecture des donnéesAssurez-vous que tous les stroboscopes de données nécessaires sont sélectionnés (figure 7).

Dans la section

Data Nets , vérifiez que chaque signal correspond correctement à chaque porte. Veuillez noter que les signaux sont différents pour les bus x18 et x36 bits, assurez-vous donc que le brochage est adapté à votre cas particulier (Fig. 8a et 8b).

Fig. 7. Lecture des données stroboscopiques

Fig. 7. Lecture des données stroboscopiques Fig. 8a. Groupe de signaux pour bus 36 bits

Fig. 8a. Groupe de signaux pour bus 36 bits Fig. 8b. Groupe de signaux pour le bus 18 bits

Fig. 8b. Groupe de signaux pour le bus 18 bitsLe test du bus parallèle est généralement effectué en réglant / maintenant le temps entre le stroboscope et le signal. Toutes ces exigences, en plus d'autres valeurs temporaires, sont requises par l'Assistant DDRx pour vérifier les résultats. Ces valeurs peuvent différer d'une puce à l'autre, il est donc recommandé de saisir des valeurs qui s'appliquent à un périphérique de mémoire spécifique. De plus, les informations de synchronisation par défaut pour LPDDR3 ne sont pas compatibles avec QDR-IV. Ainsi, toutes les informations de synchronisation pour QDR-IV doivent être saisies et correspondre à la documentation de votre puce.

Cela peut être fait à l'aide de l'

assistant de synchronisation (Fig.9), qui invite l'utilisateur à remplir plusieurs formulaires pour la génération ultérieure de valeurs temporaires, ou vous pouvez modifier les fichiers de synchronisation .V qui correspondent à votre contrôleur et à la DRAM.

Fig. 9. Définition des valeurs de synchronisationAttention

Fig. 9. Définition des valeurs de synchronisationAttention : la simulation étant réalisée en mode

LPDDR3 , les résultats doivent être interprétés en conséquence.

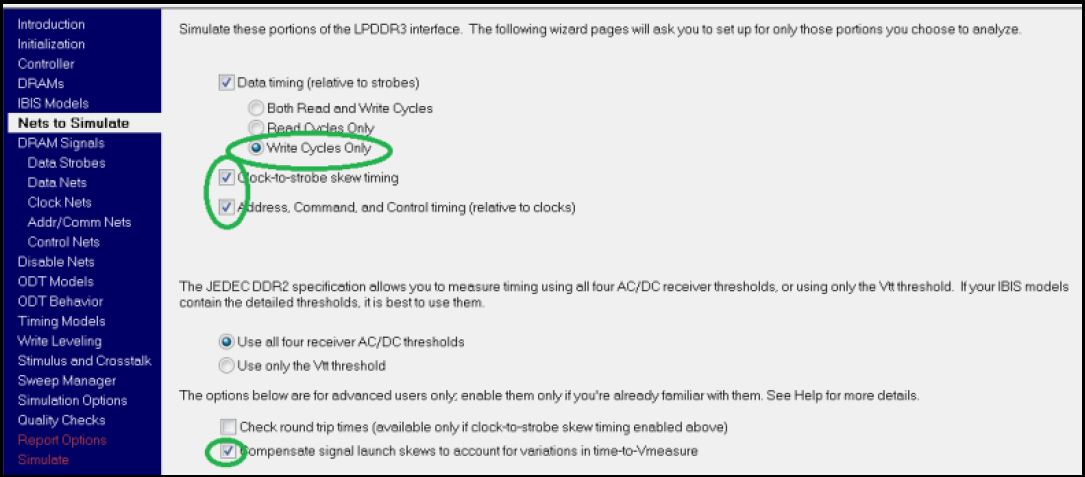

Signal de données: opération d'écriture

L'opération d'écriture de données et son analyse sont similaires à l'analyse de l'opération de lecture décrite ci-dessus. Mais il y a deux différences clés que nous allons maintenant considérer. À l'exception de ces deux nuances, les étapes de l'opération de lecture des données peuvent être répétées pour simuler l'écriture des données.

Dans la section

Filets à simuler (figure 10), assurez-vous que l'

option Écrire les cycles uniquement est sélectionnée.

Il est également possible de simuler

des opérations d'écriture de signal d'adresse . Et n'oubliez pas de vous assurer que la

case à cocher Compensate Skew Launch pour tenir compte des variations du délai de vérification est cochée .

Fig. 10. Enregistrement des données

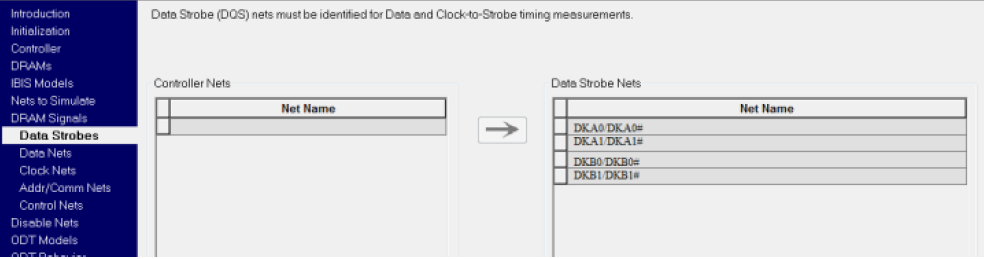

Fig. 10. Enregistrement des donnéesAssurez-vous que les bonnes portes sont sélectionnées dans la section

Data Strobe (Figure 11). La principale différence entre une transaction de lecture et une transaction d'écriture est le stroboscope utilisé pour synchroniser les données; ce stroboscope est différent du stroboscope utilisé pour l'opération de lecture de données (figures 12 et 13).

Fig. 11. Portes des données d'enregistrement

Fig. 11. Portes des données d'enregistrement Fig. 12. Groupes de signaux de signal stroboscopique (bus 36 bits)

Fig. 12. Groupes de signaux de signal stroboscopique (bus 36 bits) Fig. 13. Groupes de signaux de signal stroboscopique (bus 18 bits)

Fig. 13. Groupes de signaux de signal stroboscopique (bus 18 bits)Adresse, commande et contrôle du bus

Le QDR-IV utilise des verrouillages différentiels CK / CK # pour sélectionner les signaux de commande, l'adresse et les signaux de commande. Le bord avant du signal CK est utilisé pour entrer des informations sur le port A, et le bord arrière est utilisé pour sélectionner des informations sur le port B.

Compte tenu de l'intégrité du signal, les formes d'onde des lignes d'adresse doivent répondre aux exigences d'installation et aux retards des fronts avant et arrière du signal d'horloge. Ceci est très similaire au comportement de LPDDR3.

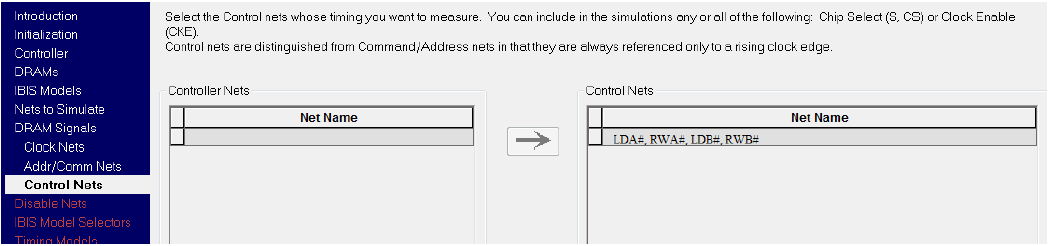

Les signaux

LDA #, LDB #, RWA # et RWB # sont synchronisés au même débit de données (débit de données unique). Cela signifie que ces signaux sont synchronisés uniquement sur l'un des deux fronts des impulsions d'horloge. Les signaux LDA # et RWA # sont synchronisés sur le front montant de l'horloge et les signaux LDB # et RWB # sont sur le front descendant.

Les blocs sont largement symétriques - le différentiel avant avant n'est pas très différent de l'arrière. Cela signifie que pour garantir l'intégrité du signal, les valeurs de synchronisation pour

LDB # et RWB # doivent être presque les mêmes, sinon identiques, lors de l'échantillonnage sur les fronts montant ou

descendant de l' horloge. Les signaux de commande LPDDR3 sont également synchronisés uniquement sur le front montant.

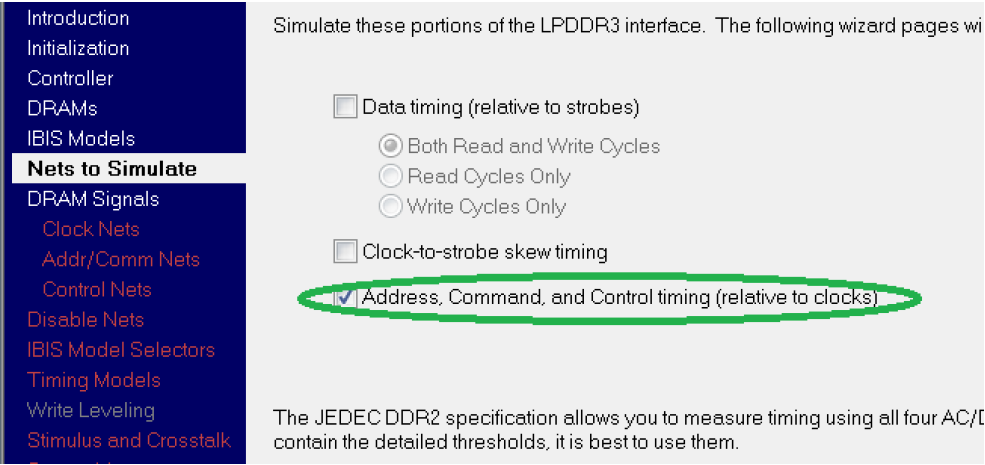

Les étapes suivantes sont spécifiques à la simulation de bus d'adresses, de bus de commande et de contrôle à l'aide de QDR-IV.

Assurez-vous que dans la section

Filets à simuler , la case à cocher

Adresse, commande et contrôle (par rapport aux horloges) est

cochée (Fig. 14).

Fig. 14. Cochez la case Address, Command and Control timing

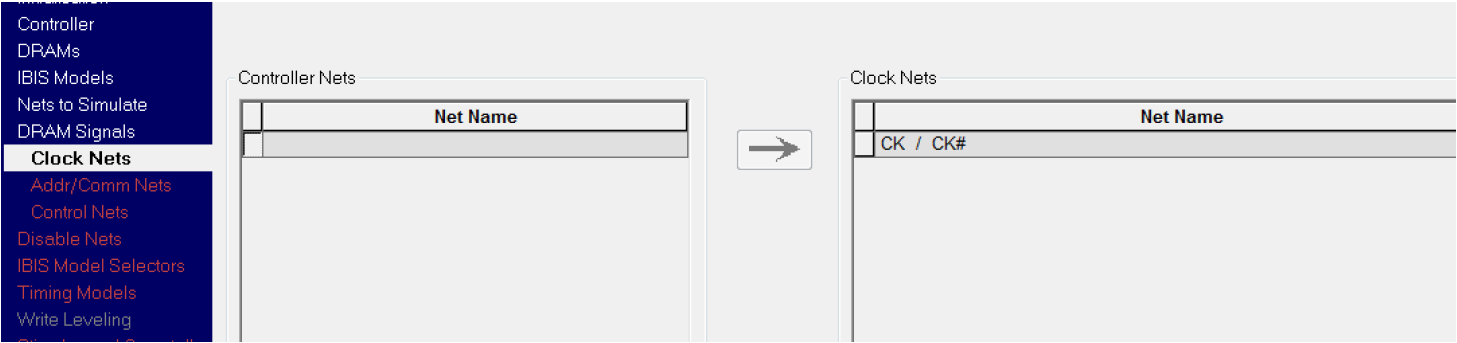

Fig. 14. Cochez la case Address, Command and Control timingDans la section

Filets d'horloge , assurez-vous que la paire différentielle de signaux d'horloge CK / CK # est sélectionnée (Fig. 15).

Fig. 15. Le choix de l'horloge différentielle

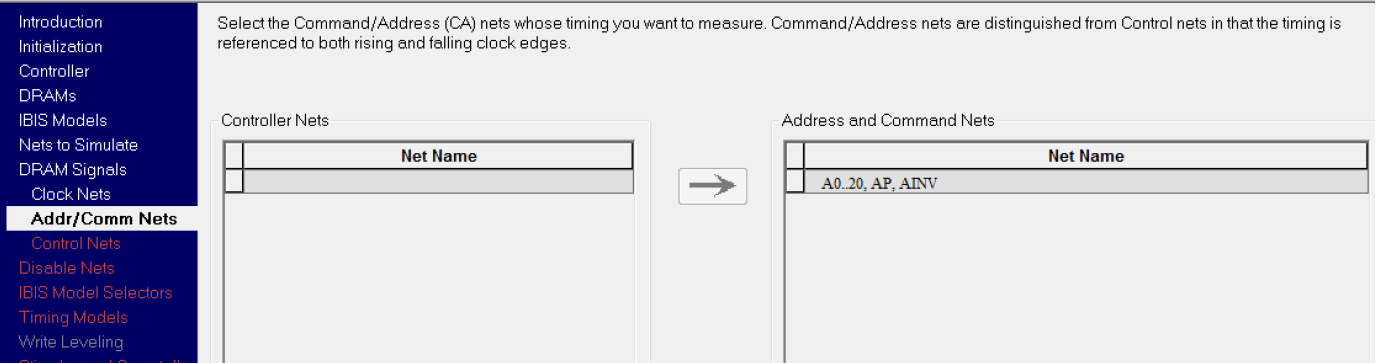

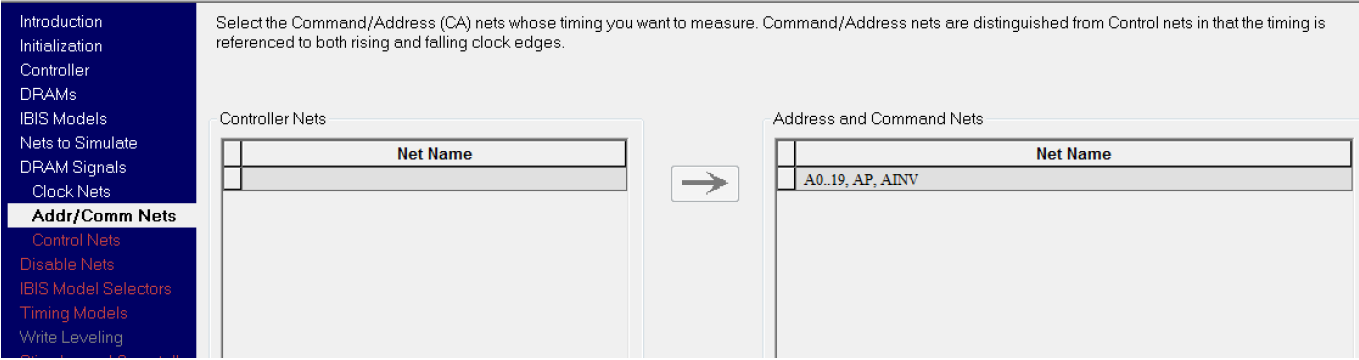

Fig. 15. Le choix de l'horloge différentielleDans la section

Addr / Comm Nets , assurez-vous que les bits

A [20: 0] sont sélectionnés pour les périphériques avec x36 bits et les bits

A [19: 0] sont sélectionnés pour les périphériques avec x18 bits. De plus, réglez les

signaux AP et AINV (

Fig.16 et 17).

Fig. 16. Paramètres pour les bus x36 bits

Fig. 16. Paramètres pour les bus x36 bits Fig. 17. Paramètres pour les bus x18 bits

Fig. 17. Paramètres pour les bus x18 bitsDans la section

Control Nets , sélectionnez les signaux LDA #, LDB #, RWA # et RWB # (Figure 18).

Fig. 18. Signaux de commande

Fig. 18. Signaux de commandeComme pour la modélisation d'un signal de données, assurez-vous que vous utilisez les bons fichiers avec des paramètres de synchronisation. Le reste de la modélisation et de l'évaluation des résultats est similaire à LPDDR3.

«Interprétation des résultats du rapport HyperLynx DDRx»Conclusion

En suivant les instructions simples de cet article, vous pouvez bénéficier et utiliser le package d'assistance de l'assistant DDRx pour simuler et tester les bus QDR-IV.

J'espère que ce manuel sera utile à quelqu'un.

Cordialement, Filipov Bogdan (

pbo ).

Profitant également de cette occasion, je souhaite inviter les développeurs de la REU à un séminaire organisé par Nanosoft et Mentor Graphics:

«Une nouvelle génération de solutions de conception d'appareils électroniques de Mentor Graphics»