Salutations, Habr! Je m'appelle Daniil Smirnov, j'étudie à l'école supérieure de l'Université ITMO, où notre équipe est engagée dans l'électronique programmable pour des projets liés aux capteurs à fibre optique dans le laboratoire de programmation et de modélisation. En tant que base matérielle pour les capteurs, des FPGA sont utilisés - Array Programmable Gate Array. Il y a quelques années, nous avons appris que les fabricants de FPGA organisent des compétitions entre étudiants en développement. Depuis lors, chaque année, une équipe est formée de nous pour participer à cet événement, et comme cette année s'est avérée spéciale, nous avons décidé de partager comment tout se passait de l'intérieur.

Entrée

C'était en octobre 2017, j'ai fait un contrôle de routine hebdomadaire: une analyse des conférences en cours sur des sujets qui sont mis en œuvre dans notre département. À un moment donné, je reçois une newsletter de Terasic: un

nouveau concours démarre

sur le développement de projets utilisant des cartes de débogage sur le FPGA , désormais mondial. L'expérience de la même compétition de l'année dernière me passe par la tête et me rappelle: le report jusqu'aux deux dernières semaines du mois, le long débogage et le réglage des algorithmes et l'émission de tous les canaux sur le moniteur et une promesse de ne pas le remettre au dernier jour.

Ce fut une expérience cool, au cours de laquelle nous avons beaucoup appris sur une plate-forme telle que SoC FPGA - l'interconnexion d'un vaste éventail d'éléments logiques et du processeur Cortex-A9, ainsi que leur interaction les uns avec les autres et avec les périphériques sur la carte de débogage.

Nouvelle compétition - nouvelles règles, nouvelles exigences, un nouveau niveau. Maintenant, la compétition se déroule en plusieurs étapes: d'abord, les étapes régionales ont lieu, puis la finale à San Jose; la carte est envoyée à tous les participants de la même façon,

DE10-Nano , et en plus maintenant vous pouvez choisir non seulement les trois modules de base, mais aussi une grande version des cartes d'Analog Devices! Cependant, contrairement aux compétitions des années précédentes, cette fois, il est nécessaire de signer une garantie du projet, et en cas de non-exécution, les participants doivent renvoyer les frais. C'est assez juste, compte tenu des statistiques des dernières années:

<...> 71 équipes de 20 pays européens ont inscrit le concours <...> 25 juges de l'industrie (ALTERA) et du milieu universitaire (CNFM) en France ont examiné les 32 projets [1].

Le conseiller scientifique, comme les étudiants qui voulaient s'impliquer dans ce travail, était déjà sous une lourde charge sur divers projets, mais l'excitation pendant le concours et la motivation d'apprendre beaucoup de nouvelles choses sont devenues des arguments de poids pour participer à nouveau au concours. Restait à trouver un projet avec lequel vous pouvez postuler.

Idée de projet

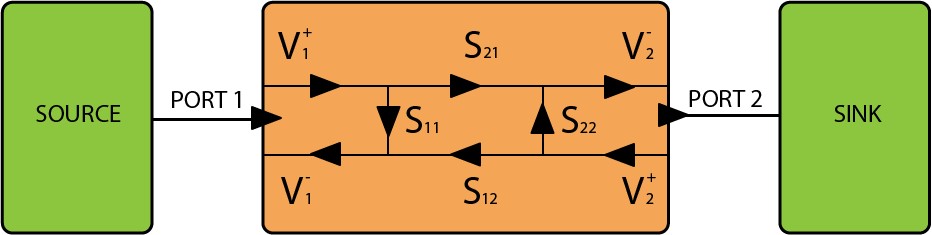

Afin que le projet ne soit pas mis de côté, il a été décidé de mettre en place un dispositif utile pour le département, qui pourrait par la suite être facilement développé et amélioré. En fonction des domaines d'activité du département, il y avait différentes options: un réflectomètre optique, un oscilloscope stroboscopique, etc. En examinant rapidement les applications existantes et les cartes supplémentaires disponibles, il a été révélé que le réflectomètre était déjà annoncé, mais un oscilloscope stroboscopique ne pouvait pas être assemblé sur de tels éléments. La seule idée qui reste vivante est l'analyseur de réseau vectoriel. L'autre jour, deux bobines ont été introduites dans le laboratoire, pour lesquelles il n'y avait aucune documentation. La tâche consistait à déterminer au moins les caractéristiques approximatives de ces bobines. On savait que le circuit oscillatoire y était assemblé, la tâche principale était donc de trouver la fréquence de résonance. Dans de telles tâches, un analyseur de réseau vectoriel (VAC ou VNA - Vector Network Analyzer) peut simplement trouver une application. VNA vous permet de définir une matrice de dispersion, également connue sous le nom de matrice de paramètres S. Dans cette méthode, l'élément à l'étude est considéré comme une boîte noire, dans laquelle les signaux incidents et réfléchis des ports de cet appareil sont analysés. Ainsi, pour un système à deux ports, la matrice est la suivante:

Où V1 + V2 + sont des ondes électromagnétiques arrivant aux ports;

V1- V2- - ondes électromagnétiques quittant les ports;

Sij sont des éléments de la matrice de diffusion à trajets multiples. [2]

Schéma de mesure des paramètres S d'un multipôle

Schéma de mesure des paramètres S d'un multipôleNous n'avons pas examiné les composants et le circuit à l'aide d'une radiographie (au moins par la radiographie du métro), donc le circuit suivant a été assemblé sur les genoux: les fréquences ont été réglées en alternance avec une étape dans le circulateur jusqu'à l'entrée de la bobine à l'aide d'un générateur, le deuxième port du circulateur a été connecté à l'entrée de la bobine et la troisième entrée à un oscilloscope ayant dans son logiciel le mode d'analyse amplitude-fréquence. Un tel circuit permet de mesurer le paramètre S11, c'est-à-dire réflexion. Au final, après beaucoup d'angoisse et de calibration, j'ai réussi à supprimer cette caractéristique - mais à quel prix? Le département s'attendait depuis longtemps à l'acquisition d'un analyseur de réseau vectoriel pour des tâches similaires (mesure de l'AFC des appareils radioélectroniques), mais cet achat a toujours été en quelque sorte retardé.

Après l'agitation avec les bobines, il a été décidé d'assembler votre propre analyseur de circuit avec visualisation et réglage confortable. Il n'est pas difficile de trouver de l'enthousiasme et un désir d'apprendre quelque chose de nouveau auprès des étudiants et des étudiants diplômés travaillant au département.L'équipe a donc été rapidement constituée d'un ingénieur en électronique, d'un programmeur-développeur de systèmes sur puce, de moi et de deux mentors.

Aussitôt dit, aussitôt fait! Après de nombreuses discussions sur la bande de fréquences, les algorithmes de traitement et d'autres paramètres du projet, l'application contenait les éléments suivants:

- Le projet revendiqué est un analyseur de circuits vectoriel basé sur SoC FPGA sur une carte DE10-Nano;

- Cartes supplémentaires demandées: une carte avec un générateur de fréquence programmable, un mélangeur haute fréquence et une carte avec un CAN;

- Plage de fréquences de fonctionnement: selon les paramètres présentés de cartes supplémentaires;

- Possibilités d'extension rapide du nombre de ports connectés;

- La sortie de la composante d'amplitude et de phase à l'écran;

- Autres fonctions d'entrée / sortie de base pour l'analyseur de réseau vectoriel.

Pour passer à l'étape suivante, il a fallu que la page du projet gagne un nombre suffisant de «likes» des utilisateurs qui se sont inscrits sur le site. Au début, tout s'est bien passé, mais ensuite certains projets douteux ont commencé à gagner des valeurs irréalistes et contrastées de likes et de vues par rapport à d'autres projets. Il s'est avéré que le site du concours était trop vulnérable à la tricherie.

Après un certain temps, les organisateurs ont informé que le jury choisirait toujours les finalistes, de sorte que les goûts des utilisateurs ont en fait perdu du poids. Le 31 janvier, notre équipe est apparue dans les listes de ceux qui sont passés à l'étape suivante et nous avons commencé à réfléchir plus en détail à notre projet en prévision du débogage.

Une dure réalité

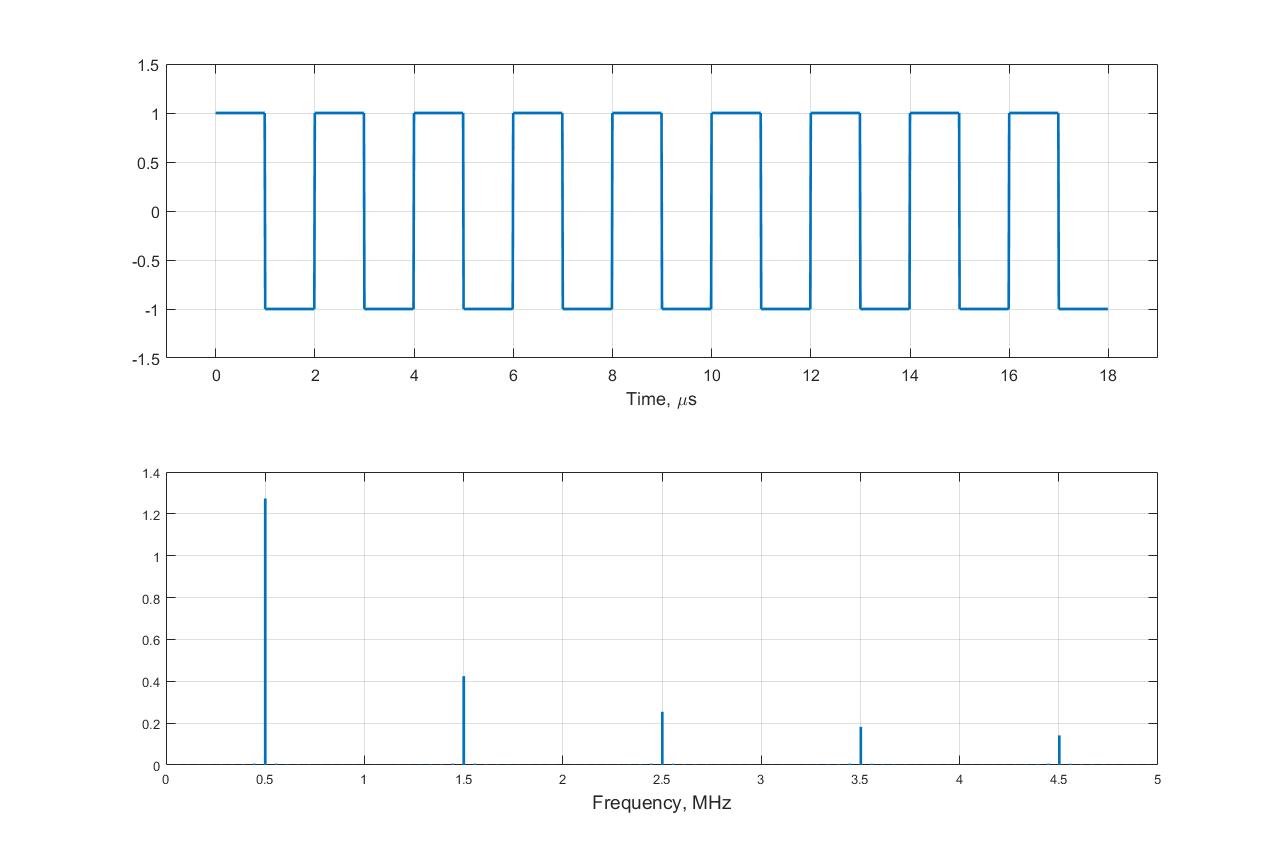

La première est venue la carte DE10-Nano. Agréable, mais un peu étrange: ils s'attendaient à ce que les planches se rejoignent. Quelques jours plus tard, un appel vient de la douane: les frais sont venus, ils dépassent tous ensemble le seuil de prix, vous devez donc payer pour le dédouanement un montant approximativement égal au coût de ces frais. Une telle situation nous a bouleversés, mais ne nous convenait pas: nous avons refusé les planches. En présence de mélangeurs et de générateurs que nous n'avions pas, il faut trouver de nouvelles solutions. Que faire? La première chose qui m'est venue à l'esprit n'était pas la solution la plus précise, mais plutôt inhabituelle: utiliser la jambe GPIO habituelle et en générer un méandre. Un filtre passe-bas analogique est installé à la sortie de ce pied avec une bande de coupure légèrement supérieure à la fréquence maximale du méandre. Pour commencer, il a été proposé d'inclure l'analyse à partir de 1 MHz (par exemple): puis après le filtre, nous aurions un sinus plus ou moins pur (les harmoniques les plus élevées seraient coupées par le filtre), et ainsi de suite jusqu'à ce que la fréquence tombe à celle à laquelle le signal après le filtre il y aura deux harmoniques. Le méandre est la somme des harmoniques impaires, et la contribution proportionnelle de chaque harmonique est connue à l'avance [3].

Un exemple de méandre dans les domaines temps et fréquence: les composantes du signal harmonique à 500 kHz, 1,5 MHz, etc. sont visibles sur le spectre.

Un exemple de méandre dans les domaines temps et fréquence: les composantes du signal harmonique à 500 kHz, 1,5 MHz, etc. sont visibles sur le spectre.Avec un filtre avec une fréquence de coupure de 1 MHz, vous pouvez descendre à 33. (3) kHz. Après cette fréquence, nous devrions obtenir la somme de deux sinus derrière le filtre. Le rapport proportionnel de leurs amplitudes est connu (fonction sinc), la réponse de l'appareil mesuré à une fréquence de 1 MHz (première harmonique impaire), aussi, nous devons donc composer une équation avec une inconnue et calculer la caractéristique de réponse à une fréquence de 33, (3) kHz! Au début, cette solution semblait trop simple, donc pour commencer, elle a été racontée à tout le monde dans l'espoir que quelqu'un trouverait une erreur. Aucune erreur n'a été trouvée, mais un certain nombre de limites ont été découvertes au cours de la discussion:

- Le pied GPIO n'est pas la meilleure source de méandre, surtout avec une fréquence croissante;

- Souder un filtre compact sur les composants disponibles sera une tâche non triviale;

- Même si ces limitations peuvent être contournées, un problème de synchronisation se pose pour la détection de phase.

Supposons que nous ayons résolu tous les problèmes du côté analogique; par programme, deux autres surgissent:

- Avec une fréquence décroissante, l'erreur de chaque détection et calcul précédents contribuera à la mesure suivante;

- Avec une fréquence décroissante, le temps de calcul des caractéristiques augmentera considérablement.

Et enfin, le dernier mais non le moindre. Le circuit décrit peut être utilisé si l'élément mesuré peut être décrit par une fonction de transfert linéaire. Cependant, si nous mesurons une boîte noire avec des caractéristiques non linéaires - l'idée a plus de problèmes que de bien. Il n'y avait pas beaucoup de temps (le premier résultat devrait être affiché deux mois après l'arrivée de la carte), donc, après quelques délibérations, nous avons décidé de revérifier nos fournitures par rapport aux cartes de débogage existantes - et avons trouvé un

DAC 14 bits à 125 Msps ! Pas la solution la plus élégante, mais pas le choix, nous l'utilisons comme générateur de signal de sortie.

Premier concept

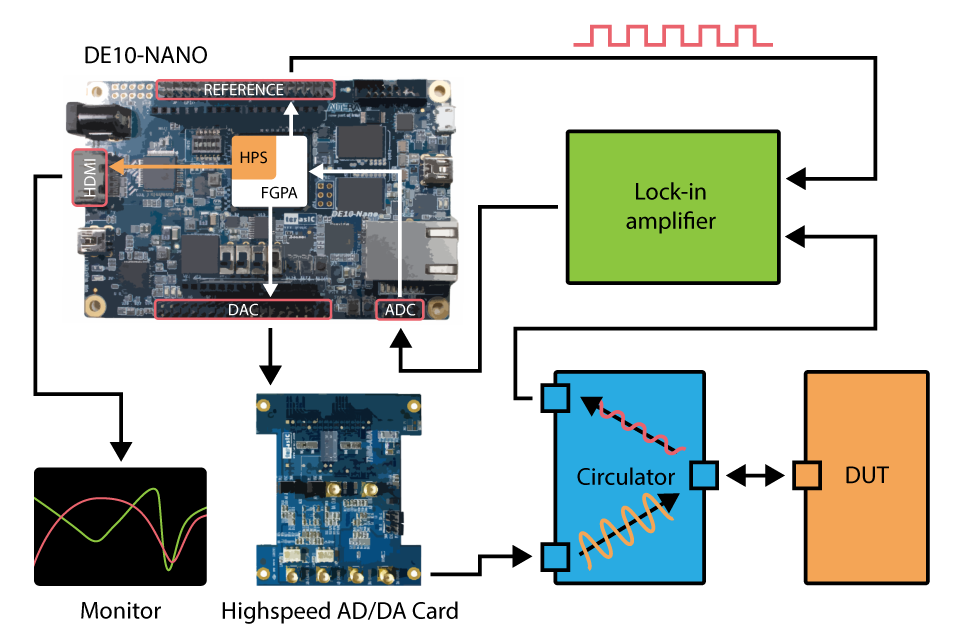

Le DAC sélectionné en tant que générateur reçoit des données à l'entrée du bus parallèle et les verrouille avec un signal d'horloge provenant du FPGA. Un tel circuit est idéal pour la synchronisation dans notre circuit. Cependant, des questions demeurent concernant la détection.

Oui, sur la même carte, il y a un ADC 14 bits à 65 Msps. Mais seules les capacités du générateur sont potentiellement plus élevées, et selon le théorème de Kotelnikov, cet ADC ne fonctionnera plus aux fréquences maximales.

La solution a été trouvée lors d'une discussion de ce problème avec des ingénieurs en électronique expérimentés. Il s'est avéré que pour notre tâche, nous pouvons utiliser un circuit amplificateur à verrouillage: la sortie d'un tel détecteur est deux valeurs constantes, les composantes de phase et de quadrature, à partir desquelles vous pouvez obtenir l'amplitude et la phase du signal, et comme elles sont constantes, elles peuvent être détectées même avec le lent ADC installé sur le DE10-Nano! Il a été décidé de modéliser d'abord le circuit dans LTSpice, puis de sélectionner les composants et d'assembler le circuit, en tenant compte du fait que l'entrée du détecteur est un signal du circulateur et que les sorties sont connectées à l'ADC sur la carte DE10-Nano.

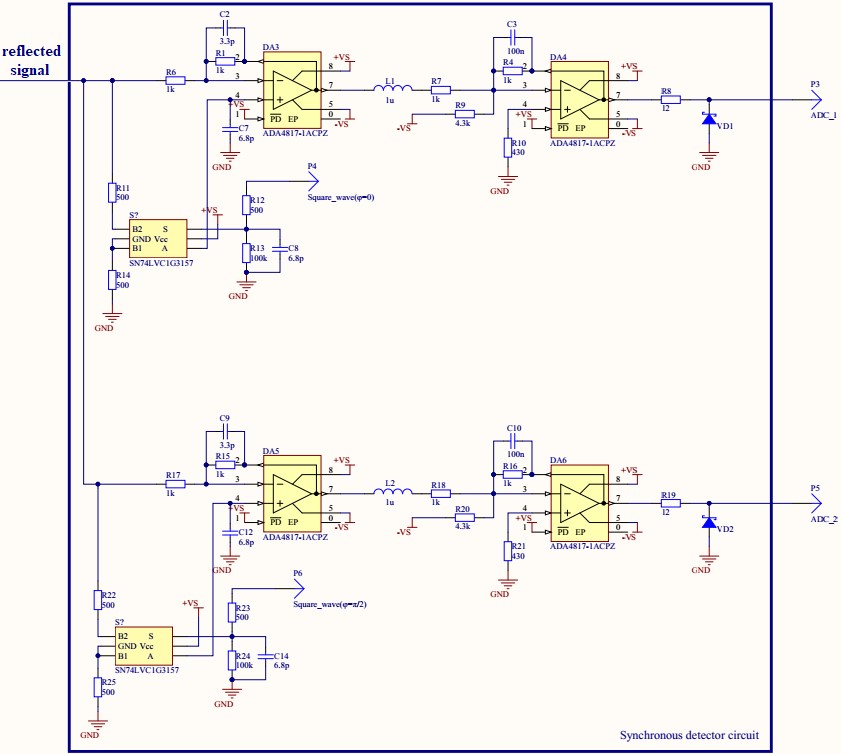

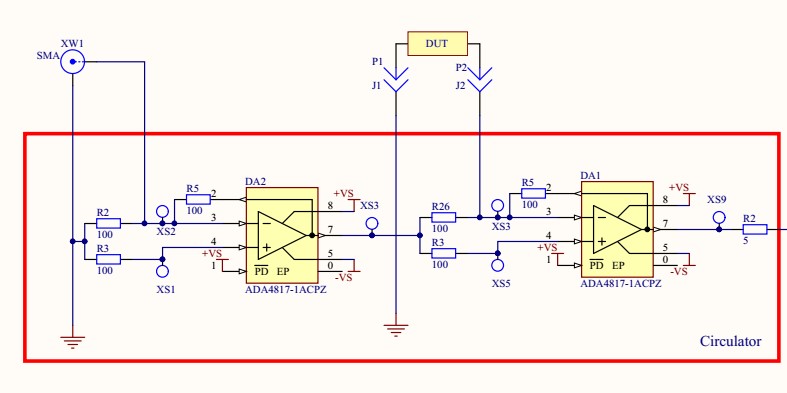

À propos du détecteur et du circulateur synchronesUn détecteur synchrone est également utilisé dans le traitement numérique du signal pour détecter divers signaux sur un fond de bruit. Zurich Instruments a une bonne description [4], dans notre cas la détection est la suivante: le signal réfléchi de fréquence connue est multiplié par le méandre à l'aide d'un interrupteur haute fréquence et d'un amplificateur opérationnel:

Le circuit de détection de réflexion

Le circuit de détection de réflexionEn fait, la multiplication est mise en œuvre comme une commutation du mode de fonctionnement de l'amplificateur opérationnel, et la commutation est contrôlée par deux méandres provenant de la carte DE10-Nano: l'un d'eux est en phase avec le signal d'origine (reçu à l'entrée de l'appareil), et l'autre avec un retard de phase de 90 degrés.

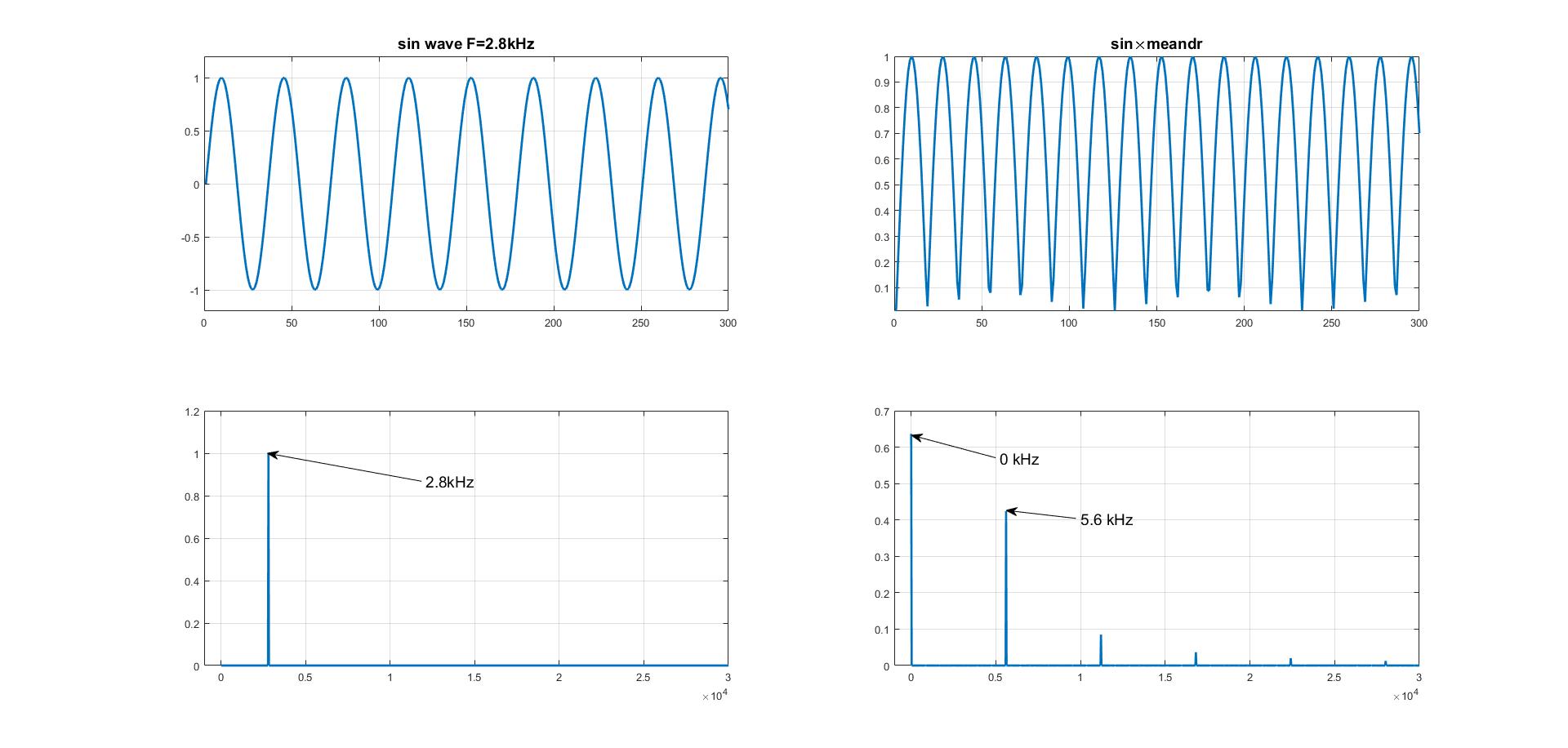

Le résultat de la multiplication est le transfert du signal utile à la composante DC, et toutes les fréquences ci-dessus ne sont plus intéressantes et peuvent donc être filtrées:

Spectre du signal avant et après multiplication: à la sortie de l'amplificateur opérationnel, vous pouvez assembler un simple filtre passe-bas pour isoler uniquement la composante continue

Spectre du signal avant et après multiplication: à la sortie de l'amplificateur opérationnel, vous pouvez assembler un simple filtre passe-bas pour isoler uniquement la composante continueUn circulateur sur amplificateurs opérationnels (amplificateurs opérationnels) est un circuit de connexion en série d'amplificateurs opérationnels fermés en anneau. Les circulateurs OA sont utilisés à de nombreuses fins, en particulier pour le réglage des antennes, des amplificateurs, des générateurs, du Gigabit Ethernet, etc. dans la gamme de fréquences jusqu'à des centaines de mégahertz. Lors de la création du VAC, un circuit de circulation créé à partir de deux amplificateurs opérationnels a été utilisé [5].

Schéma de connexion pour connecter l'appareil mesuré

Schéma de connexion pour connecter l'appareil mesuré  Concept de projet mis à jour

Concept de projet mis à jourDes signaux sinusoïdaux avec une fréquence de 1 Hz à 1 MHz avec des pas réglés à quelques Hz ont été envoyés au premier port du circulateur. Le dispositif étudié a été connecté au deuxième port, en fonction de la réponse en fréquence dont un coefficient de réflexion du signal a changé. Le signal réfléchi a été envoyé au port 3, où un circuit de détection synchrone a été assemblé pour déterminer les caractéristiques de fréquence et de phase. Pour un fonctionnement correct, les ports du circulateur ont été adaptés à une impédance de 100 Ohms, associée à la résistance de sortie du DAC et au choix des appareils à l'étude.

Il restait moins d'un mois avant la fin du projet, et à la fin du délai, il était nécessaire de préparer du matériel de rapport: une description détaillée du projet sur la page du concours, un projet publié sur GitHub dans le domaine public et un rapport vidéo sur le travail effectué.

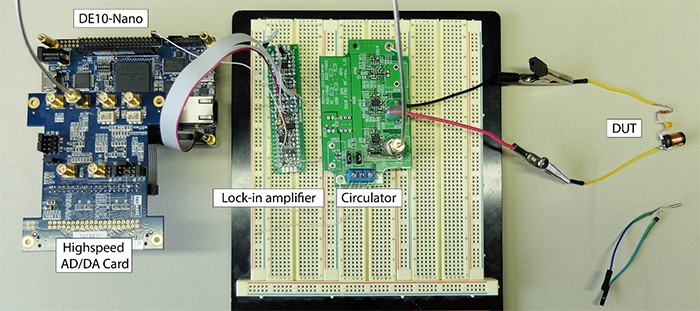

Puisque nous avons maintenant compris quelles données entreraient dans les entrées et les sorties, nous avons commencé à travailler sur un projet pour le SoC FPGA. Nous avons vu le projet implémenté comme suit: l'utilisateur définit la plage de fréquences dans laquelle la mesure est planifiée, le FPGA commence à générer des harmoniques dans un intervalle spécifié à son tour en utilisant le DAC, l'ADC reçoit les composants de quadrature et de phase à l'entrée, les convertissant en valeurs d'amplitude et de phase à la fréquence actuelle , les valeurs obtenues sont affichées en temps réel sur le moniteur connecté à la carte de débogage. Il y avait déjà des réalisations sur l'affichage des informations sur le moniteur, donc l'essentiel était le rendu correct des données en temps réel et la sortie de l'image sur HDMI. Nous sommes dissociés. Le premier groupe a repris des tâches sur le programme du processeur, pour comprendre plus en détail les initialisations nécessaires, des questions sur la visualisation des données. Nous leur avons également demandé d'augmenter la résolution de l'écran à 1024x768 [6]. Le deuxième groupe a laissé des détails sur la mise en œuvre de la partie sur le FPGA, qui devrait ensuite être fournie au processeur via le bus d'interface light_h2f, ainsi qu'un test de l'opérabilité du premier prototype de détecteur synchrone. Après avoir éliminé les lacunes et mesuré avec succès les caractéristiques de plusieurs éléments, il ne restait plus beaucoup de temps.Les deux jours suivants ont donc été consacrés à la connexion des systèmes, à l'ajout de rapports et au montage de la vidéo.

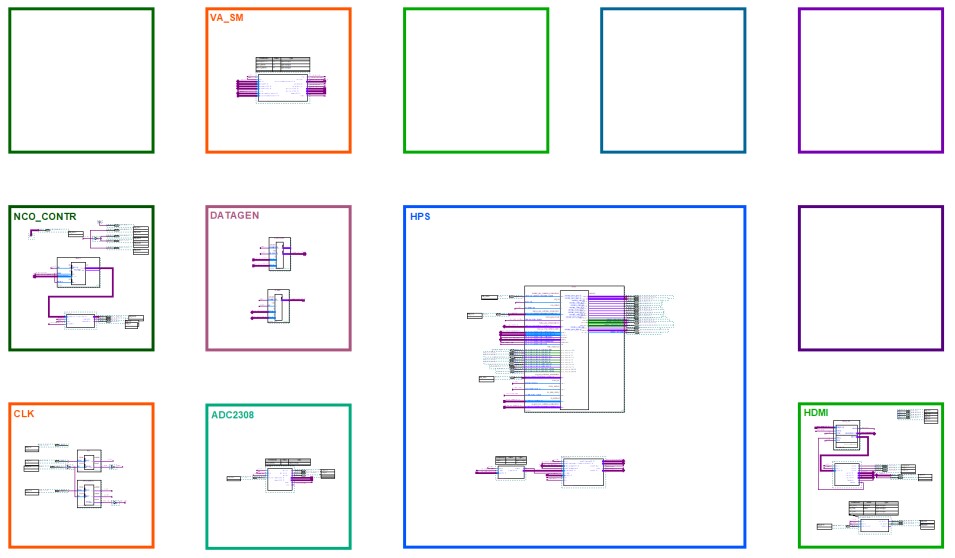

Apparence du fichier de niveau supérieur dans Quartus II

Apparence du fichier de niveau supérieur dans Quartus IIDernières minutes

Après avoir passé plus de quelques jours de repos dans le laboratoire, nous avons assemblé l'ensemble du système. Il ne fonctionnait pas pour toute la plage de fréquences potentielles, ne mesurait que le paramètre S11 et reflétait les caractéristiques de phase et d'amplitude mesurées de l'appareil connecté sur le moniteur. L'appareil assemblé à l'extérieur n'avait toujours pas l'air trop attrayant - trois cartes séparées connectées par des fils monoconducteurs, mais c'est un prototype qui

fonctionne , et vous pouvez mettre un marafet à l'étape suivante. Nous avons écrit le texte, illustré les étapes de mise en œuvre, tourné une vidéo, le tout téléchargé sur le site et avons commencé à attendre.

Bien sûr, nous avons envoyé à des amis des liens vers ces documents pour ajouter légèrement des vues. Cependant, en un jour, les opinions ont commencé à grandir, comme si quelqu'un avait fusionné cela en promotion. Après une petite analyse, il s'est avéré: notre projet a été remarqué sur hackaday.io [7] et la grande majorité des vues étaient de là. C'était intéressant de voir les premières réponses à notre projet. Inspirés, nous avons commencé à attendre les résultats.

Cependant

Ce n'est pas la première année de notre participation au concours. Ce projet a été pour nous le plus réfléchi parmi les travaux étudiants déjà mis en œuvre. Mais ça n'a pas grandi ensemble: on n'est pas passé à l'étape suivante. Cela est peut-être dû à un malentendu entre nous et les juges. Peut-être que le projet n'entre tout simplement pas dans le domaine des tendances actuelles pour les FPGA (cryptographie, calcul parallèle, réseaux de neurones, etc.). Mais pour nous, c'est une grande étape dans le développement sur SoC FPGA, une nouvelle branche de développement et, surtout, d'expérience.

Ps

Félicitations aux représentants russes qui ont pris la deuxième place en finale du concours!

Je remercie mes collègues du projet Danila Nikiforovsky et

Yevgeny Vostrikov ainsi que les dirigeants

Ivan Deineku ,

Philipp Shuklin et Artem Aleinik pour leur participation active et leur soutien.

Les références

[1] Concours Innovate Europe 2015

www.innovateeurope.org/eu/2015winner.html[2] Un guide de l'ingénieur pour les tests automatisés de l'interface haute vitesse, Jose Moreira, Hubert Wekmann, 2010, Annexe F p. 503

[3] Le spectre de la séquence périodique d'impulsions rectangulaires,

en.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html[4] Principes de détection de verrouillage et état de l'art, Zurich Instruments

www.zhinst.com/applications/principles-of-lock-in-detection[5] Circulateur / isolateur basse fréquence sans ferrite ni aimant

www.cqham.ru/oth9.htm[6] Projet VAC pour la carte DE10-Nano

github.com/tvShushtov/em078_vector_analyzer[7] Article sur le VAC sur Hackaday

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga