Intel a développé la puce 8087 en 1980 afin d'améliorer les performances des PC équipés de processeurs de ligne 8086/8088 (comme le PC IBM) lors de l'exécution d'opérations en virgule flottante. Les premiers microprocesseurs étant conçus pour effectuer des opérations avec des nombres entiers, l'exécution des opérations avec des nombres à virgule flottante était lente, c'est-à-dire sur les performances des opérations transcendantales, telles que les fonctions trigonométriques ou les logarithmes. Le coprocesseur 8087 a considérablement augmenté la vitesse d'exécution des tâches en virgule flottante; tout a été fait presque 100 fois plus rapidement. L'architecture 8087 a également été implémentée dans les processeurs Intel ultérieurs, et les instructions 8087 sont toujours utilisées dans les PC x86 modernes. Intel a introduit la puce 8087 en 1980, conçue pour améliorer les performances de l'informatique à virgule flottante sur les processeurs 8086 et 8088.

Parce que les premiers microprocesseurs ne fonctionnaient qu'avec des entiers, l'arithmétique à virgule flottante était lente et les opérations transcendantales comme les déclencheurs ou les logarithmes semblaient encore pires. L'ajout du coprocesseur mathématique 8087 au système nous a permis d'accélérer 100 fois les opérations en virgule flottante. L'architecture 8087 est devenue partie intégrante des processeurs Intel ultérieurs, et les instructions 8087 (bien que dépassées) font toujours partie des ordinateurs de bureau x86 modernes.

La puce 8087 fournit une arithmétique à virgule flottante rapide pour le PC IBM d'origine et fait partie de l'architecture x86 utilisée aujourd'hui. L'une des caractéristiques inhabituelles du 8087 est une ROM à plusieurs niveaux (mémoire morte), capable de stocker deux bits par transistor, ce qui représente le double de la densité d'une ROM conventionnelle. Au lieu de stocker des données binaires, chaque cellule de la ROM 8087 a enregistré l'une des quatre valeurs différentes, qui ont ensuite été décodées en deux bits. Le 8087 nécessitant une grande quantité de ROM pour le microcode (1) et le nombre de transistors sur la puce étant très limité, Intel a utilisé une technologie inhabituelle pour résoudre le problème. Dans cet article, je vais expliquer comment Intel a implémenté cette ROM en couches.

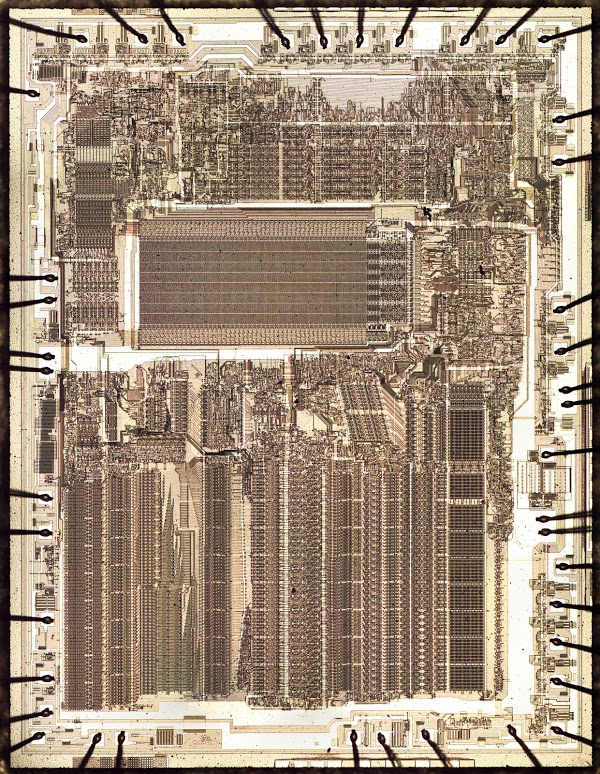

J'ai ouvert la puce 8087 et l'ai photographiée au microscope, obtenant la photo ci-dessous. Sur la photo, j'ai indiqué les principaux blocs fonctionnels basés sur ma propre ingénierie inverse (Cliquez pour agrandir l'image). La matrice du processeur 8087 est assez complexe, avec 40 000 transistors (2). Le 8087 utilise des nombres à virgule flottante de 80 bits: 64 bits sont réservés à la mantisse, 15 bits à l'exposant et un autre bit signé. (Exemple d'un nombre avec une base de 10: parmi 6,02 × 1023, 6,02 est la mantisse et 23 est l'exposant). Au bas de la photographie, le mot "traitement de fraction" marque une partie du schéma de la mantisse. De gauche à droite, cela inclut: stockage constant, décalage 64 bits, additionneur / soustracteur 64 bits et pile de registres. Un peu plus haut est le schéma de traitement de l'exposant.

Puce de coprocesseur mathématique pour les opérations à virgule flottante Intel 8087, avec la désignation des principaux blocs fonctionnelsL'exécution de l'instruction sur 8087 a nécessité plusieurs étapes, et dans certains cas plus de 1000. Le micrologiciel 8087 a utilisé le microcode pour déterminer les opérations de bas niveau à chaque étape: décalages, incrément, échantillons de mémoire, constantes de lecture, etc. Vous pouvez percevoir le microcode comme un programme simple, écrite sous forme de microcommandes, dans laquelle chaque microcommande génère des signaux de commande pour différents composants de la puce. La photo ci-dessus montre une ROM avec le programme de microcode 8087. La ROM occupe une grande partie de la puce, montrant clairement pourquoi une ROM compacte à plusieurs niveaux était nécessaire. À gauche de la ROM se trouve le "moteur" sur lequel le programme de microcode a été lancé, en fait, un simple processeur.

Le 8087 fonctionnait en coprocesseur avec le processeur 8086. Lorsque le 8086 détectait une instruction spéciale à virgule flottante, le processeur l'ignorait et permettait au 8087 d'exécuter l'instruction en parallèle. Je ne vais pas expliquer en détail le fonctionnement interne de 8087, mais, en bref, les opérations en virgule flottante ont été implémentées à l'aide d'opérations d'addition / soustraction et de décalage d'entiers. Pour ajouter ou soustraire deux nombres à virgule flottante, 8087 a effectué un décalage bit à bit du nombre jusqu'à ce que les délimiteurs binaires (c'est-à-dire que le séparateur décimal soit une virgule, mais dans le système binaire) soient égaux, puis ont ajouté ou soustrait la mantisse. La multiplication, la division et la racine carrée ont été effectuées par des décalages, des ajouts ou des soustractions répétés. Les opérations transcendantales (bronzage, arctan, log, puissance) ont utilisé des algorithmes CORDIC, qui utilisent des décalages et l'ajout de constantes spéciales, traitant un bit à la fois. 8087 a également rencontré de nombreux cas particuliers: infini, débordement, NaN (pas un nombre), nombres dénormalisés et plusieurs modes d'arrondi. Le microcode stocké dans la ROM contrôlait toutes ces opérations.

Implémentation de la ROM

La puce 8087 est constituée d'une minuscule matrice de silicium sur laquelle du silicium est dopé avec des impuretés par endroits pour obtenir les propriétés semi-conductrices souhaitées. Du polysilicium (un type spécial de silicium) est appliqué à la surface du silicium, qui forme des fils et des transistors. Et enfin, une couche métallique sur le dessus du silicone complète le circuit électrique de travail. Sur la photo ci-dessous, sur le côté gauche, une petite partie de la puce est représentée, car elle est visible sous le microscope, montrant un câblage métallique jaunâtre. Sur le côté droit de la photo, le métal a été enlevé avec de l'acide, exposant le polysilicium et le silicium. Lorsque le polysilicium traverse le silicium, un transistor est formé. Les zones roses sont en silicium dopé et les fines lignes verticales en polysilicium. Les petits cercles sont les contacts entre les couches de silicium et de métal, les reliant entre eux.

Structure de la ROM dans Intel 8087 FPU. La couche métallique est représentée à gauche, et le polysilicium et le silicium à droite.Bien qu'il existe de nombreuses façons de créer des ROM, la méthode standard consiste à créer une grille de "cellules" où chaque cellule stocke un bit. Chaque cellule peut avoir un transistor (ce qui signifie 0 bits) ou ne pas avoir de transistor, ce qui signifie 1 bit. Dans l'image ci-dessus, vous pouvez voir une grille de cellules avec des transistors (où le polysilicium est appliqué au silicium) et des transistors manquants (où il y a des lacunes dans le silicium). Pour lire les informations de la ROM, une ligne de sélection de colonne est activée (en fonction de l'adresse) pour sélectionner les bits stockés dans cette colonne et obtenir un bit de chaque ligne en sortie. Vous pouvez voir les lignes de sélection de colonne verticales (lignes de sélection de colonne) de silicium polycristallin et les lignes métalliques horizontales sur la photo ci-dessus. Les lignes verticales de silicium dopé sont mises à la terre.

Le schéma ci-dessous (correspondant au segment ROM 4x4) explique le fonctionnement de la ROM. Chaque cellule possède soit un transistor (noir), soit aucun transistor (grisé). Lorsqu'une tension est appliquée à la ligne de sélection de la colonne de silicium polycristallin, les transistors de cette colonne se mettent sous tension et relient les lignes métalliques correspondantes. (dans ce cas, le transistor NMOS est comme une grille ouverte si l'entrée est 0 et fermée si l'entrée est 1.) Les «rangées» métalliques du circuit émettent les données stockées dans la «colonne» sélectionnée.

Segment ROM 4x4 du schémaLes signaux de sélection de colonne sont générés par un circuit décodeur. Étant donné que ce circuit est construit à partir de vannes NOR, je vais d'abord expliquer la conception des vannes. Le diagramme ci-dessous montre une porte NOR à quatre entrées constituée de quatre transistors et d'une résistance de rappel (bien qu'en fait, un transistor spécial remplisse la fonction de la résistance). Sur le côté gauche du circuit, toutes les entrées sont à 0, donc tous les transistors sont bloqués, et la résistance de rappel maintient le signal de sortie à un niveau "élevé". Sur le côté droit, 1 a été appliqué à l'une des entrées, en activant le transistor. Le transistor est mis à la terre, donc le signal de sortie est maintenant de niveau "bas". Ainsi, si des entrées sont élevées (1), la sortie est faible (0). Ce circuit implémente donc la valve NOR.

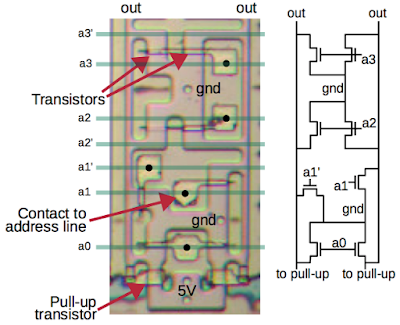

Porte NOR à 4 voies construite à partir de transistors NMOSLe circuit décodeur de sélection de colonne reçoit les bits d'adresse entrants et active la ligne de sélection correspondante. Le décodeur contient une porte NOR à 8 entrées pour chaque colonne, c'est-à-dire une porte NOR pour chaque adresse. La photo montre deux éléments NOR qui génèrent des signaux de sélection de colonne (pour simplifier, je ne montrerai que quatre des 8 entrées). Chaque colonne utilise une combinaison différente de lignes d'adresse et de lignes d'adresse remplies en entrée, en choisissant une adresse différente. Les lignes d'adresse sont dans une couche métallique, qui est supprimée sur la photo ci-dessous; les lignes d'adresse sont surlignées en vert. Pour déterminer l'adresse associée à la colonne, regardez les broches carrées associées à chaque transistor et notez quelles lignes d'adresse sont connectées. Si toutes les lignes d'adresse connectées aux transistors d'une colonne sont à un niveau bas (0), la porte NOR sélectionnera cette colonne.

La photo ci-dessous montre une petite partie du décodeur ROM avec les 8 entrées pour les portes NOR. Vous pouvez lire des adresses binaires en examinant attentivement les connexions dans la barre d'adresse. Notez le modèle binaire: a1 joint les valeurs de changement dans chaque colonne, a2 joint alternent toutes les deux colonnes, a3 joint toutes les quatre colonnes, etc. A0 est fixe car ce circuit décodeur sélectionne les colonnes impaires; un circuit ROM similaire sélectionne des adresses paires (une telle séparation était nécessaire pour que le décodeur s'adapte sur la puce, car chaque colonne du décodeur est deux fois plus large que la cellule ROM).

Partie du décodeur d'adresse pour le microcode ROM 8087. Le décodeur convertit l'adresse 8 bits en signaux de sélection de colonneLe dernier composant de la ROM est un ensemble de multiplexeurs qui réduit 64 lignes de sortie à 8 lignes. Chaque multiplexeur 8 à 1 sélectionne l'une de ses 8 entrées en fonction de l'adresse. Le schéma ci-dessous montre l'un des multiplexeurs de ligne de processeur 8087, composé de huit grands transistors pass-through, chacun étant connecté à l'une des lignes «ligne». Tous les transistors sont connectés à la sortie, donc lorsque le transistor sélectionné est activé, il transfère son entrée à la sortie. Les transistors multiplexeurs sont beaucoup, beaucoup plus grands que les transistors de la ROM pour réduire la distorsion du signal de la ROM. Un décodeur (similaire à celui considéré précédemment, mais plus petit) génère huit lignes de commande de multiplexeur à partir de trois lignes d'adresse.

L'un des multiplexeurs à 8 rangées en ROM. Ici, vous pouvez voir des couches de (poly) silicium, avec des composés métalliques peints en orangePour résumer, la ROM stocke des bits dans une grille. Il utilise huit bits d'adresse pour sélectionner une colonne dans la grille. Ensuite, trois bits de l'adresse sélectionnent les huit sorties souhaitées dans les «lignes».

ROM en couches

Jusqu'à présent, j'ai expliqué un périphérique ROM typique qui stocke un bit par cellule. Alors, comment le 8087 a-t-il pu stocker deux bits par cellule? Si vous regardez attentivement, le microcode ROM 8087 contient quatre tailles différentes de transistors - si vous considérez l'absence de transistor comme l'une des tailles (6). Avec quatre options pour chaque transistor, une cellule peut coder deux bits, doublant grossièrement la densité (7). La section actuelle explique comment les quatre tailles de transistors génèrent quatre courants différents et comment les circuits analogiques et numériques de la puce convertissent ces courants en deux bits.

Une micrographie du microcode ROM 8087 montre quatre tailles différentes de transistors. Cela permet à la ROM de stocker deux bits par cellule.La taille du transistor contrôle le courant à travers le transistor (8). Un facteur géométrique important est les différentes largeurs de silicium (rose), où il intersecte avec le polysilicium (lignes verticales), créant des transistors avec différentes largeurs de grille. Puisque la largeur de grille contrôle le courant à travers le transistor, les quatre tailles du transistor génèrent quatre courants différents: le plus grand transistor passe la majeure partie du courant et aucun courant ne circule du tout s'il n'y a pas de transistor.

Le courant ROM est converti en bits en quelques étapes. Tout d'abord, une résistance de rappel convertit le courant en tension. Ensuite, trois comparateurs comparent la tension avec la tension de référence pour générer des signaux numériques, déterminant quelle tension est supérieure / inférieure. Enfin, les portes logiques convertissent les signaux de sortie du comparateur en deux bits de sortie. Ce modèle est répété huit fois, générant un total de 16 bits en sortie.

Schéma de lecture de deux bits d'une cellule ROMLe diagramme ci-dessus effectue ces étapes de conversion. En conséquence, l'un des transistors ROM est sélectionné par la ligne de sélection "colonne" et le multiplexeur (discuté précédemment) qui génère l'un des quatre courants. Ensuite, une résistance de rappel (12) convertit le courant du transistor en tension, ce qui fait que la tension dépend de la taille du transistor sélectionné. Les comparateurs comparent cette tension à trois tensions de référence et produisent 1 si la tension ROM est supérieure à la tension de référence. Les comparateurs et les tensions de référence nécessitent une conception soignée, car les tensions ROM peuvent différer de seulement 200 mV.

Les tensions de référence sont au milieu entre les valeurs de tension attendues de la ROM, ce qui permet certaines fluctuations de tension. La tension ROM "basse" est inférieure à toutes les tensions de référence, donc tous les comparateurs sortiront 0. La deuxième tension ROM est supérieure à Ref 0, donc le comparateur inférieur sort 1. À la troisième tension ROM, les deux comparateurs inférieurs sortent 1, et au maximum la tension ROM à la sortie des trois comparateurs 1. Ainsi, les trois comparateurs produisent quatre modèles de sortie différents, selon la ROM du transistor. Les éléments logiques convertissent ensuite la sortie du comparateur en deux bits de sortie (10).

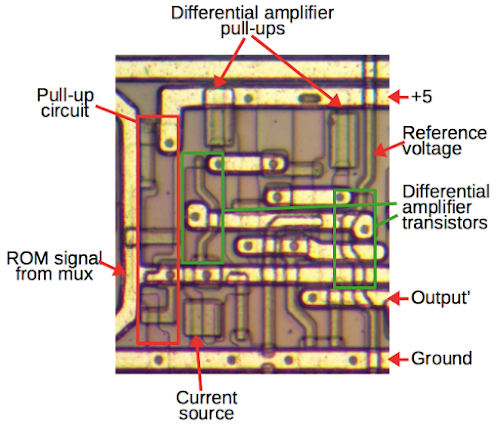

La conception du comparateur est intéressante en ce qu'elle est un pont entre les mondes analogique et numérique, produisant 1 ou 0 si la tension ROM est supérieure ou inférieure à la tension de référence. Chaque comparateur contient un amplificateur différentiel qui amplifie la différence entre la tension ROM et la tension de référence. La sortie de l'amplificateur différentiel entraîne une grille qui stabilise la sortie et la convertit en un signal de niveau logique. L'amplificateur différentiel (ci-dessous) est un circuit analogique standard. La source de courant (symbole ci-dessous) fournit du courant continu. Si l'un des transistors a une tension d'entrée plus élevée que l'autre, la majeure partie du courant passe par ce transistor. La chute de tension aux bornes des résistances entraînera une baisse de la sortie correspondante et une augmentation de l'autre sortie.

Un diagramme montrant le fonctionnement d'une paire différentielle. La majeure partie du courant passera à travers un transistor avec une tension d'entrée plus élevée, résultant en un signal de sortie plus faible. Le symbole du double cercle ci-dessous est une source de courant continu ILa photo ci-dessous montre l'un des comparateurs sur une puce; couche métallique sur le dessus, transistors en dessous. Je ne considérerai que les points principaux de ce schéma complexe; Voir la note 12 pour plus de détails. Le signal de la ROM et du multiplexeur est fourni à gauche. Un circuit de rappel 12 convertit le courant en tension. Deux grands transistors amplificateurs différentiels comparent la tension ROM avec la tension de référence (entrée par le haut). Les sorties de l'amplificateur différentiel vont au circuit d'obturation (dispersées sur la photo); la sortie de l'obturateur est dans le coin inférieur droit. La source de courant de l'amplificateur différentiel et des résistances de pull-up est constituée de transistors à mode d'appauvrissement. Trois comparateurs de sortie sont utilisés dans chaque circuit de sortie, ce qui donne un total de 24 comparateurs.

Chaque tension de référence est générée par un transistor de taille soigneusement sélectionnée et un circuit pull-up. Le circuit de référence de tension est conçu pour être aussi proche que possible du circuit de signal de la ROM, de sorte que tout changement dans la fabrication des puces affectera également les deux éléments. La tension de référence et le signal ROM utilisent le même circuit de charge. De plus, chaque circuit de tension de référence comprend un très grand transistor, identique au transistor multiplexeur, bien qu'il n'y ait pas de multiplexage dans le circuit de signal de référence - uniquement pour assurer une "adaptation" des circuits. Les trois circuits de tension de référence sont identiques à l'exception de la taille du transistor de référence (9).

Un circuit générant trois tensions de référence. Les tailles des transistors de référence sont comprises entre les tailles des transistors ROM. La couche d'oxyde n'a pas été complètement retirée de cette partie de la matrice, à cause de laquelle des tourbillons de couleur sont apparus sur la photoPour assembler l'intégralité du puzzle, la photo ci-dessous montre l'emplacement des composants du microcode ROM sur la puce (12). La partie principale du circuit ROM est constituée de transistors qui stockent des données. Le circuit décodeur de colonne est situé au-dessus et au-dessous des données ROM. La moitié des décodeurs de sélection de colonne sont en haut et la moitié en bas, pour une meilleure disposition. Le circuit de sortie est à droite. Huit multiplexeurs coupent 64 lignes de lignes à huit. Ensuite, huit lignes entrent dans les comparateurs, générant 16 bits à la sortie de la ROM vers la droite. Le circuit de référence au-dessus des comparateurs génère trois tensions de référence. En bas à droite, un petit décodeur de ligne contrôle les multiplexeurs.

ROM du micrologiciel d'Intel 8087 FPU étiquetée avec les principaux composantsBien qu'au départ, il puisse sembler qu'une ROM à plusieurs niveaux sera deux fois moins importante qu'une ROM conventionnelle, l'effet n'est pas si notable en raison du circuit supplémentaire des comparateurs et du fait que les transistors eux-mêmes sont légèrement plus grands, en raison de la nécessité d'utiliser plusieurs tailles. Malgré cela, une ROM à plusieurs niveaux a économisé environ 40% de l'espace qu'une ROM ordinaire occuperait.

Maintenant que je comprends la structure de la ROM, je peux simplement (mais fastidieusement) lire le contenu de la ROM en regardant simplement la taille de chaque transistor sous un microscope. Mais, ne connaissant pas le jeu d'instructions du microcode, le contenu de la ROM est inutile.

Conclusions

8087 « » . Intel 1981 iAPX 432.11 , 1980- . , - , , , , , , (14).

, , -. - (13). - 4 ( 16 ) , (QLC, quad-level cell). , 1980- , .

, @kenshirriff 8087. RSS-. 8087.

- 8087 1648 ( ), 16 , 26368 . , Intel .

- 8087: Intel , 40 000 , , 45 000. . , , PLA , , «» , . , .

- 8086 8087 ; . , 8087 8086 , 8087. , 8086 , . , 8087 8086 ( 8088), , 8086. , 8086, . 8087 , 8086. , 8086 8087, , . , 8087 , , . 8087 , , . 8087 8087, .

- , , , , , . , ROM, , . , 8 1/8 , 1/8 . , , (, 1 × 16) , . , «» . , Intel ; 1405 512 . , «» - 20 .

- IBM : ( , ), (link). , Xerox Alto, . , . , .

- , Hacker News , 8087 . , , .

- 1980- . Mostek : . , . Intel, ( ), . ( ) . ( ), , . Z-80 «», , , , . , , Z-80 , , , .

- . ( — .) ( , ) , . MOSFET . Wikipedia

- , -. , . , Reference 0 , . , , . : , , , . - , , , .

- : = 00, = 01, = 11, = 10. ; , , . (. «Two Bits Per Cell ROM», Stark).

- Intel iAPX 43203 (1981) , 8087. «The interface processor for the Intel VLSI 432 32 bit computer,» J. Bayliss et al., IEEE J. Solid-State Circuits, vol. SC-16, . 522-530, 1981 . 43203 - iAPX 432. Intel iAPX 432 1975 , «», Intel 1980- . iAPX 432 , Intel 8086 , 1978 . Intel 8086 , x86, iAPX 432 1986 .

- ( «Multiple-Valued ROM Output Circuits») . . (T3, T4, T5) . 4 5 , 3, ( ). ( ) T6, . ().

- - SLC ( single level cell — ), MLC (multi level cell — ), TLC (triple level cell — ) QLC (quad level cell — ). , - , , - .

- «Electronics» «Four-State Cell Doubles ROM Bit Capacity» (. 39, 9 1980 .), Intel, . Intel « » COMPCON (. 209-212, 1981 .). Intel «Multiple-valued ROM output circuits» (Proc. 14th Int. Symp. Multivalue Logic, 1984). , , — « A Survey of Multivalued Memories » («IEEE Transactions on Computers», 1986 ., . 99–106) « A review of multiple-valued memory technology » (IEEE Symposium on Multivalued Logic, 1998).

, . Aimez-vous nos articles? Vous voulez voir des matériaux plus intéressants? Soutenez-nous en passant une commande ou en le recommandant à vos amis, une

réduction de 30% pour les utilisateurs Habr sur un analogue unique de serveurs d'entrée de gamme que nous avons inventés pour vous: Toute la vérité sur VPS (KVM) E5-2650 v4 (6 cœurs) 10 Go DDR4 240 Go SSD 1 Gbps à partir de 20 $ ou comment diviser le serveur? (les options sont disponibles avec RAID1 et RAID10, jusqu'à 24 cœurs et jusqu'à 40 Go de DDR4).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps 1 ,

.

Dell R730xd 2 fois moins cher? Nous avons seulement

2 x Intel Dodeca-Core Xeon E5-2650v4 128 Go DDR4 6x480 Go SSD 1 Gbps 100 TV à partir de 249 $ aux Pays-Bas et aux États-Unis! Pour en savoir plus sur la

création d'un bâtiment d'infrastructure. classe utilisant des serveurs Dell R730xd E5-2650 v4 coûtant 9 000 euros pour un sou?