Les FPGA Stratix 10 SX / GX d'Intel

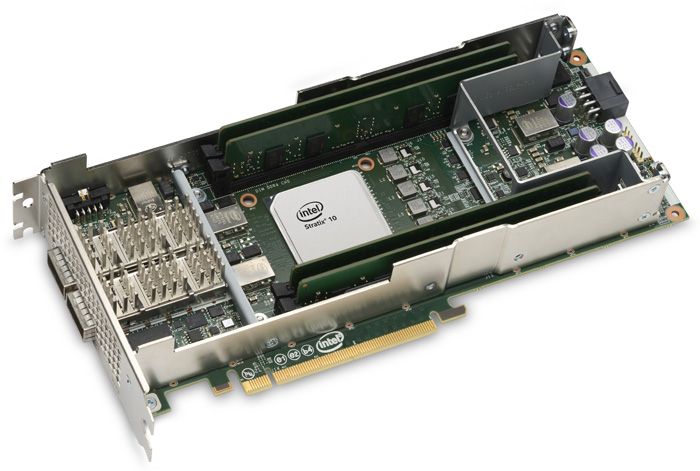

Les FPGA Stratix 10 SX / GX d'Intel , lancés il y a 2 ans, sont un nouveau mot dans le domaine des matrices de portes. Réalisées selon le minimum à l'époque, la technologie de traitement à 14 nm, elles étaient deux fois plus productives et 70% écoénergétiques que leurs prédécesseurs. Cependant, afin de réaliser toutes les capacités inhérentes à FPGA Intel, vous avez besoin du même «wrapper» avancé. La construction matérielle-logicielle publiée par Intel pour l'utilisation de Stratix dans les systèmes hôtes s'appelle la carte d'accélération programmable (PAC) - sa

prochaine version a été annoncée en septembre de cette année.

Le nouveau RAS est basé sur l'Intel Stratix 10 SX FPGA - le modèle le plus puissant de la famille Stratix 10. Je vais rappeler brièvement ses principales caractéristiques:

- Architecture HyperFlex

- technologie de production - Tri-Gate 14 nm (FinFET);

- usine monolithique avec 5,5 millions d'éléments logiques;

- jusqu'à 96 canaux émetteurs-récepteurs duplex;

- largeur de bande des émetteurs-récepteurs jusqu'à 28,3 Gb / s;

- correction d'erreur matérielle dans chaque canal de l'émetteur-récepteur;

- contrôleurs de mémoire matérielle prenant en charge la mémoire DDR4-2666;

- unités de traitement du signal numérique (DSP) avec une capacité totale de jusqu'à 10 TFLOPS, efficacité énergétique jusqu'à 80 GFLOPS / W;

- processeur ARM Cortex-A53 64 bits intégré à 4 cœurs avec une fréquence allant jusqu'à 1,5 GHz;

- accélération matérielle du chiffrement / déchiffrement AES-256, SHA-256/384 et ECDSA-256/384;

- prise en charge matérielle pour l'authentification multifacteur.

Quant à la carte d'accélération programmable elle-même, son dispositif fonctionnel est le suivant.

La même chose plus en détail sous la forme d'un tableau.

| Facteur de forme | PCIe Gen3 x16

Pleine hauteur, 3/4 longueur, double fente |

| La mémoire | 32 Go DDR4 (4x8 Go) ECC |

| Interfaces réseau | 2X QSFP + jusqu'à 100 Gbps |

| Interface de service | USB 2.0 pour le débogage et la programmation |

| Contrôleur de contrôle | Contrôleur de gestion de la carte mère Intel MAX 10 FPGA (BMC)

• Lecture des données de température et de tension

• Modèle de données au niveau de la plate-forme (PLDM)

• IPMI 2.0 |

| Gestion de l'alimentation | Intel Enpirion Power Solutions (télémétrie en temps réel et surveillance de l'état) |

| Logiciels | • Pile d'accélération pour CPU Intel Xeon avec FPGA

• Gestionnaire d'interface FPGA

• Intel Quartus Prime Pro Edition

• SDK FPGA Intel pour OpenCL |

La carte sera disponible dans le cadre des produits serveurs des partenaires OEM d'Intel (notamment Hewlett Packard Enterprise) au début de l'année prochaine.