La conception de dispositifs électroniques à l'aide de modules de mémoire DDR SDRAM rapides nécessite une attention particulière à l'intégrité du signal. L'article parle d'un outil de modélisation moderne pour résoudre de tels problèmes.Aujourd'hui, presque tous les appareils électroniques modernes sont équipés de modules de mémoire. Les serveurs, ordinateurs, smartphones, consoles de jeux, navigateurs GPS et la plupart des autres appareils sont conçus sur la base de processeurs et de FPGA. De tels appareils nécessitent une mémoire à haute vitesse avec une large bande passante de canal ou une mémoire à double fréquence (DDR). Avec chaque nouvelle génération de DDR SDRAM (mémoire dynamique synchrone avec accès aléatoire et vitesse de transfert de données doublée), la vitesse d'échange de données, la capacité et la consommation de mémoire sont réduites.

Lors de la conception des cartes de circuits imprimés d'appareils à mémoire DDR, un certain nombre de difficultés peuvent survenir, dont le problème de l'intégrité du signal. Cet article traite des problèmes de garantie de l'intégrité des signaux dans les appareils utilisant la mémoire DDR.

Bruit et gigue du signal de données numériques

Lors de la réception / transmission du signal d'horloge du bus mémoire du contrôleur au microcircuit, diverses interférences peuvent se produire en raison de la propre gigue des émetteurs et des récepteurs, des pertes dans les lignes de transmission, du bruit et des interférences. Tout cela conduit à l'apparition de gigue et de distorsion de la forme du signal d'interface numérique.

Toute énergie indésirable ajoutée à un signal idéal peut être considérée comme du bruit. Elle peut être causée par des interférences provenant de lignes voisines, un canal de transmission mal conçu, une impédance incohérente et d'autres facteurs qui entraînent un flou du front d'impulsion. En l'absence de bruit, le signal réel est identique à l'idéal.

Tout écart par rapport à la forme d'onde idéale affecte son intégrité. Les écarts de temps (gigue) et les écarts d'amplitude / tension (bruit) affectent également les performances du système. Si vous ne garantissez pas l'intégrité des signaux, le système DDR utilisera des informations erronées, ce qui augmentera considérablement l'intensité des erreurs binaires BER (Bit Error Rate). En fin de compte, le système fonctionnera de manière incorrecte et inefficace.

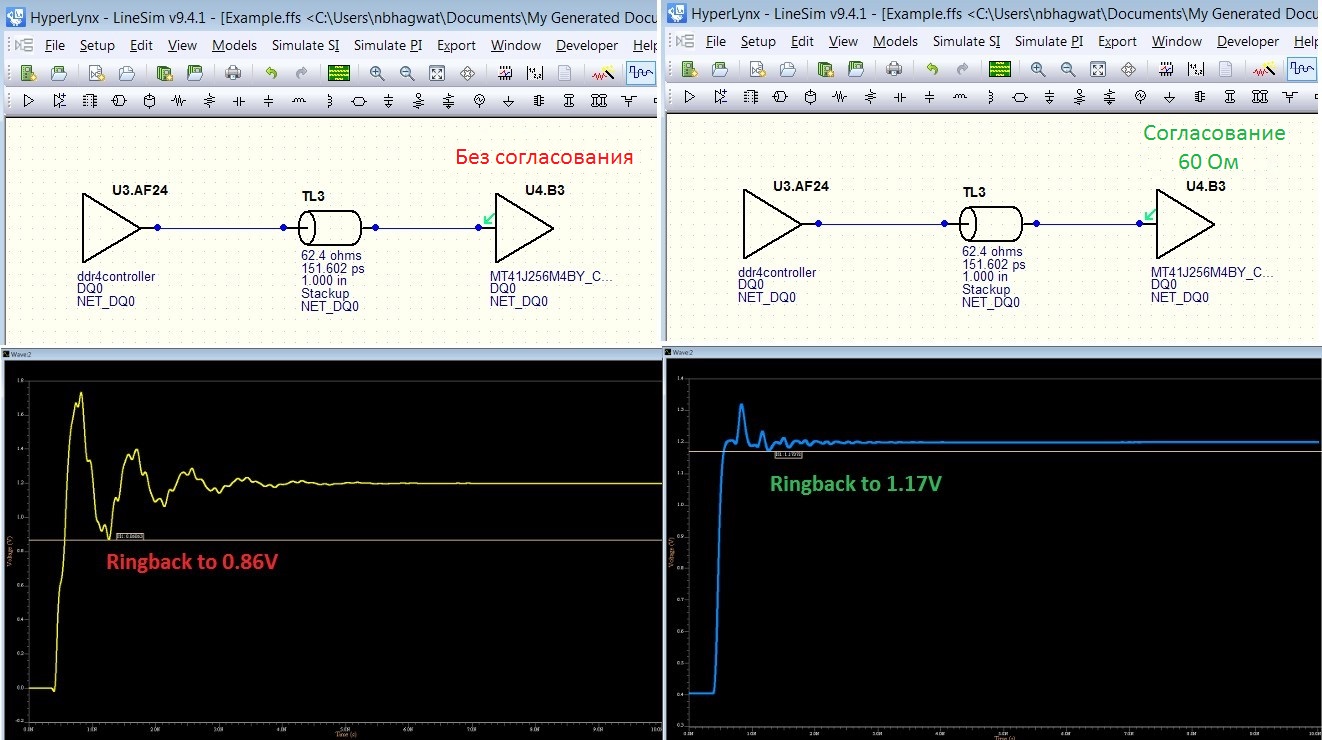

Prenons un exemple spécifique. Si l'ingénieur connecte l'émetteur à un récepteur incohérent situé à une certaine distance de celui-ci, la forme d'onde sera similaire à celle illustrée sur la figure 1a: ici, vous pouvez clairement voir la «sonnerie» à 0,86 V et les émissions parasites de boost à 1,75 V à un signal de 1,2 V. Tout cela peut entraîner un dysfonctionnement de la logique DDR4 et, si la carte de circuit imprimé est conçue avec une telle topologie, avec une probabilité de 100%, des erreurs se produiront dans le flux de données, ce qui, à son tour, peut conduire à un fonctionnement incorrect du système .

Théoriquement, il est possible de résoudre les problèmes de «sonnerie» et d'émissions en réduisant la longueur de la ligne de transmission, mais, malheureusement, cela fonctionne rarement dans la pratique. Le moyen le plus efficace consiste à faire correspondre le récepteur / émetteur par impédance, ce qui entraîne une diminution du niveau de bruit et une amélioration de la forme du signal (voir Fig. 1b).

Fig. 1. Une topologie ayant des problèmes de qualité du signal: a) avant la coordination b) après la coordination

Fig. 1. Une topologie ayant des problèmes de qualité du signal: a) avant la coordination b) après la coordinationÀ cet égard, la question se pose de savoir quelle cote d'approbation utiliser et comment la calculer, car même une petite modification de la cote peut affecter considérablement les performances du système. La seule façon de résoudre ce problème consiste à simuler, en particulier, à l'aide des assistants de réconciliation interactive utilisés dans HyperLynx.

Problèmes de synchronisation dans DDRx

Étant donné que les bus parallèles fonctionnant à des fréquences gigahertz, tels que DDR3 / 4, sont de plus en plus utilisés dans la conception des cartes de circuits imprimés, les problèmes d'intégrité du signal sont particulièrement aigus. La SDRAM DDR3, par exemple, diffère considérablement en termes de performances de vitesse et de fréquence de la DDR2: la fréquence d'horloge maximale de la DDR2 est de 800 MHz et la fréquence maximale de la DDR3 est de 1600 MHz. En raison de la réduction de la tension d'alimentation des cellules, les créateurs du nouveau type de RAM ont réussi à réduire sa consommation d'énergie jusqu'à 15%, ce qui, compte tenu des performances impressionnantes de la DDR2, peut être qualifié de véritable percée. La DDR3 utilise une topologie de bus de commande / adresse / contrôle «Fly-by» réseau avec correspondance intra-module (ODT). Dans le même temps, la DDR3 crée de nouveaux problèmes d'intégrité du signal, en particulier, associés aux circuits ODT, aux taux de transfert de données plus élevés et à la distorsion temporelle.

Malgré le fait qu'il existe des contrôleurs qui effectuent un étalonnage automatique en lecture / écriture, optimisant les intervalles de temps, le développeur doit garantir le bon timing. Les limites de temps dans les interfaces DDR3 sont si petites que l'approche empirique de l'optimisation ne suffit plus, et afin de garantir le fonctionnement de l'interface à des vitesses élevées, une analyse détaillée du circuit est nécessaire.

De telles relations temporelles complexes sont difficiles à analyser sans l'aide d'outils supplémentaires. Afin d'identifier et d'éliminer les problèmes potentiels en général ou de calculer des relations temporelles complexes, les ingénieurs doivent analyser les relations de cause à effet, ce qui est une tâche complexe et longue.

De tels problèmes de conception entraînent souvent des retards dans la planification du projet et, par conséquent, augmentent considérablement le temps nécessaire au produit fini pour entrer sur le marché. Des outils de simulation avancés et puissants peuvent aider les ingénieurs à trouver et à corriger rapidement les erreurs en optimisant les signaux à un niveau BER acceptable.

Analyse d'intégrité du signal des systèmes DDR SDRAM

Le comité de normalisation de l'ingénierie JEDEC Semiconductor a approuvé une liste d'exigences à respecter lors du développement de produits de qualité. Il est essentiel que les SDRAM DDR répondent à ces exigences pour garantir un fonctionnement correct et éviter les problèmes d'intégrité du signal. Cependant, effectuer toutes les mesures et tous les calculs nécessaires se heurte souvent à de nombreuses difficultés.

Parfois, ces calculs peuvent être complètement évités en suivant strictement les instructions de mise en page fournies par le fournisseur du contrôleur. Mais que se passe-t-il si ces recommandations ne peuvent pas être mises en œuvre en raison de diverses limitations dans des projets spécifiques? Que faire s'il faut beaucoup de temps pour s'assurer que le projet répond à toutes les recommandations et exigences? Dans de telles situations, vous devez utiliser des outils pour vérifier rapidement le projet avant de le mettre en production.

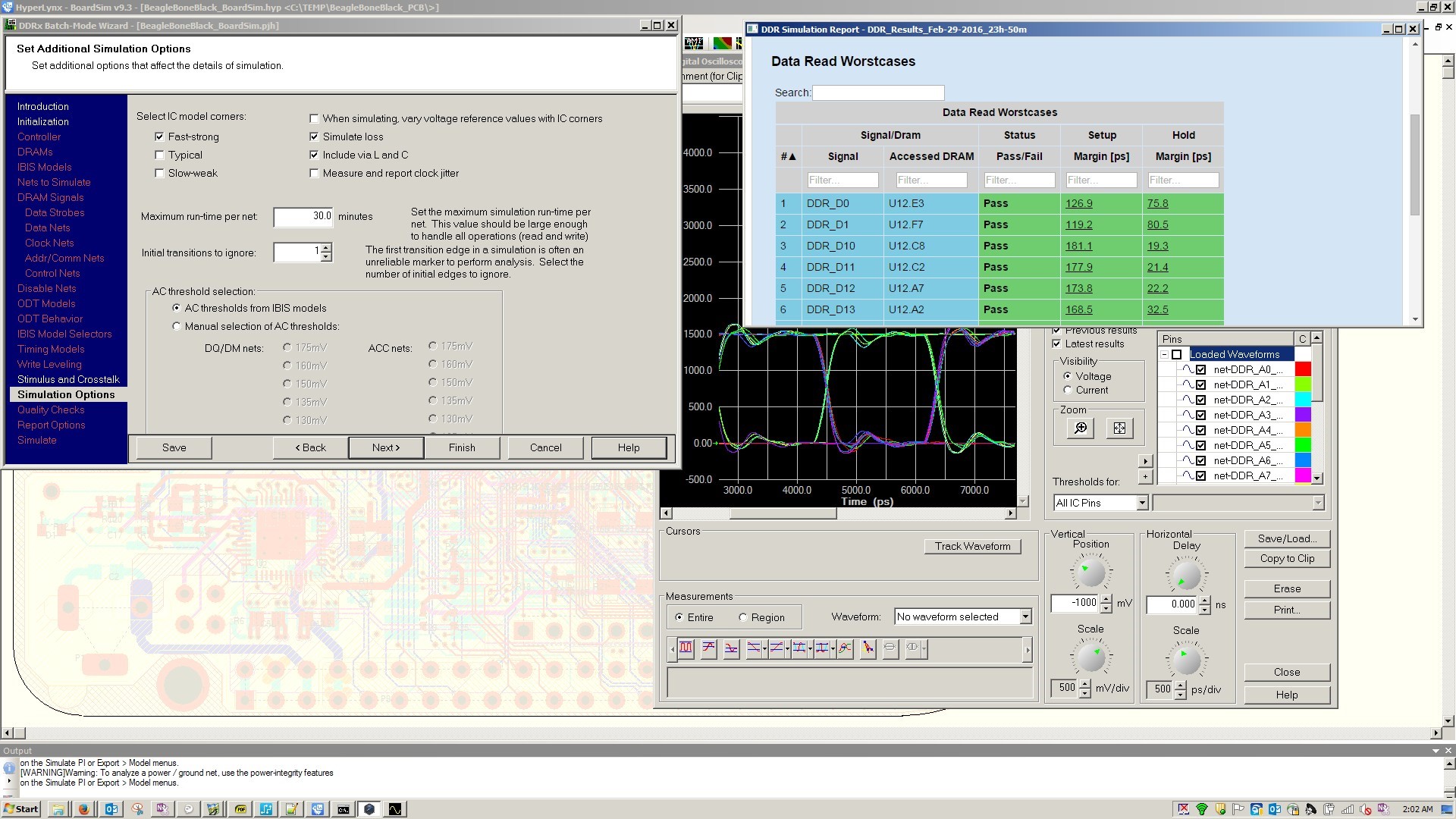

À l'aide d'HyperLynx DDR (voir figure 2), vous pouvez simuler l'intégralité du canal DDR en une seule itération. Pour ce faire, il vous suffit de lier les modèles de périphériques appropriés disponibles sur les sites Web des fabricants. Après cela, le temps de configuration de la simulation ne prendra que dix minutes, ce qui permettra de poursuivre la modélisation sans délai.

Fig. 2. Modélisation avec l'aide interactive HyperLynx DDR

Fig. 2. Modélisation avec l'aide interactive HyperLynx DDRLe processus de configuration est intuitivement simple, car tous les paramètres nécessaires à la configuration de la simulation sont demandés par l'assistant de manière interactive. L'utilisateur saisit simplement les informations pertinentes, telles que le choix des modèles IBIS pour les contrôleurs et les dispositifs de mémoire, les taux de transfert pour les cycles de lecture / écriture, ODT, etc. Toutes les configurations créées peuvent être enregistrées pour une utilisation future, ce qui réduira le temps d'installation dans les projets futurs. Les simulations peuvent être effectuées avant ou après le traçage, aidant à déterminer les exigences pour la pile de PCB.

Analyse des résultats de simulation

La simulation comprend l'analyse de l'intégrité du signal et la synchronisation de l'ensemble du bus DDR. À la fin du processus de simulation, un rapport est créé qui comprend des données sur le passage (et non la réussite) des vérifications, conformément aux informations de configuration et aux données entrées dans l'assistant interactif. Les résultats peuvent être filtrés et correctement organisés pour une étude minutieuse des problèmes de synchronisation et d'intégrité du signal dans les cycles de lecture / écriture de données, dans les bus d'adresse et de commande ou dans les circuits différentiels. Tous les résultats du rapport sont liés aux données de simulation correspondantes, pour un accès rapide à l'outil de visualisation des formes d'onde graphiques des signaux.

Les données de simulation en mode batch créées par l'assistant DDRx peuvent être enregistrées sur le disque, ce qui vous permet d'utiliser l'oscilloscope HyperLynx pour simuler plusieurs circuits simultanément et étudier en détail les problèmes d'intégrité du signal en mode hors ligne.

Conclusion

La DDR SDRAM ouvre de nouvelles possibilités dans le développement d'appareils électroniques. Comme pour les autres interfaces haut débit, l'utilisation de la mémoire DDR présente plusieurs fonctionnalités. Le problème de l'intégrité du signal doit être soigneusement étudié afin d'éviter des itérations inutiles et coûteuses dans la fabrication des produits. La modélisation est un excellent moyen de résoudre ce problème, vous permettant de prendre en compte les effets au niveau de la carte, tels que les changements d'impédance et les retards, offrant un contrôle complet sur l'interface mémoire. De puissants outils d'analyse aideront à garantir que les projets sont conformes aux recommandations JEDEC et à garantir que le produit final fonctionnera avec des performances et une fiabilité élevées.

HyperLynx DDR peut être partagé par de nombreuses sociétés de conception de PCB CAO, notamment PADS et Xpedition.

Cet article a été publié dans la revue MODERN ELECTRONICS n ° 7, 2018 (www.soel.ru)