Début octobre, Xilinx a

présenté la nouvelle puce Versal, basée sur des matrices de portes programmables (

FPGA ). La logique de fonctionnement d'un tel appareil peut être modifiée à tout moment en cours d'utilisation. Il est prévu que la puce accélérera le travail des systèmes d'IA et trouvera une application dans les réseaux 5G. La sortie du processeur est prévue pour fin 2019.

Ensuite, nous parlons de l'appareil et de la façon dont il aidera les réseaux de prochaine génération.

/ Flickr / mike mozart / cc

/ Flickr / mike mozart / ccProblème de réseau 5G

La technologie 5G utilise des fréquences élevées - 28 GHz et plus - de sorte que le signal est mal transmis sur de longues distances. Le plus de sa propagation est fortement gêné par les murs des maisons. Dans une ville, cela peut entraîner une baisse de la qualité de la connexion.

Les experts

disent que cela deviendra un obstacle au travail d'un grand nombre d'appareils IoT, dont une augmentation active est

prévue à partir de 2020 (juste au moment où des réseaux 5G à part entière seront déployés).

Les appareils connectés, tels que les voitures ou les gadgets médicaux portables, doivent communiquer en temps réel. L'instabilité de la connexion peut les empêcher d'évaluer correctement la situation qui les entoure ou de transmettre des données vitales (par exemple, sur l'état de la santé humaine) aux serveurs de l'organisation au service. Les entreprises prévoient de résoudre ce problème en organisant des systèmes d'antennes distribuées spéciales, mais cela pose des problèmes.

Par exemple, à New York, plus d'un millier de stations de base sont installées. Pour couvrir toute la ville avec un réseau 5G,

il faudra en installer un autre demi-million . Le coût du projet sera beaucoup plus élevé que dans le cas des "normes G" précédentes.

Comment Versal aide à résoudre ces problèmes

L'appareil Xilinx aidera à résoudre les problèmes de stabilité de la connexion Internet à l'aide de systèmes d'IA, avec lesquels il est «réglé» pour fonctionner. La puce Versal traitera des algorithmes d'apprentissage automatique dans des réseaux 5G qui optimisent les

diagrammes de rayonnement des antennes mobiles. Cela évitera les secteurs aveugles et choisira le mode de transmission de données approprié.

Les systèmes d'IA amélioreront également les algorithmes de

transfert , qui sont responsables du transfert des sessions d'une station à une autre. De plus, les réseaux s'auto-répareront et s'adapteront, redirigeant automatiquement les données en cas de défaillance d'un nœud. Ainsi, les utilisateurs de la 5G pourront se déplacer librement dans un bâtiment ou une ville sans échec de connexion.

Xilinx a déjà des clients pour les puces AI pour 5G. Des processeurs polyvalents seront utilisés pour le réseautage aux Jeux olympiques de 2020.

Caractéristiques de l'architecture de la puce

Xilinx a introduit le concept Versal en octobre. Le nouveau microcircuit est

hétérogène , c'est-à-dire qu'il utilise plusieurs unités de calcul à la fois. Ces unités peuvent être des processeurs, des coprocesseurs, des circuits intégrés ASIC et FPGA.

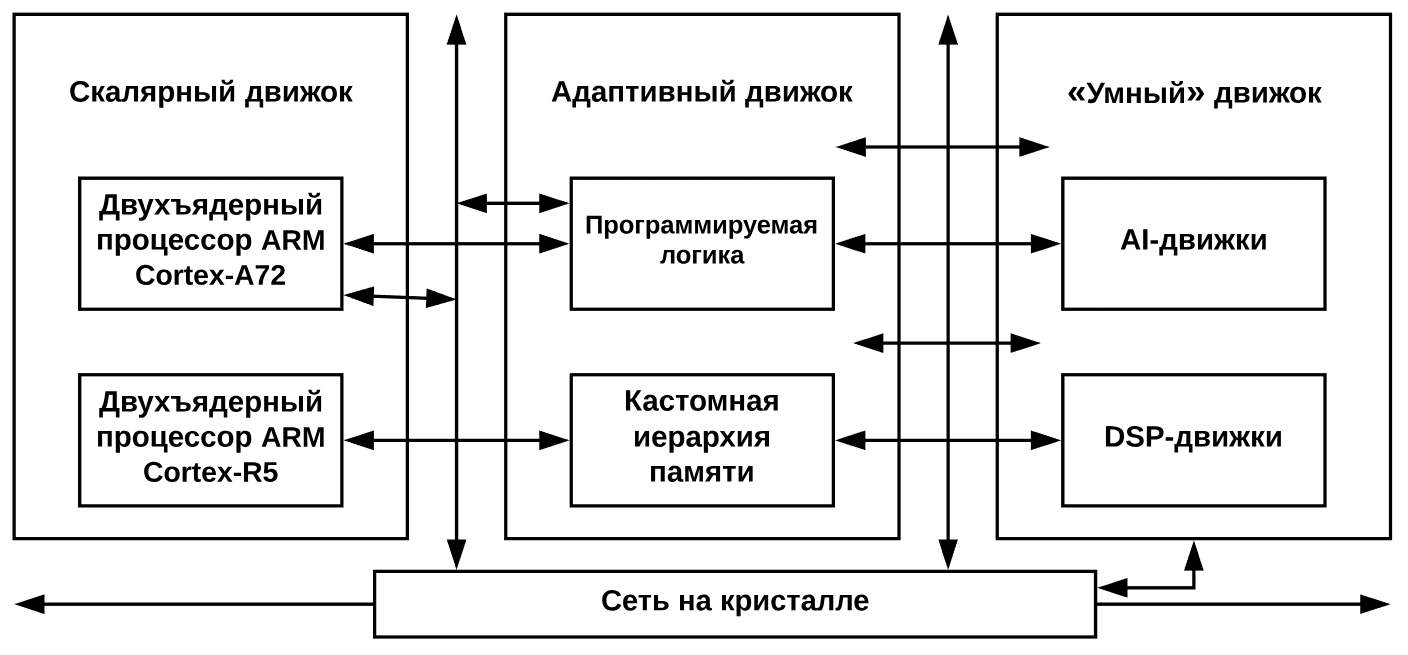

La nouvelle puce Xilinx est basée sur une version améliorée de FPGA - l'architecture Adaptive Computer Accelerator Platform (ACAP). Il se compose de quatre composants de base: un moteur

scalaire , un moteur adaptatif,

des accélérateurs

vectoriels (moteur «intelligent») et un réseau sur puce (NoC - Network-on-Chip) pour connecter les éléments du système.

Le moteur scalaire est représenté par les processeurs ARM Cortex-A72 et Cortex-R5 double cœur. La logique programmable est construite sur des

éléments logiques configurables avec

des tables de recherche , des

déclencheurs , de la mémoire et des blocs spéciaux pour relier les composants. Tout cela vous permet de construire une

hiérarchie de mémoire , affinée pour une tâche de calcul spécifique.

Le moteur «intelligent» est basé sur l'

architecture VLIW , qui est nécessaire pour l'exécution parallèle de plusieurs opérations en une seule instruction. Le principe des calculs

SIMD est également appliqué. Une telle structure permet de résoudre les problèmes de MO et de traiter les signaux 5 à 10 fois plus rapidement que les systèmes classiques. Quant à NoC, sa bande passante déclarée est de 1 Tbps.

Le diagramme d'architecture ACAP ressemble à ceci.

La famille de puces Versal sera produite à TSMC à l'aide d'une technologie de traitement à

7 nm . D'autres caractéristiques architecturales peuvent être trouvées dans les documents PDF officiels -

Vue d'ensemble de l' architecture ASAP et

Revue des puces Versal .

Le système est programmé en C, C ++ et Python. Selon les développeurs, ils ont opté pour ces PL, car selon

TIOBE , C, C ++ et Python, ils sont les plus populaires après Java.

De plus, ces langues se complètent. C et C ++ sont compilés, ce qui signifie que le code peut être exécuté sur du métal nu (en particulier, sur FPGA). Python est meilleur que quiconque pour analyser les données et travailler avec les systèmes d'IA. D'autres raisons de choisir Xilinx se trouvent dans une étude distincte sur le sujet (

PDF ).

Solutions similaires

Des puces basées sur FPGA sont également développées par d'autres sociétés, telles qu'Intel. Parmi les derniers produits de la société, le

dispositif hybride Arria se distingue. Le développement est une plate-forme de deux puces: Xeon E5-2600 v4 et

Altera Arria 10 .

Selon Intel, l'appareil convient aux serveurs, aux centres de données et aux services cloud, où la charge augmente souvent de façon spasmodique. Un processeur sur le FPGA aidera à traiter les données en parallèle, ce qui augmentera les performances globales du système. Fujitsu, par exemple,

prévoit de fournir sa gamme de serveurs Primergy avec cette puce d'ici la fin de l'année.

D'autres acteurs du marché - AMD, ARM, Qualcomm, Samsung et autres - ont créé l'organisation à but non lucratif

HSA Foundation en 2012. Les calculs hétérogènes y sont vulgarisés: ils développent les normes de l'industrie, aident les développeurs à pénétrer le marché et parrainent des programmes éducatifs.

Xilinx

estime qu'avec le développement des systèmes d'IA et la propagation des réseaux 5G, la demande de plates-formes FPGA augmentera. Le PDG de Xilinx, Victor Peng,

note que le seul obstacle à la production en série de puces est la concurrence du CPU et du GPU, qui empêche les solutions FPGA de «capturer» le marché. Mais, probablement, un bond de la demande (si cela se produit) ne devrait pas être prévu

avant 2020 .

PS Documents supplémentaires du blog d'entreprise des experts VAS:

PPS Quelques nouveaux articles de notre blog sur Habré: