Début octobre, le fabricant de puces taïwanais TSMC, qui travaille avec des sociétés telles que AMD et Apple, a

fait deux déclarations. Tout d'abord, l'entreprise a réussi à améliorer sa technologie de traitement à 7 nm et à fabriquer la puce à l'aide d'une nouvelle technologie. La seconde - une puce de 5 nanomètres sera lancée en 2019. Les perspectives de ces développements sont décrites ci-dessous.

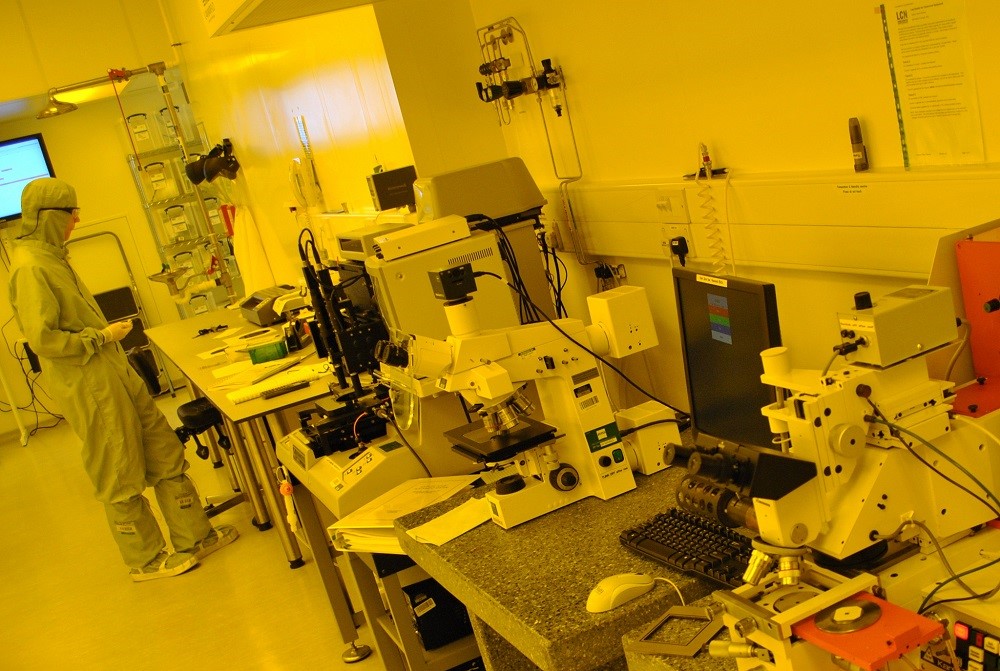

/ photo UCL CC

/ photo UCL CCTechnologie de processus TSMC 7 nm

La puce imprimée par TSMC au début du mois est basée sur la technologie de processus 7 nm de deuxième génération, qui a subi un certain nombre de changements par rapport à son prédécesseur.

La technologie de traitement à 7 nm de la TSMC de première génération est basée sur la lithographie

DUV avec un rayonnement ultraviolet "profond". Dans ce cas

, la lithographie par immersion et les scanners avec une longueur d'onde de 193 nm sont utilisés. La première puce de cette technologie dans l'entreprise a été imprimée en avril de cette année. Et en mai, TSMC a

commencé à produire des puces 7 nm pour Apple. De nouvelles puces ont été

fournies avec le système de puces A12 Bionic. Elle est déjà responsable du travail des derniers smartphones du géant informatique: iPhone XR, XS et XS Max.

Au total, les commandes

proviennent de deux douzaines d'entreprises, dont Bitmain, NVIDIA et Qualcomm. AMD est

également un client majeur des processeurs TSMC - Vega 20 et un processeur serveur Epyc sont construits sur la base de la technologie de processus 7 nm.

Plus tôt ce mois-ci, TSMC a indiqué avoir été en mesure d'améliorer sa technologie de traitement 7 nm. Les ingénieurs ont utilisé la photolithographie dans l'ultraviolet "dur" (

EUV ) pour développer des puces. Dans ce cas, la longueur d'onde est

vingt fois inférieure et est de 13,5 nm . Le passage à l'EUV (associé au développement de méthodes de modélisation et de détection des défauts et autres processus) a permis de

réduire la consommation électrique des microcircuits fabriqués de 8% et d'augmenter la densité des transistors de 20%, par rapport à la technologie de la première génération.

Jusqu'à présent, seulement quatre couches non critiques de la puce sont mises en œuvre avec EUV. Tout d'abord, l'entreprise souhaite maîtriser la technologie, puis l'utiliser pour la fabrication de gros volumes de produits (alors que la production d'appareils adaptés est assez faible).

Le fabricant n'a pas révélé qui est devenu le premier client à recevoir les nouvelles puces, mais il est supposé

qu'Apple était le même . La société développe également une version spécialisée de la technologie de processus mise à jour pour l'industrie automobile.

Quand attendre une puce de 5 nm

TSMC prévoit de commencer la production risquée de puces de 5 nm dès 2019. Pour créer des microcircuits de 5 nanomètres, la société utilise EUV, mais en utilisant cette méthode de photolithographie, quatorze couches de la puce seront produites, au lieu de quatre.

D'ici là, une entreprise taïwanaise prévoit de mettre un terme à la technologie EUV et d'augmenter la capacité de production. L'entreprise a déjà

annoncé le début de la construction d'une nouvelle usine où des puces seront créées. Il sera érigé dans le parc scientifique sud de Taiwan.

Les puces de 5 nm présentent plusieurs avantages par rapport à 7 nm. Avec la même complexité, la densité des transistors dans les puces mises à jour

sera 1,8 fois plus élevée et la fréquence d'horloge augmentera de 15%. Dans ce cas, le processeur 5 nm consommera 20% moins d'énergie que le 7 nm. Cependant, avant de commencer la production, l'entreprise doit résoudre un certain nombre de difficultés.

Le premier d'entre eux est le

manque d' outils

de développement. Le package de conception EDA nécessaire pour la technologie du procédé 5 nm sera préparé en novembre de cette année. Cependant, les bibliothèques pour les unités PCIe 4.0 et USB 3.1 ne seront prêtes que l'été prochain.

Un autre problème est le coût de développement élevé. Selon les experts, le développement d'un système sur puce utilisant la technologie 7 nm

coûte environ 150 millions de dollars. Dans le cas de la technologie de traitement à 5 nm, le coût s'élève à 250 millions de dollars. Cela signifie que le prix des produits finis augmentera à terme et que moins d'entreprises clientes seront intéressées à utiliser ces puces. Par conséquent, rien ne garantit que la production de microcircuits utilisant la technologie de traitement à 5 nm sera payante.

Comment vont les autres entreprises?

Dans l'un de nos précédents articles, nous avons déclaré que le fabricant de circuits intégrés

GlobalFoundries avait arrêté le développement de sa technologie de traitement à 7, 5 et 3 nm en raison de difficultés financières. Au lieu de cela, l'organisation est passée à l'amélioration du 14 nm et à la création de périphériques de stockage intégrés.

/ photo plaquette de silicium Mr Seb CC / 22nm Intel

/ photo plaquette de silicium Mr Seb CC / 22nm IntelIntel perd également TSMC dans la vitesse de développement de nouveaux processus de fabrication. La société a de nouveau

reporté la sortie de la puce 10 nm et a annoncé en septembre qu'elle

reviendrait sur la puce

22 nm (mais pour la mise en place de chipsets) afin de «décharger» les capacités de production. Cependant, il est juste de dire que le 7 nm en TSMC et le 10 nm en Intel

sont considérés comme les mêmes normes de conception dans le contexte de la densité et de la taille des transistors.

Jusqu'à présent, Samsung

est le seul concurrent de TSMC dans le domaine des 7 et 5 nanomètres. Le géant sud-coréen a prévu le lancement de puces 7 nm pour le premier semestre de l'année prochaine. Les puces conformes aux normes de conception du Samsung 5 nm commenceront également à produire en 2019, mais lorsque leurs ventes commenceront, cela reste inconnu.

PS À propos de l'infrastructure virtuelle et de travailler avec PD - dans notre

canal Telegram :