Il n'y a pas si longtemps, STM a lancé la très puissante gamme de cristaux STM32H7 selon les normes des microcontrôleurs. Ce qui m'a attiré chez elle:

- fréquence de coeur augmentée jusqu'à 400 MHz

- RAM augmentée, jusqu'à 1 Mo

- ADC 16 bits

- compatibilité broche à broche avec la série F7

Je pensais parfaitement, j'ai soudé le cristal STM32H743IIT6 sur la carte au lieu du STM32F746IGT6 et commencé un nouveau projet dans SW4STM32.

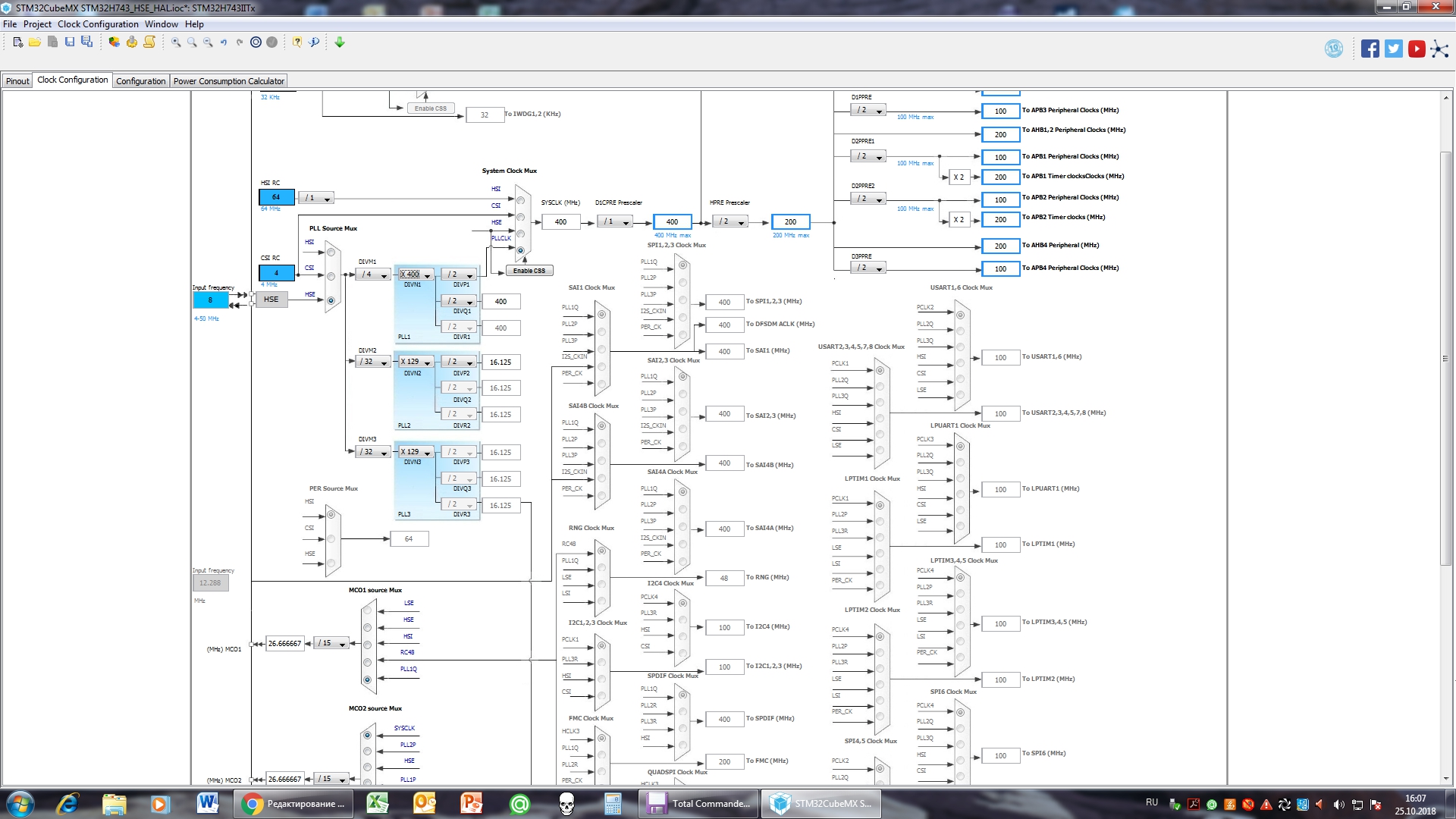

Il est pratique d'utiliser l'onglet Configuration de l'horloge du programme STM32CubeMX pour calculer les coefficients des diviseurs et les facteurs du système d'horloge du microcontrôleur.

Paramètres d'horloge:

- quartz externe - 8 MHz

- source de fréquence pour PLL1 - quartz externe (HSE)

- diviseur pour PLL1 - 4 (DIVM1)

- multiplicateur PLL1 - 400 (DIVN1)

- diviseurs de sortie - 2 (DIVP1, DIVQ1, DIVR1)

En conséquence, la fréquence centrale (SYSCLK) est de 400 MHz.

En plus du STM32CubeMX, il existe également le package de micrologiciel STM32CubeH7, qui contient un grand nombre d'exemples d'utilisation de périphériques pour le STM32H7. C'est de lui que la séquence d'initialisation du système d'horloge du microcontrôleur a été prise.

Les informations et commentaires proviennent des sources suivantes:

- SystemClock_Config du package de micrologiciel STM32CubeH7

- Manuel de référence MCU 32 bits avancés basés sur ARM STM32H743 / 753 et STM32H750

- - Fiche technique STM32H743xI

Commençons donc.

1. Allumer le quartz externe et attendre d'être prêt.

// Enable HSE RCC->CR |= RCC_CR_HSEON; // Wait till HSE is ready while((RCC->CR & RCC_CR_HSERDY) == 0);

2. Indication de la source de fréquence pour PLL1 - quartz externe.

3. La valeur du diviseur est définie sur 4.

//PLLM = 4 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_5; //0 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_4; //0 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_3; //0 RCC -> PLLCKSELR |= RCC_PLLCKSELR_DIVM1_2; //1 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_1; //0 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_0; //0

4. Le facteur N et les diviseurs P, Q, R

//PLL1DIVR bits //DIVN1[8:0] 0 - 8 PLLN = 400 //DIVP1[6:0] 9 - 15 PLLP = 2 //DIVQ1[6:0] 16 - 22 PLLQ = 2 //DIVR1[6:0] 24 - 30 PLLR = 2 RCC -> PLL1DIVR |= 0x0101038F;

5. Diviseur de fréquence fractionnaire PLL (si nécessaire)

// /* Configure PLL PLL1FRACN */ //__HAL_RCC_PLLFRACN_CONFIG(RCC_OscInitStruct->PLL.PLLFRACN)

6. Indication de la plage de fréquences d'entrée PLL1

7. Indication de la plage de fréquence de sortie PLL1

8. Mise en marche des diviseurs de sortie PLL1: P, Q, R

/* Enable PLL System Clock output. */ // __HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL1_DIVP); //Bit 16 DIVP1EN: PLL1 DIVP divider output enable RCC->PLLCFGR |= RCC_PLLCFGR_DIVP1EN; /* Enable PLL1Q Clock output. */ //__HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL1_DIVQ); RCC->PLLCFGR |= RCC_PLLCFGR_DIVQ1EN; /* Enable PLL1R Clock output. */ // __HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL1_DIVR); RCC->PLLCFGR |= RCC_PLLCFGR_DIVR1EN;

9. L'inclusion du diviseur fractionnaire.

10. Démarrez PLL1 et attendez la disponibilité

PLL1 est configuré et fonctionne. Sélectionnez maintenant la source de fréquence SYSCLK et configurez les diviseurs de bus.

11. Séparateur de 2 HPRE

//RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2; // MODIFY_REG(RCC->D1CFGR, RCC_D1CFGR_HPRE, RCC_ClkInitStruct->AHBCLKDivider); //HPRE[3:0]: D1 domain AHB prescaler //1000: rcc_hclk3 = sys_d1cpre_ck / 2 RCC -> D1CFGR |= RCC_D1CFGR_HPRE_3; //1 RCC -> D1CFGR &= ~RCC_D1CFGR_HPRE_2; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_HPRE_1; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_HPRE_0; //0

12. Sans division D1CPRE

//RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1; //MODIFY_REG(RCC->D1CFGR, RCC_D1CFGR_D1CPRE, RCC_ClkInitStruct->SYSCLKDivider); //D1CPRE[3:0]: D1 domain Core prescaler //0xxx: sys_ck not divided (default after reset) RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_3; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_2; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_1; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_0; //0

13. Définissez PLL1 comme source SYSCLK et attendez la disponibilité

//RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; //MODIFY_REG(RCC->CFGR, RCC_CFGR_SW, RCC_ClkInitStruct->SYSCLKSource); //SW[2:0]: System clock switch //011: PLL1 selected as system clock (pll1_p_ck) RCC->CFGR &= ~RCC_CFGR_SW_2; //0 RCC->CFGR |= RCC_CFGR_SW_1; //1 RCC->CFGR |= RCC_CFGR_SW_0; //1 while((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL1);

14. Séparateur par 2 D1PPRE

//D1PCLK1 Configuration //RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2; //MODIFY_REG(RCC->D1CFGR, RCC_D1CFGR_D1PPRE, RCC_ClkInitStruct->APB3CLKDivider); //Bits 6:4 D1PPRE[2:0]: D1 domain APB3 prescaler //100: rcc_pclk3 = rcc_hclk3 / 2 RCC -> D1CFGR |= RCC_D1CFGR_D1PPRE_2; RCC -> D1CFGR &= ~RCC_D1CFGR_D1PPRE_1; RCC -> D1CFGR &= ~RCC_D1CFGR_D1PPRE_0;

15. Séparateur par 2 D2PPRE1

//PCLK1 Configuration //RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2; //MODIFY_REG(RCC->D2CFGR, RCC_D2CFGR_D2PPRE1, (RCC_ClkInitStruct->APB1CLKDivider)); //Bits 6:4 D2PPRE1[2:0]: D2 domain APB1 prescaler //100: rcc_pclk1 = rcc_hclk1 / 2 RCC -> D2CFGR |= RCC_D2CFGR_D2PPRE1_2; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE1_1; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE1_0;

16. Diviseur par 2 D2PPRE2

//PCLK2 Configuration //RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2; //MODIFY_REG(RCC->D2CFGR, RCC_D2CFGR_D2PPRE2, (RCC_ClkInitStruct->APB2CLKDivider)); //Bits 10:8 D2PPRE2[2:0]: D2 domain APB2 prescaler //100: rcc_pclk2 = rcc_hclk1 / 2 RCC -> D2CFGR |= RCC_D2CFGR_D2PPRE2_2; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE2_1; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE2_0;

17. Diviseur par 2 D3PPRE

//D3PCLK1 Configuration //RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2; //MODIFY_REG(RCC->D3CFGR, RCC_D3CFGR_D3PPRE, (RCC_ClkInitStruct->APB4CLKDivider) ); //Bits 6:4 D3PPRE[2:0]: D3 domain APB4 prescaler //100: rcc_pclk4 = rcc_hclk4 / 2 RCC -> D3CFGR |= RCC_D3CFGR_D3PPRE_2; RCC -> D3CFGR &= ~RCC_D3CFGR_D3PPRE_1; RCC -> D3CFGR &= ~RCC_D3CFGR_D3PPRE_0;

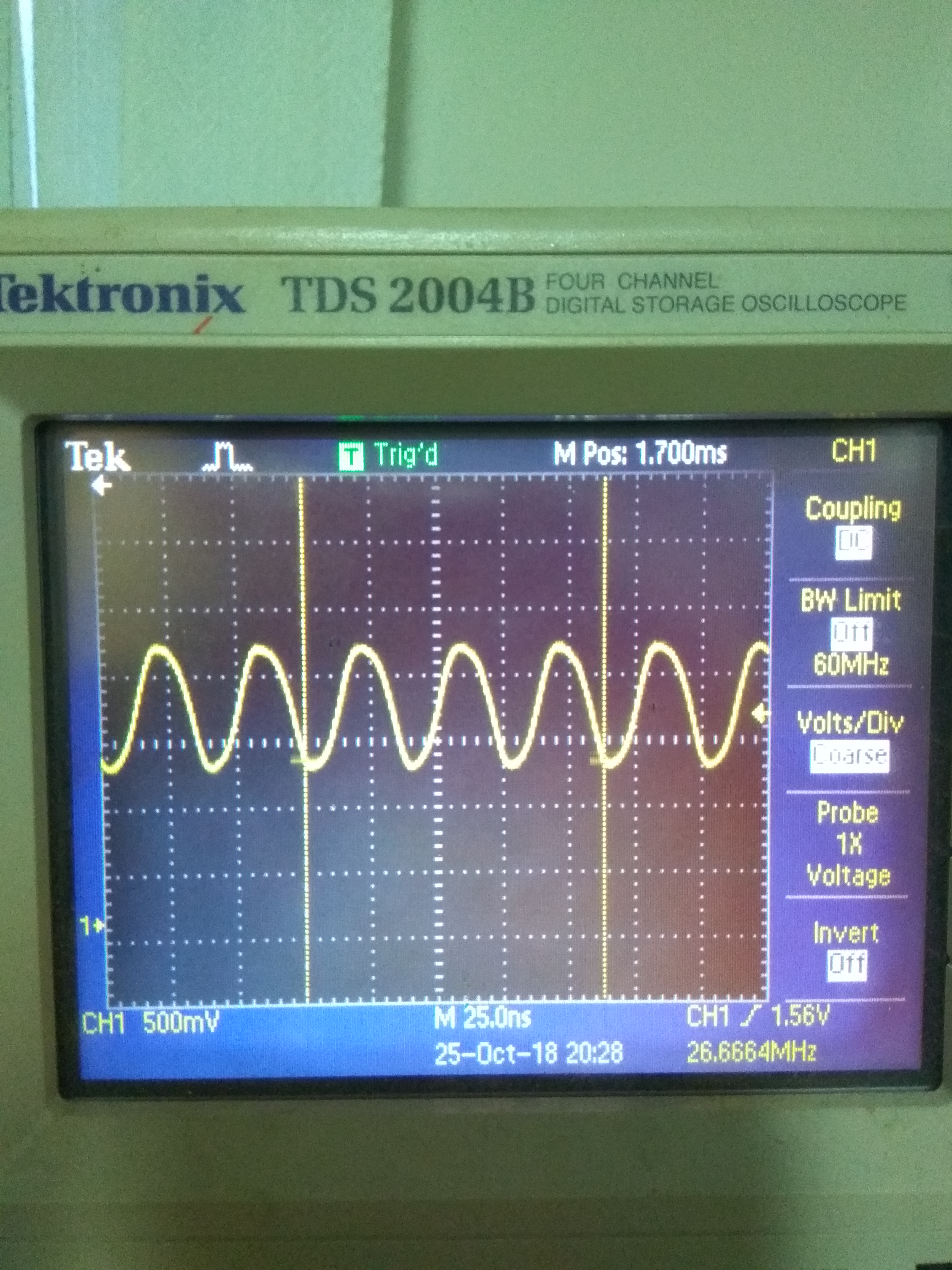

Afin de nous assurer que la configuration et le démarrage ont réussi, nous utilisons la sortie du microcontrôleur MCO2. Cette sortie doit avoir une fréquence de 26,666 MHz avec un séparateur de sortie de 15.

Super. La fréquence est présente, alors tout se fait correctement.