MCM: disposition multi-puces

La microélectronique est réputée pour un grand nombre de solutions d'ingénierie originales, étranges et efficaces. L'un d'eux est un arrangement multi-puces, qui d'une manière ou d'une autre se trouve presque partout - des postes de travail haute performance aux ordinateurs portables ultraportables, des ordinateurs à carte unique pour 10 $ aux ordinateurs centraux IBM.

Ce post parle de l'histoire de son utilisation par rapport aux processeurs à usage général.

Je

vous préviens à l'avance: je ne prétends pas être absolument compétent et académique dans ma présentation, pour la plupart je parle de ce que j'ai rencontré, travaillé et tenu entre mes mains.

Avertissement de circulation! Sous la coupe beaucoup de photos!Qu'est ce que c'est

MCM (module multi-puces, module multi-puces) ou MCP (package multi-puces, configuration multi-puces) est une solution d'ingénierie pour diviser la fonctionnalité d'un microcircuit en plusieurs puces combinées dans un seul boîtier. Il diffère des modules par le fait que les microcircuits sont généralement «nus», sans composé, et sont soudés directement par des cristaux à la carte. Il est utilisé pour augmenter le rendement des puces appropriées (en réduisant la taille d'un monocristal), une connexion compacte de cristaux réalisée selon divers processus et technologies technologiques.

Eh bien, commençons?

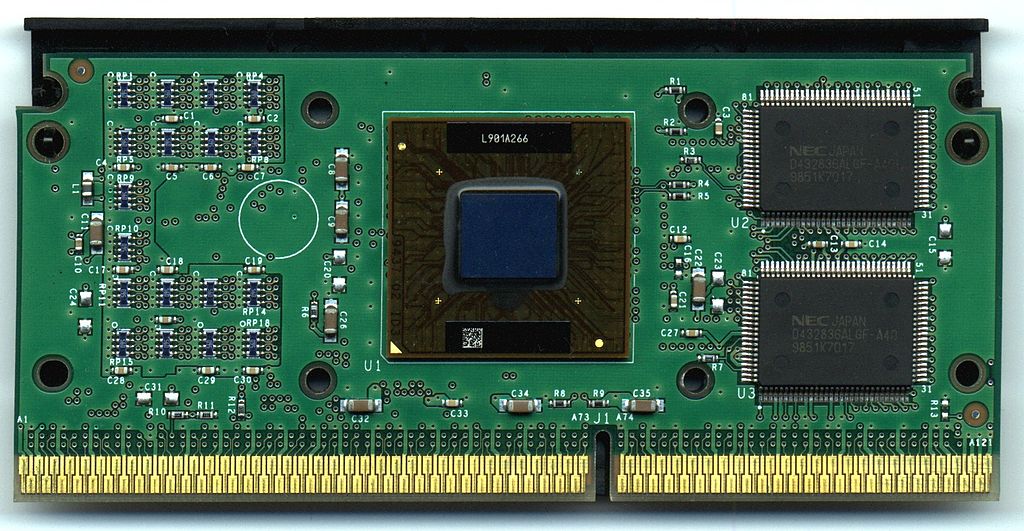

1995: Quand la cache ne rentre dans aucune porte

(alias Pentium Pro)

Cache - grognement, dimensionnel et rapide. De là, deux problèmes se posent: avec une augmentation de la vitesse de son travail, le débit de son bus devient un goulot d'étranglement, et il commence à se réchauffer. Nous devons le réparer d'une manière ou d'une autre. Le moyen le plus logique consiste à transférer L2 vers le processeur, où L1 broute depuis longtemps. Mais il y a un problème, et pas un: avec l'augmentation de la taille du cristal, le% de rejets de puce augmente, et de façon presque exponentielle. Que faire Bien sûr, faites du cache une puce séparée, mais plus proche de la principale. Du coup, on peut admirer cette brique:

La solution est bonne, mais a compliqué décemment l'emballage.

1997: Maintenant encore, mais pas la même

(alias Pentium II)

Un grand boîtier en céramique est, bien sûr, bon, mais cher. Essayez de rejouer? Et pourquoi pas. La tâche est de le rendre moins cher, et c’est tout. Le transfert du cache vers la carte n'est pas une option - ce serait un pas en arrière. Et la largeur du bus de cache a également augmenté ... Peut-il tout combiner avec le refroidissement en un seul module? Le Pentium II est donc né:

Vous ne pouvez bien sûr pas considérer ce MCM, mais puisque je m'en suis souvenu, il sera ici.

(au fait, sans ce vieil homme permanent et immortel, votre humble serviteur n'aurait pas écrit cet article - le PII-400, qui travaille pour moi en tant que passerelle et routeur WiFi depuis de nombreuses années, ayant survécu à beaucoup de ses descendants)

2005: D - signifie Double Bottom

(alias Pentium D)

Lorsque le plan est «Un noyau, mais à GARDER!» il a commencé à craquer considérablement au niveau des coutures, et les concurrents, en riant, étaient sur le point de libérer des processeurs double cœur sur une puce, devaient faire quelque chose, et rapidement. Donc, cet atavisme est apparu, par lequel ils ont bouché un trou sur le marché, tandis que les principales forces étaient jetées sur l'architecture Core plus prometteuse. La raison principale de l'utilisation de cette solution était probablement la réduction du temps de développement - la taille des cristaux n'était pas si grande que le doublage posait des problèmes. Eh bien, c'est arrivé:

Il y avait des processeurs Xeon similaires pour le segment des serveurs, mais je peux en dire peu à leur sujet.

2007: Pourquoi pas?

(alias Core 2 Quad)

Depuis que nous avons maîtrisé les cristaux à double cœur en 2006, alors pourquoi filtrer? Nous utilisons une solution éprouvée - collez deux cristaux dans un seul boîtier et il n'y a aucun problème! Il n'y a rien à dire, l'image n'a pas beaucoup changé:

Les Xeon de cette époque l'étaient également, à l'exception du modèle à six cœurs - il y a un gros cristal.

2010: Avant l'arrivée du sable

(alias Core i3 de première génération / 5/7)

Sur les processeurs Core i double cœur de première génération, ils ont décidé d'exécuter le processus 32 nm, ce qui est assez drôle - sur le processus 45 nm éprouvé, ils ont créé un noyau vidéo intégré et un contrôleur de mémoire, et deux cœurs avec cache ont été placés sur un cristal 32 nm séparé. Alors que leurs homologues quad-core plus anciens utilisaient le processus 45 nm! Les tailles de cristaux sont aussi amusantes:

(Cependant, le cœur vidéo des processeurs double cœur et maintenant souvent plus que les deux cœurs combinés)

2011: Un bulldozer c'est bien, et deux c'est mieux

(alias Opteron 6000)

Le cristal est déjà si gros, la technologie pour leur production est ajustée, quels sont en fait les problèmes? NUMA? Mais nous faisons déjà ces processeurs pour serveurs et multi-socket. Puisqu'il n'y a aucun problème, nous collectons deux cristaux sous un même couvercle:

(Ouais, et puis les gens s'amusent - le processeur est un, et les nœuds NUMA sont deux)

2013: caramel écossais mais non comestible

(aka eDRAM L4 GPU / CPU cache)

À partir de la génération Haswell, les processeurs équipés de graphiques intégrés Iris Pro / Iris Plus (et dans la génération Skylake, ceux avec Iris standard) sont livrés dans le même package avec une puce de mémoire de 64/128 Mo qui fonctionne comme un cache L4 et augmente très sérieusement les performances des graphiques intégrés. Et la puce n'est pas petite (bien que la mémoire occupe toujours beaucoup d'espace):

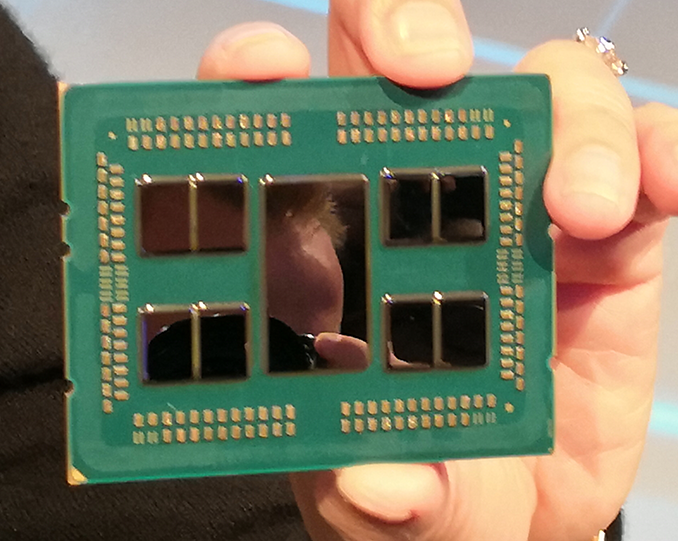

2017: année où Intel shit brix

(alias Ryzen Threadripper & EPYC)

Les ingénieurs d'AMD ont joué avec Infinity Fabric, joué ... Et puis - oups! Quatre cristaux sous un couvercle connectés par IF chacun à chacun (dans le cas d'EPYC côté serveur) ou une paire les uns des autres (Threadripper avec deux cristaux actifs). Tout va bien, un seul problème est NUMA (jusqu'à 4 nœuds par processeur!), Mais c'est un problème exclusivement pour les logiciels qui n'y sont pas adaptés. Donc ça s'est très bien passé:

2018: doubler le nombre - doubler le plaisir

(alias Zen 2 et Cascade Lake AP)

Nous sommes donc arrivés à l'actualité. Le 5 novembre, Intel a rapidement annoncé les processeurs double puce à 48 cœurs (ils n'avaient même pas le temps de prendre des photos), et le 6 novembre, AMD a présenté de nouveaux EPYC lors de son événement Next Horizon. Mille mots seront remplacés par une image:

Neuf cristaux. Neuf putain! Les raisons de cette décision sont claires pour moi, et elles sont très simples: dans le but d'augmenter la sortie de puces entières, de réduire le coût total du processeur et d'accélérer le développement. 7 nm est encore un processus brut. Intel, avec ses 10 nm (+ - égal à 7 nm TSMC process) déjà issu de ce râteau. Tant et si bien, que nous avons encore vu des processeurs 10 nm vivre uniquement sous la forme d'un modèle de stub i3 pour ordinateur portable.

Le cristal central est fabriqué selon un processus éprouvé de 14 nm et fonctionne comme un contrôleur de mémoire et toutes les entrées / sorties sauf PCIe 4.0, dont 16 lignes sont fournies par chacun des cristaux satellites avec huit cœurs chacun.

Un contrôleur de mémoire commun fournit l'essentiel - un accès uniforme à la mémoire (UMA). Et il ne sera jamais superflu.

Temps de spéculation

Le cristal central est connecté aux satellites à l'aide d'Infinity Fabric, qui à son tour offre un grand nombre de possibilités d'utilisation des composants à la fois ensemble et séparément. Besoin d'un processeur de bureau 16 cœurs? Nous scions un cristal avec un contrôleur de mémoire à double canal et connecté à deux complexes nucléaires sous un même couvercle. Besoin d'un processeur avec carte graphique intégrée? Nous jetons un complexe nucléaire, au lieu de cela, nous mettons la puce GPU. Le coût de l'extension de la gamme de processeurs diminuera d'un ordre de grandeur. Une réduction de la taille des cristaux individuels réduit le pourcentage de rejets, ce qui à son tour a un effet positif sur le coût.

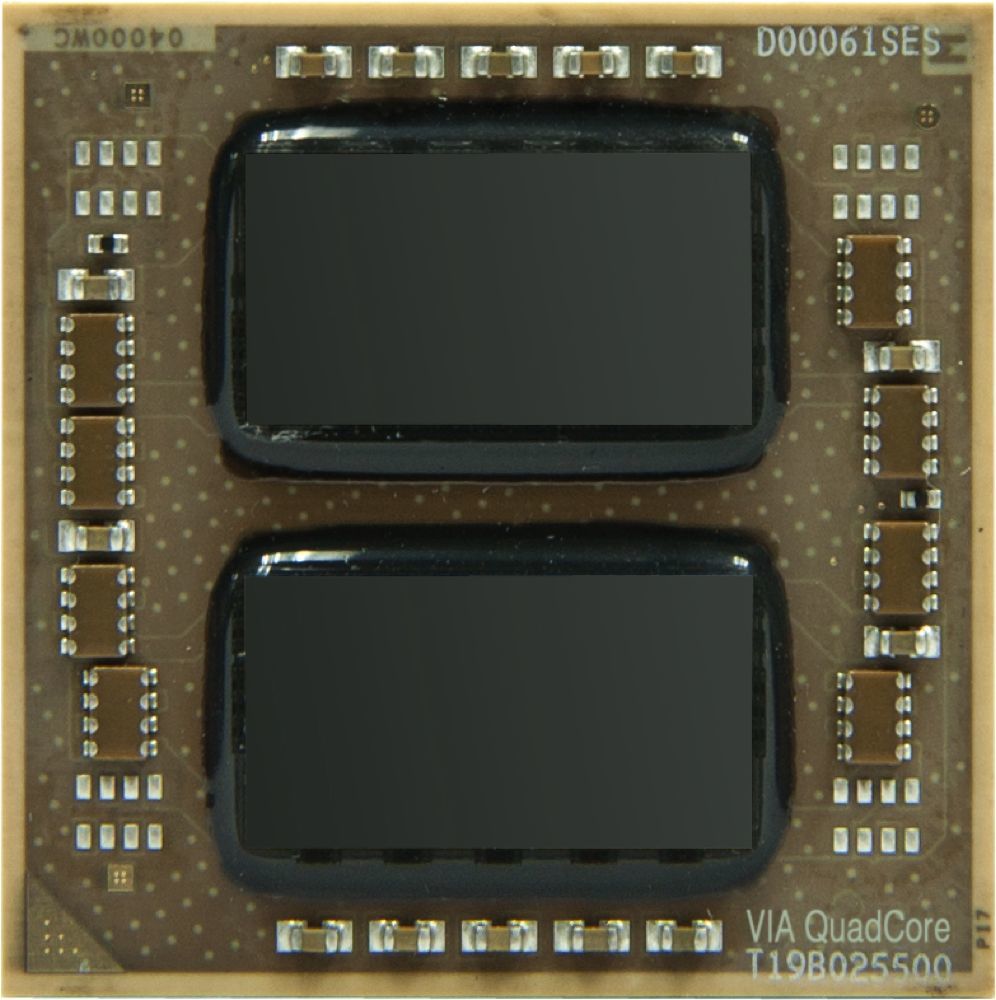

Moar geek porn

Quelque chose que je n'ai pas écrit, mais qui mérite d'être mentionné: Via Nano QuadCore, je l'ai complètement oublié. Je n'avais rien à faire avec elle, il n'y avait rien à dire.

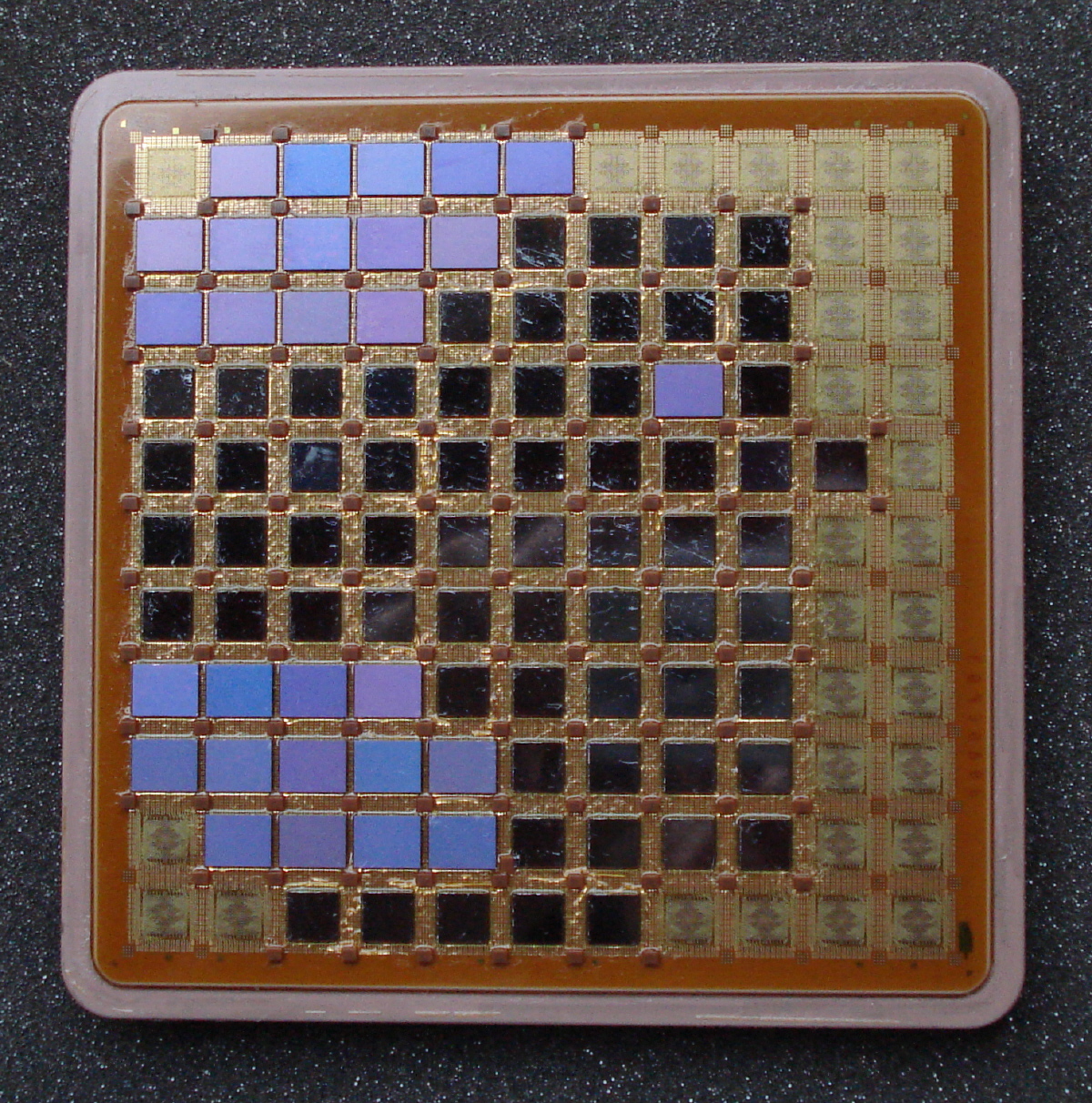

Via Nano QuadCore, je l'ai complètement oublié. Je n'avais rien à faire avec elle, il n'y avait rien à dire. IBM CPU 9121/311

IBM CPU 9121/311 Puissance Ibm 5

Puissance Ibm 5 Et encore plus de Power 7

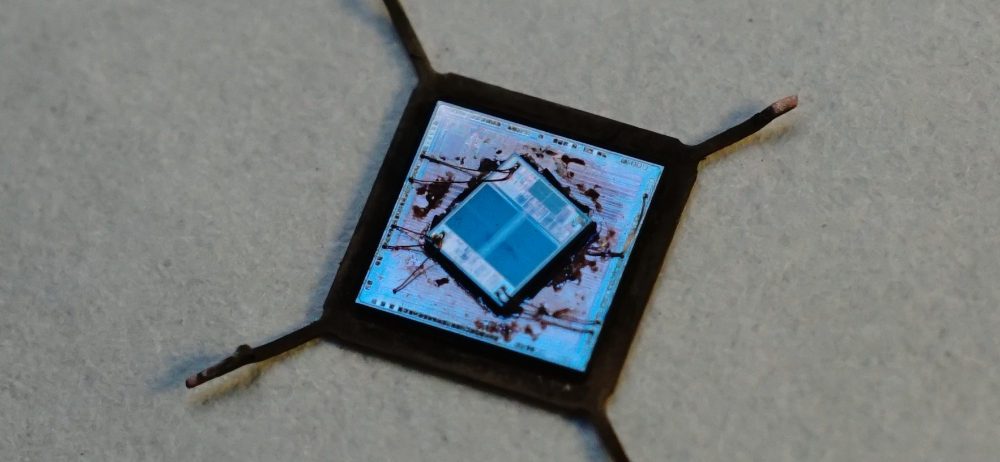

Et encore plus de Power 7 Microcontrôleur GD32, puce de mémoire flash sur le dessus. Photo d'un ami BarsMonster

Microcontrôleur GD32, puce de mémoire flash sur le dessus. Photo d'un ami BarsMonster