Bonjour, cher lecteur! On m'a demandé d'écrire sur UHCI - eh bien, j'écris.

Cet article peut vous être utile si, par exemple, vous n'avez pas les compétences suffisantes en écriture pour les pilotes et en lecture de documentation pour un matériel. Un exemple simple: vous voulez écrire votre système d'exploitation pour un mini-PC, afin que certaines distributions Windows ou Linux ne téléchargent pas de matériel, et vous utilisez toute sa puissance exclusivement à vos propres fins.

Qu'est-ce que l'UHCI?

Je pense, afin de ne pas pulvériser à nouveau sur le sujet de quoi et pourquoi, il suffit de laisser un lien vers mon article précédent sur EHCI.

Piquez iciUHCI - Universal Host Controller Interface, fonctionne comme un périphérique PCI, mais, contrairement à EHCI, utilise des ports au lieu de MMIO (Memory-Mapped-IO).

Termes à utiliser ci-après

- Pilote USB (USBD) - le pilote USB lui-même

- HC (Host Controller) - un contrôleur hôte, ou tout simplement notre UHCI

- Host Controller Driver (HCD) - un pilote qui connecte le matériel et l'USBD

- Périphérique USB - Périphérique USB lui-même

Types de transfert de données

Isochronous - transmission isosynchrone, qui a une fréquence donnée de transfert de données. Il peut être utilisé, par exemple, pour des microphones USB, etc.

Interruption - Petits transferts de données spontanés à partir d'un appareil. Le type de transmission d'interruption prend en charge les dispositifs qui nécessitent un intervalle de service prévisible mais ne fournissent pas nécessairement un flux de données prévisible. Couramment utilisé pour les périphériques tels que les claviers et les périphériques de pointage qui peuvent ne pas fournir de données pendant de longues périodes, mais nécessitent une réponse rapide lorsqu'ils ont des données à envoyer.

Contrôle - Type de transmission d'informations sur l'état, l'état et la configuration de l'appareil. Le type de transfert de contrôle est utilisé pour fournir un canal de contrôle de l'hôte aux périphériques USB. Les transmissions de contrôle se composent toujours d'une phase de configuration et de zéro ou plusieurs phases de données suivies d'une phase d'état. Il est impératif que le transfert de contrôle vers un point d'extrémité donné soit traité en mode FIFO. Si le contrôle est transmis au même point de terminaison, l'entrelacement peut entraîner un comportement imprévisible.

En vrac - type de transfert de tableaux de données. Utilisé, par exemple, dans les appareils MassStorage.

Voici à quoi ressemble la distribution temporelle 1 ms - traitement d'une image.

Distribution du temps

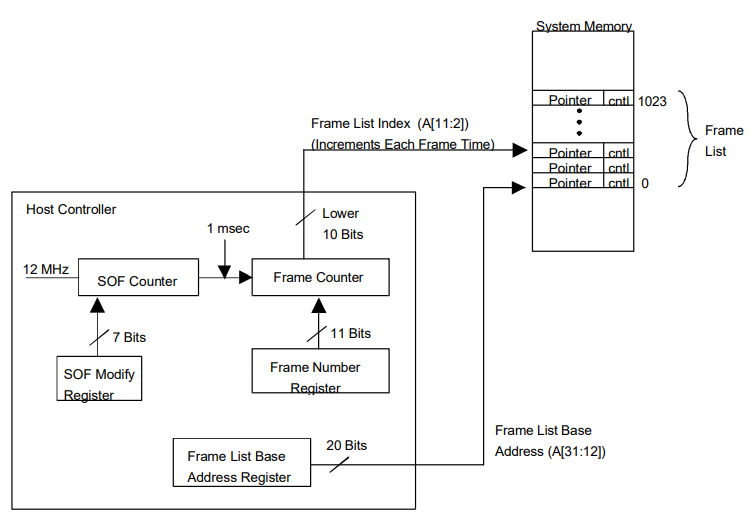

Le contrôleur hôte prend en charge la livraison de données en temps réel en générant un paquet de début de trame (SOF) toutes les 1 ms. Un paquet SOF est généré lorsque le compteur SOF du contrôleur hôte expire (figure 3). Le contrôleur hôte initialise le compteur SOF pour une durée de trame de 1 ms. De petites modifications peuvent être apportées à cette valeur (et donc à la période de temps de trame) en programmant le registre de changement SOF. Cette fonction vous permet d'apporter des modifications mineures à la période de trame, si nécessaire, pour maintenir la synchronisation en temps réel sur l'ensemble du système USB.

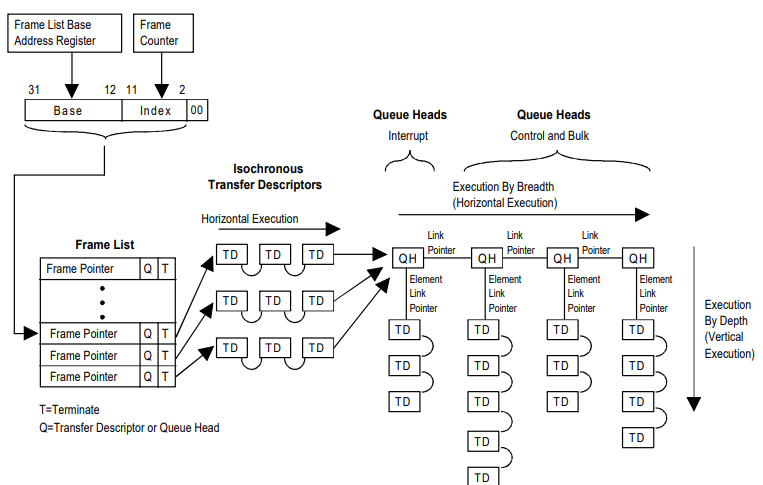

Le contrôleur hôte inclut le numéro de trame dans chaque paquet SOF. Ce numéro de trame détermine uniquement la période de trame en temps réel. La condition de fin de trame (EOF) se produit à la fin de l'intervalle de temps de 1 ms lorsque le contrôleur hôte démarre la prochaine trame, générant un autre paquet SOF avec le numéro de trame correspondant. Pendant la période de trame, les données sont transmises sous forme de paquets d'informations. La période de trame est strictement appliquée par le contrôleur hôte, et les paquets de données dans la trame actuelle ne peuvent pas aller au-delà de l'EOF (voir le chapitre 11 dans la spécification USB). Le contrôleur hôte prend en charge la synchronisation de la transmission de données entre les trames en temps réel, reliant le numéro de trame pour effectuer une entrée spécifique dans la liste des trames. Le compteur de trames du contrôleur hôte génère un numéro de trame (valeur 11 bits) et l'inclut dans chaque paquet SOF. Le compteur est programmé via des registres et chaque période de trame est incrémentée. Le contrôleur hôte utilise les 10 bits inférieurs du numéro de trame comme index dans la liste de trames avec 1024 trames, qui est stockée dans la mémoire système. Ainsi, puisque le compteur de trames contrôle la sélection d'une entrée dans la liste de trames, le contrôleur hôte traite chaque entrée de la liste dans une période de trame donnée. Le contrôleur hôte se développe à l'entrée suivante dans la liste de trames pour chaque nouvelle trame. Cela garantit que les transmissions isochrones sont effectuées dans une trame spécifique.

Figure 3:

Structure UHCI

Tout est exactement le même qu'avec EHCI. Exemples de demandes à HC:

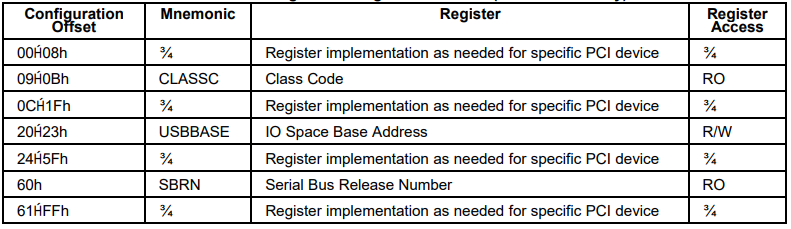

Configurer et accéder à UHCI

Et donc, comme je l'ai dit plus tôt, UHCI fonctionne via des ports, donc à partir de PCI, nous devons trouver la base des registres UHCI.

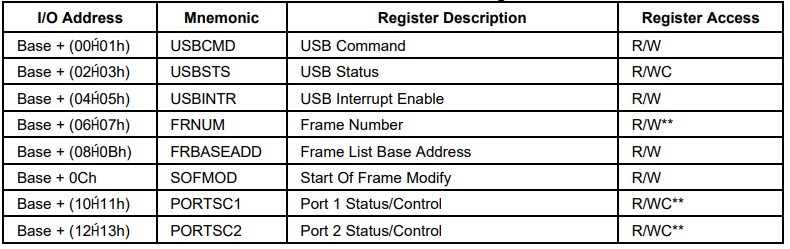

Au décalage 0x20, il y a 4 octets - IO Base. Concernant IO Base, nous pouvons utiliser les registres suivants:

Registres UHCI

- USBCMD est un registre pour contrôler HC. Bits:

- Le bit 6 est un indicateur que le périphérique est configuré et initialisé avec succès.

- Bit 1 - Réinitialisation HC. Réglez pour réinitialiser HC.

- Bit 0 - Run / Stop. Affiche l'état HC. 1 - fonctionne, 0 - non.

- USBSTS - Registre d'état. Bits:

- Bit 5 - HC arrêté. Une erreur s'est produite ou le contrôleur a réussi la réinitialisation HC.

- Bit 4 - Erreur de processus du contrôleur hôte. Le bit est mis à 1 lorsqu'une erreur critique s'est produite et que HC ne peut pas continuer la mise en file d'attente et TD.

- Bit 3 - Erreur du système hôte. Erreur PCI.

- Bit 1 - Interruption d'erreur. Indique qu'une erreur s'est produite et que le HC a généré une interruption.

- Bit 0 - Interrompre. Indique que HC a généré une interruption.

- USBINTR - Registre des paramètres d'interruption. Bits:

- Le bit 2 - IOC - Interruption à la fin - génère une interruption à la fin de la transaction.

- FRNUM - Numéro de la trame actuelle (Take it & 0x3FF pour la valeur correcte).

- FLBASEADD - Frame List Base Address - adresse de la liste des trames.

- PORTSC - Statut et contrôle des ports - registre d'état et de contrôle des ports. Bits:

- Bit 9 - Port Reset - 1 - port à réinitialiser.

- Bit 8 - indique qu'un périphérique basse vitesse est connecté au port

- Bit 3 - Indique que l'état du port sur a changé

- Bit 2 - Indique si le port est activé

- Bit 1 - indique que l'état de l'appareil est connecté au port

- Bit 0 - indique que l'appareil est connecté au port.

Structures

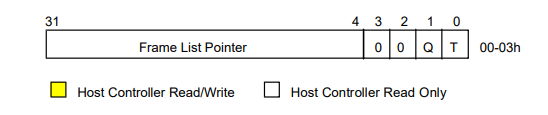

Pointeur de liste d'images

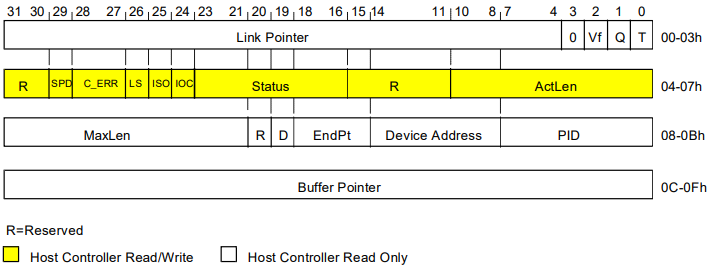

Descrptor de transfert

CONTRÔLE ET ÉTAT TD

. Bits:

- Bits 28-27 - compteur d'erreurs, similaire à EHCI.

- Bit 26 - 1 = appareil à basse vitesse, 0 = appareil à pleine vitesse.

- Bit 25 - 1 = TD isosynchrone

- Bit 24 - IOC

- Bits 23-16 - Statut:

- Bit 23 - Indique qu'il s'agit d'un TD actif

- Bit 22 - au point mort

- Bit 21 - Erreur de tampon de données

- Bit 20 - Babble détecté

- Bit 19 - NAK

- Bits 10–0: nombre d'octets transmis par le contrôleur hôte.

Jeton TD

- Bits 31:21 - Max Packet Len, similaire à EHCI

- Bit 19 - Basculement des données, similaire à EHCI

- Bits 18:15 - Numéro du point final

- Bits 18:14 - adresse de l'appareil

- Bits 7: 0 - PID. In = 0x69, Out = 0xE1, Setup = 0x2D

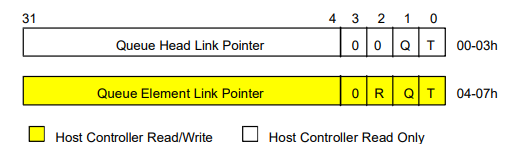

Tête de file d'attente

Code

Initialisez et configurez HC:

PciBar bar; PciGetBar(&bar, id, 4); if (~bar.flags & PCI_BAR_IO) {

Demandes de point de terminaison et de contrôle: