Dans la

partie précédente, nous avons examiné l'évolution de la livraison d'interruption à partir de dispositifs dans des systèmes x86 (PIC → APIC → MSI), une théorie générale et tous les termes nécessaires.

Dans cette partie pratique, nous verrons comment revenir à l'utilisation des méthodes de livraison d'interruption Linux héritées, à savoir, considérer les options de démarrage du noyau:

Nous verrons également l'ordre dans lequel l'OS regarde les tables de routage d'interruption (ACPI / MPtable / $ PIR) et quel effet cela aura sur l'ajout d'options de démarrage:

- pci = noacpi

- acpi = noirq

- acpi = off

Vous avez peut-être essayé des combinaisons de toutes ces options lorsqu'un appareil ne fonctionnait pas en raison d'un problème d'interruption. Voyons ce qu’ils font exactement et comment ils modifient la sortie de / proc / interrupts.

Télécharger sans options supplémentaires

Nous allons observer les interruptions dans cet article sur une carte personnalisée avec Intel Haswell i7 avec le chipset lynxPoint-LP sur lequel s'exécute le

coreboot .

Nous afficherons des informations sur les interruptions via la commande

cat /proc/interrupts

Sortie au démarrage sans options supplémentaires:

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 0 1 0 1 IO-APIC-edge i8042 8: 0 0 0 1 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-fasteoi acpi 12: 0 0 0 1 IO-APIC-edge 23: 16 247 7 10 IO-APIC-fasteoi ehci_hcd:usb1 56: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 57: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 58: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 59: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 60: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 61: 0 0 0 0 PCI-MSI-edge aerdrv,PCIe PME 62: 3118 1984 972 3454 PCI-MSI-edge ahci 63: 1 0 0 0 PCI-MSI-edge eth59 64: 2095 57 4 832 PCI-MSI-edge eth59-rx-0 65: 6 18 1 1309 PCI-MSI-edge eth59-rx-1 66: 13 512 2 1 PCI-MSI-edge eth59-rx-2 67: 10 61 232 2 PCI-MSI-edge eth59-rx-3 68: 169 0 0 0 PCI-MSI-edge eth59-tx-0 69: 14 14 4 205 PCI-MSI-edge eth59-tx-1 70: 11 491 3 0 PCI-MSI-edge eth59-tx-2 71: 20 19 134 50 PCI-MSI-edge eth59-tx-3 72: 0 0 0 0 PCI-MSI-edge eth58 73: 2 1 0 152 PCI-MSI-edge eth58-rx-0 74: 3 150 2 0 PCI-MSI-edge eth58-rx-1 75: 2 34 117 2 PCI-MSI-edge eth58-rx-2 76: 153 0 2 0 PCI-MSI-edge eth58-rx-3 77: 4 0 2 149 PCI-MSI-edge eth58-tx-0 78: 4 149 2 0 PCI-MSI-edge eth58-tx-1 79: 4 0 117 34 PCI-MSI-edge eth58-tx-2 80: 153 0 2 0 PCI-MSI-edge eth58-tx-3 81: 66 106 2 101 PCI-MSI-edge snd_hda_intel 82: 928 5657 262 224 PCI-MSI-edge i915 83: 545 56 32 15 PCI-MSI-edge snd_hda_intel NMI: 0 0 0 0 Non-maskable interrupts LOC: 4193 3644 3326 3499 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 290 233 590 111 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1339 2163 2404 1946 Rescheduling interrupts CAL: 607 537 475 559 Function call interrupts TLB: 163 202 164 251 TLB shootdowns TRM: 48 48 48 48 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 3 3 3 3 Machine check polls ERR: 0 MIS: 0

Le fichier / proc / interrupts fournit un tableau sur le nombre d'interruptions sur chaque processeur sous la forme suivante:

- Première colonne: numéro d'interruption

- Haut-parleurs CPUx: compteurs d'interruption sur chaque processeur

- Colonne suivante: type d'interruption:

- IO-APIC-edge - interruption de front au contrôleur I / O APIC

- IO-APIC-fasteoi - interruption de niveau par contrôleur d'E / S APIC

- PCI-MSI-edge - interruption MSI

- XT-PIC-XT-PIC - interruption sur le contrôleur PIC (voir plus loin)

- Dernière colonne: appareil associé à cette interruption

Ainsi, comme cela devrait être le cas dans un système moderne, ils sont utilisés pour les périphériques et les pilotes qui prennent en charge les interruptions MSI / MSI-X. Les autres interruptions sont acheminées via l'APIC d'E / S.

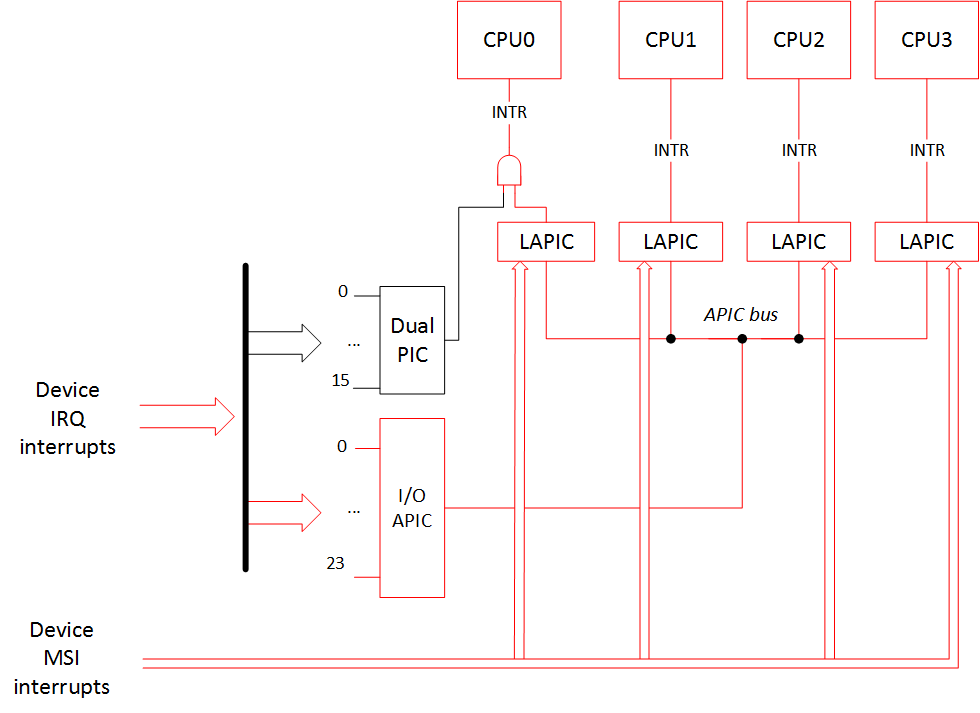

Le schéma de routage d'interruption simplifié peut être tracé comme ceci (chemins actifs marqués en rouge, chemins inutilisés en noir).

La prise en charge d'un périphérique MSI / MSI-X doit être étiquetée comme capacité correspondante dans son espace de configuration PCI.

En confirmation, nous donnons un petit fragment de la sortie lspci pour les appareils pour lesquels il est indiqué qu'ils utilisent MSI / MSI-X. Dans notre cas, il s'agit d'un contrôleur SATA (interruption ahci), de 2 contrôleurs ethernet (interruptions eth58 * et eth59 *), d'un contrôleur graphique (i915) et de 2 contrôleurs HD Audio (snd_hda_intel).

lspci -v

00:02.0 VGA compatible controller: Intel Corporation Haswell-ULT Integrated Graphics Controller (rev 09) (prog-if 00 [VGA controller]) ... Capabilities: [90] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [d0] Power Management version 2 Capabilities: [a4] PCI Advanced Features Kernel driver in use: i915 00:03.0 Audio device: Intel Corporation Haswell-ULT HD Audio Controller (rev 09 ... Capabilities: [60] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [70] Express Root Complex Integrated Endpoint, MSI 00 Kernel driver in use: snd_hda_intel 00:1b.0 Audio device: Intel Corporation 8 Series HD Audio Controller (rev 04) ... Capabilities: [60] MSI: Enable+ Count=1/1 Maskable- 64bit+ Capabilities: [70] Express Root Complex Integrated Endpoint, MSI 00 Capabilities: [100] Virtual Channel Kernel driver in use: snd_hda_intel 00:1f.2 SATA controller: Intel Corporation 8 Series SATA Controller 1 [AHCI mode] (rev 04) (prog-if 01 [AHCI 1.0]) ... Capabilities: [80] MSI: Enable+ Count=1/1 Maskable- 64bit- Capabilities: [70] Power Management version 3 Capabilities: [a8] SATA HBA v1.0 Kernel driver in use: ahci 05:00.0 Ethernet controller: Intel Corporation I350 Gigabit Network Connection (rev 01) ... Capabilities: [50] MSI: Enable- Count=1/1 Maskable+ 64bit+ Capabilities: [70] MSI-X: Enable+ Count=10 Masked- Capabilities: [a0] Express Endpoint, MSI 00 Kernel driver in use: igb 05:00.1 Ethernet controller: Intel Corporation I350 Gigabit Network Connection (rev 01) ... Capabilities: [50] MSI: Enable- Count=1/1 Maskable+ 64bit+ Capabilities: [70] MSI-X: Enable+ Count=10 Masked- Capabilities: [a0] Express Endpoint, MSI 00 Kernel driver in use: igb

Comme nous pouvons le voir, ces appareils ont la ligne «MSI: Enable +» ou «MSI-X: Enable +»

Commençons à dégrader le système. Tout d'abord, démarrez avec l'option pci = nomsi.

pci = nomsi

Avec cette option, les interruptions MSI deviendront IO-APIC / XT-PIC selon le contrôleur d'interruption utilisé.

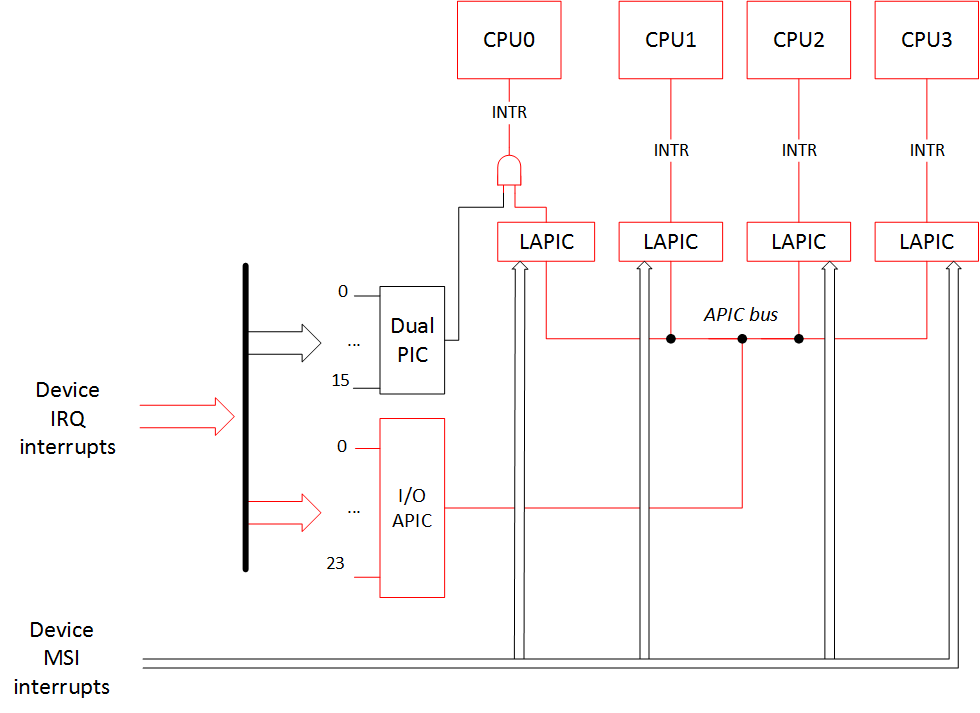

Dans ce cas, nous avons toujours le contrôleur d'interruption APIC prioritaire, donc l'image sera comme ceci:

La sortie de / proc / interrupts:

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 0 1 0 1 IO-APIC-edge i8042 8: 0 0 1 0 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-fasteoi acpi 12: 0 0 0 1 IO-APIC-edge 16: 1314 5625 342 555 IO-APIC-fasteoi i915, snd_hda_intel, eth59 17: 5 0 1 34 IO-APIC-fasteoi eth58 21: 2882 2558 963 2088 IO-APIC-fasteoi ahci 22: 26 81 2 170 IO-APIC-fasteoi snd_hda_intel 23: 23 369 8 8 IO-APIC-fasteoi ehci_hcd:usb1 NMI: 0 0 0 0 Non-maskable interrupts LOC: 3011 3331 2435 2617 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 197 228 544 85 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1708 2349 1821 1569 Rescheduling interrupts CAL: 520 554 509 555 Function call interrupts TLB: 187 181 205 179 TLB shootdowns TRM: 102 102 102 102 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Toutes les interruptions MSI / MSI-X devraient disparaître. Au lieu de cela, les appareils utilisent désormais des interruptions IO-APIC-fasteoi.

Notez qu'avant l'inclusion de cette option, eth58 et eth59 avaient 9 interruptions chacune! Et maintenant, un seul à la fois. Après tout, comme nous le rappelons, sans MSI une fonction PCI, une seule interruption est disponible!

Quelques informations de dmesg sur l'initialisation des contrôleurs Ethernet:

- téléchargement sans option pci = nomsi:

igb: Intel(R) Gigabit Ethernet Network Driver - version 5.0.5-k igb: Copyright (c) 2007-2013 Intel Corporation. acpi:acpi_pci_irq_enable: igb 0000:05:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16 igb 0000:05:00.0: irq 63 for MSI/MSI-X igb 0000:05:00.0: irq 64 for MSI/MSI-X igb 0000:05:00.0: irq 65 for MSI/MSI-X igb 0000:05:00.0: irq 66 for MSI/MSI-X igb 0000:05:00.0: irq 67 for MSI/MSI-X igb 0000:05:00.0: irq 68 for MSI/MSI-X igb 0000:05:00.0: irq 69 for MSI/MSI-X igb 0000:05:00.0: irq 70 for MSI/MSI-X igb 0000:05:00.0: irq 71 for MSI/MSI-X igb 0000:05:00.0: irq 63 for MSI/MSI-X igb 0000:05:00.0: irq 64 for MSI/MSI-X igb 0000:05:00.0: irq 65 for MSI/MSI-X igb 0000:05:00.0: irq 66 for MSI/MSI-X igb 0000:05:00.0: irq 67 for MSI/MSI-X igb 0000:05:00.0: irq 68 for MSI/MSI-X igb 0000:05:00.0: irq 69 for MSI/MSI-X igb 0000:05:00.0: irq 70 for MSI/MSI-X igb 0000:05:00.0: irq 71 for MSI/MSI-X igb 0000:05:00.0: added PHC on eth0 igb 0000:05:00.0: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.0: eth0: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2a igb 0000:05:00.0: eth0: PBA No: 106300-000 igb 0000:05:00.0: Using MSI-X interrupts. 4 rx queue(s), 4 tx queue(s) acpi:acpi_pci_irq_enable: igb 0000:05:00.1: PCI INT B -> GSI 17 (level, low) -> IRQ 17 igb 0000:05:00.1: irq 72 for MSI/MSI-X igb 0000:05:00.1: irq 73 for MSI/MSI-X igb 0000:05:00.1: irq 74 for MSI/MSI-X igb 0000:05:00.1: irq 75 for MSI/MSI-X igb 0000:05:00.1: irq 76 for MSI/MSI-X igb 0000:05:00.1: irq 77 for MSI/MSI-X igb 0000:05:00.1: irq 78 for MSI/MSI-X igb 0000:05:00.1: irq 79 for MSI/MSI-X igb 0000:05:00.1: irq 80 for MSI/MSI-X igb 0000:05:00.1: irq 72 for MSI/MSI-X igb 0000:05:00.1: irq 73 for MSI/MSI-X igb 0000:05:00.1: irq 74 for MSI/MSI-X igb 0000:05:00.1: irq 75 for MSI/MSI-X igb 0000:05:00.1: irq 76 for MSI/MSI-X igb 0000:05:00.1: irq 77 for MSI/MSI-X igb 0000:05:00.1: irq 78 for MSI/MSI-X igb 0000:05:00.1: irq 79 for MSI/MSI-X igb 0000:05:00.1: irq 80 for MSI/MSI-X igb 0000:05:00.1: added PHC on eth1 igb 0000:05:00.1: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.1: eth1: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2b igb 0000:05:00.1: eth1: PBA No: 106300-000 igb 0000:05:00.1: Using MSI-X interrupts. 4 rx queue(s), 4 tx queue(s)

- démarrer avec l'option pci = nomsi

igb: Intel(R) Gigabit Ethernet Network Driver - version 5.0.5-k igb: Copyright (c) 2007-2013 Intel Corporation. acpi:acpi_pci_irq_enable: igb 0000:05:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16 igb 0000:05:00.0: added PHC on eth0 igb 0000:05:00.0: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.0: eth0: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2a igb 0000:05:00.0: eth0: PBA No: 106300-000 igb 0000:05:00.0: Using legacy interrupts. 1 rx queue(s), 1 tx queue(s) acpi:acpi_pci_irq_enable: igb 0000:05:00.1: PCI INT B -> GSI 17 (level, low) -> IRQ 17 igb 0000:05:00.1: added PHC on eth1 igb 0000:05:00.1: Intel(R) Gigabit Ethernet Network Connection igb 0000:05:00.1: eth1: (PCIe:5.0Gb/s:Width x1) 00:15:d5:03:00:2b igb 0000:05:00.1: eth1: PBA No: 106300-000 igb 0000:05:00.1: Using legacy interrupts. 1 rx queue(s), 1 tx queue(s)

En raison de la réduction du nombre d'interruptions par périphérique, l'activation de cette option peut limiter considérablement les performances du pilote (cela ne tient pas compte du fait que, selon Intel

Reducing Interrupt Latency Through the Use of Message Signaled Interrupts, les interruptions via MSI sont 3 fois plus rapides que via IO -APIC et 5 fois plus rapide que via PIC).

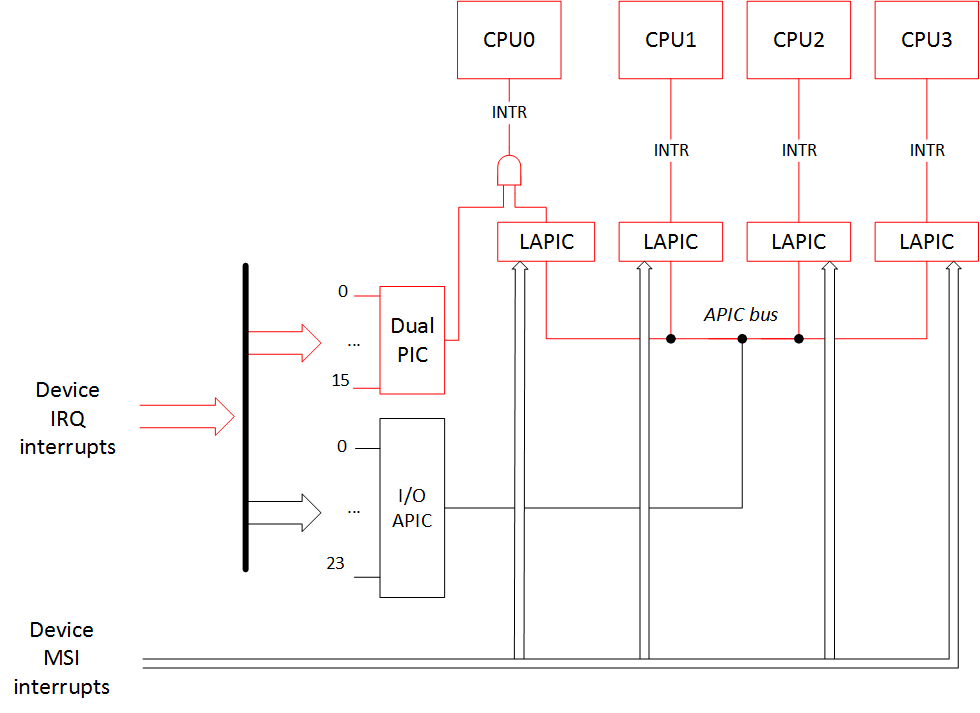

noapic

Cette option désactive les E / S APIC. Les interruptions MSI peuvent toujours aller à tous les CPU, mais les interruptions des périphériques ne peuvent aller qu'à CPU0, car le PIC n'est connecté qu'à CPU0. Mais LAPIC fonctionne et d'autres processeurs peuvent fonctionner et gérer les interruptions.

CPU0 CPU1 CPU2 CPU3 0: 5 0 0 0 XT-PIC-XT-PIC timer 1: 2 0 0 0 XT-PIC-XT-PIC i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 8: 1 0 0 0 XT-PIC-XT-PIC rtc0 9: 0 0 0 0 XT-PIC-XT-PIC acpi 12: 172 0 0 0 XT-PIC-XT-PIC ehci_hcd:usb1 56: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 57: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 58: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 59: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 60: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 61: 0 0 0 0 PCI-MSI-edge aerdrv, PCIe PME 62: 2833 2989 1021 811 PCI-MSI-edge ahci 63: 0 1 0 0 PCI-MSI-edge eth59 64: 301 52 9 3 PCI-MSI-edge eth59-rx-0 65: 12 24 3 178 PCI-MSI-edge eth59-rx-1 66: 14 85 6 2 PCI-MSI-edge eth59-rx-2 67: 17 24 307 1 PCI-MSI-edge eth59-rx-3 68: 70 18 8 10 PCI-MSI-edge eth59-tx-0 69: 7 0 0 23 PCI-MSI-edge eth59-tx-1 70: 15 227 2 2 PCI-MSI-edge eth59-tx-2 71: 18 6 27 2 PCI-MSI-edge eth59-tx-3 72: 0 0 0 0 PCI-MSI-edge eth58 73: 1 0 0 27 PCI-MSI-edge eth58-rx-0 74: 1 22 0 5 PCI-MSI-edge eth58-rx-1 75: 1 0 22 5 PCI-MSI-edge eth58-rx-2 76: 23 0 0 5 PCI-MSI-edge eth58-rx-3 77: 1 0 0 27 PCI-MSI-edge eth58-tx-0 78: 1 22 0 5 PCI-MSI-edge eth58-tx-1 79: 1 0 22 5 PCI-MSI-edge eth58-tx-2 80: 23 0 0 5 PCI-MSI-edge eth58-tx-3 81: 187 17 70 7 PCI-MSI-edge snd_hda_intel 82: 698 1647 247 129 PCI-MSI-edge i915 83: 438 135 16 59 PCI-MSI-edge snd_hda_intel NMI: 0 0 0 0 Non-maskable interrupts LOC: 1975 2499 2245 1474 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 132 67 429 91 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1697 2178 1903 1541 Rescheduling interrupts CAL: 561 496 534 567 Function call interrupts TLB: 229 254 170 137 TLB shootdowns TRM: 78 78 78 78 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Comme vous pouvez le voir, toutes les interruptions IO-APIC- * se sont transformées en XT-PIC-XT-PIC, et ces interruptions sont routées uniquement sur CPU0. Les interruptions MSI restent inchangées et vont à tous les CPU0-3.

nolapic

Désactive LAPIC. Les interruptions MSI ne peuvent pas fonctionner sans LAPIC, les E / S APIC ne peuvent pas fonctionner sans LAPIC. Par conséquent, toutes les interruptions des appareils iront au PIC et cela ne fonctionne qu'avec CPU0. Et sans LAPIC, les autres processeurs ne fonctionneront même pas dans le système.

La sortie de / proc / interrupts:

CPU0 0: 6416 XT-PIC-XT-PIC timer 1: 2 XT-PIC-XT-PIC i8042 2: 0 XT-PIC-XT-PIC cascade 3: 5067 XT-PIC-XT-PIC aerdrv, aerdrv, PCIe PME, PCIe PME, i915, snd_hda_intel, eth59 4: 32 XT-PIC-XT-PIC aerdrv, aerdrv, PCIe PME, PCIe PME, eth58 5: 0 XT-PIC-XT-PIC aerdrv, PCIe PME 6: 0 XT-PIC-XT-PIC aerdrv, PCIe PME 8: 1 XT-PIC-XT-PIC rtc0 9: 0 XT-PIC-XT-PIC acpi 11: 274 XT-PIC-XT-PIC snd_hda_intel 12: 202 XT-PIC-XT-PIC ehci_hcd:usb1 15: 7903 XT-PIC-XT-PIC ahci NMI: 0 Non-maskable interrupts LOC: 0 Local timer interrupts SPU: 0 Spurious interrupts PMI: 0 Performance monitoring interrupts IWI: 0 IRQ work interrupts RTR: 0 APIC ICR read retries RES: 0 Rescheduling interrupts CAL: 0 Function call interrupts TLB: 0 TLB shootdowns TRM: 0 Thermal event interrupts THR: 0 Threshold APIC interrupts MCE: 0 Machine check exceptions MCP: 1 Machine check polls ERR: 0 MIS: 0

Combinaisons:

En fait, il n'y en a qu'un pour la nouvelle version: "noapic pci = nomsi". Toutes les interruptions des appareils ne peuvent aller vers CPU0 que via le PIC. Mais LAPIC fonctionne et d'autres processeurs peuvent fonctionner et gérer les interruptions.

Premièrement, parce que vous ne pouvez rien combiner avec «nolapic», parce que cette option rendra I / O APIC et MSI indisponibles. Donc, si vous avez une fois prescrit les options de démarrage «noapic nolapic» (ou l'option la plus courante «acpi = off noapic nolapic»), vous avez apparemment tapé des lettres supplémentaires.

Alors, que se passera-t-il avec les options «noapic pci = nomsi»:

La sortie de / proc / interrupts:

CPU0 CPU1 CPU2 CPU3 0: 5 0 0 0 XT-PIC-XT-PIC timer 1: 2 0 0 0 XT-PIC-XT-PIC i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 3: 5072 0 0 0 XT-PIC-XT-PIC i915, snd_hda_intel, eth59 4: 32 0 0 0 XT-PIC-XT-PIC eth58 8: 1 0 0 0 XT-PIC-XT-PIC rtc0 9: 0 0 0 0 XT-PIC-XT-PIC acpi 11: 281 0 0 0 XT-PIC-XT-PIC snd_hda_intel 12: 200 0 0 0 XT-PIC-XT-PIC ehci_hcd:usb1 15: 7930 0 0 0 XT-PIC-XT-PIC ahci NMI: 0 0 0 0 Non-maskable interrupts LOC: 2595 2387 2129 1697 Local timer interrupts SPU: 0 0 0 0 Spurious interrupts PMI: 0 0 0 0 Performance monitoring interrupts IWI: 159 90 482 135 IRQ work interrupts RTR: 3 0 0 0 APIC ICR read retries RES: 1568 1666 1810 1833 Rescheduling interrupts CAL: 431 556 549 558 Function call interrupts TLB: 124 184 156 274 TLB shootdowns TRM: 116 116 116 116 Thermal event interrupts THR: 0 0 0 0 Threshold APIC interrupts MCE: 0 0 0 0 Machine check exceptions MCP: 2 2 2 2 Machine check polls ERR: 0 MIS: 0

Interrompre les tables de routage et les options «acpi = noirq», «pci = noacpi», «acpi = off»

Comment le système d'exploitation reçoit-il les informations de routage d'interruption des appareils? Le BIOS prépare les informations pour le système d'exploitation sous la forme de:

- Tables ACPI (méthodes _PIC / _PRT)

- Tables _MP_ (MPtable)

- $ Tables PIR

- Enregistre l'espace de configuration du périphérique PCI 0x3C / 0x3D

Il convient de noter que le BIOS n'a rien à faire pour indiquer les interruptions du MSI; toutes les informations ci-dessus sont nécessaires uniquement pour les lignes d'interruption APIC / PIC.

Les tableaux de la liste ci-dessus sont indiqués par ordre de priorité. Examinons-le plus en détail.

Supposons que le BIOS fournisse toutes ces données et que nous démarrions sans aucune option supplémentaire:

- Le système d'exploitation trouve des tables ACPI

- L'OS exécute la méthode ACPI "_PIC", lui transmet l'argument selon lequel il doit être chargé en mode APIC. Ici, le code de méthode enregistre généralement le mode sélectionné dans une variable (disons PICM = 1)

- Pour obtenir des données sur les interruptions, le système d'exploitation appelle la méthode ACPI "_PRT". Il vérifie la variable PICM en interne et renvoie le routage pour le cas APIC

Si nous

démarrons avec l'option

noapic :

- Le système d'exploitation trouve des tables ACPI

- L'OS exécute la méthode ACPI "_PIC", lui transmet l'argument selon lequel il est nécessaire de démarrer en mode PIC. Ici, le code de méthode enregistre généralement le mode sélectionné dans une variable (disons PICM = 0)

- Pour obtenir des données sur les interruptions, le système d'exploitation appelle la méthode ACPI "_PRT". Il vérifie la variable PICM en interne et renvoie le routage pour le cas PIC

Si la table ACPI est manquante ou si la fonctionnalité de routage d'interruption via ACPI est désactivée à l'aide des

options acpi = noirq ou

pci = noacpi (ou si ACPI est complètement désactivé à l'aide d'

acpi = off ), le système d'exploitation recherche la table MPtable (_MP_) pour le routage des interruptions:

- Le système d'exploitation ne trouve pas / ne recherche pas les tables ACPI

- Le système d'exploitation trouve MPtable (_MP_)

Si la table ACPI est manquante ou si la fonctionnalité de routage d'interruption via ACPI est désactivée à l'aide des

options acpi = noirq ou

pci = noacpi (ou ACPI est complètement désactivée à l'aide d'

acpi = off ) et si la table MPtable (_MP_) est manquante (ou si l'option de démarrage

noapic ou

nolapic est

passée ):

- Le système d'exploitation ne trouve / ne voit pas la table ACPI

- Le système d'exploitation ne trouve pas / ne regarde pas la table MPtable (_MP_)

- Le système d'exploitation trouve la table $ PIR

S'il n'y a pas de table $ PIR, ou si elle n'est pas complète, le système d'exploitation pour deviner les interruptions examinera les valeurs des registres 0x3C / 0x3D dans l'espace de configuration des périphériques PCI.

Nous résumons tout ce qui précède avec l'image suivante:

Il ne faut pas oublier que tous les BIOS ne fournissent pas les 3 tables (ACPI / MPtable / $ PIR), donc si vous avez passé l'option au chargeur pour refuser d'utiliser ACPI ou ACPI et MPtable pour le routage des interruptions, c'est loin du fait que votre système démarre.

Remarque 1 : si nous essayons de démarrer en mode APIC avec l'option acpi = noirq et sans la présence de MPtable, l'image des interruptions sera la même que dans le cas d'un démarrage normal avec la seule option noapic. Le système d'exploitation lui-même passera en mode d'interruption PIC.

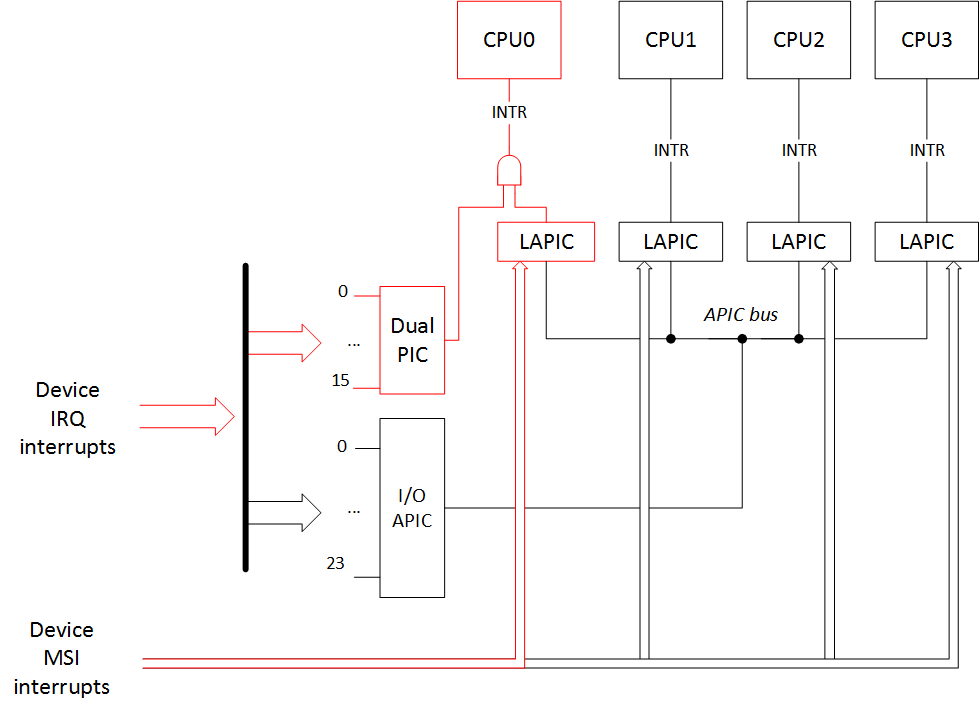

Si nous essayons de démarrer sans tables ACPI (acpi = off) et sans fournir MPtable, l'image sera comme ceci:

CPU0 0: 6 XT-PIC-XT-PIC timer 1: 2 XT-PIC-XT-PIC i8042 2: 0 XT-PIC-XT-PIC cascade 8: 0 XT-PIC-XT-PIC rtc0 12: 373 XT-PIC-XT-PIC ehci_hcd:usb1 16: 0 PCI-MSI-edge PCIe PME 17: 0 PCI-MSI-edge PCIe PME 18: 0 PCI-MSI-edge PCIe PME 19: 0 PCI-MSI-edge PCIe PME 20: 0 PCI-MSI-edge PCIe PME 21: 0 PCI-MSI-edge PCIe PME 22: 8728 PCI-MSI-edge ahci 23: 1 PCI-MSI-edge eth59 24: 1301 PCI-MSI-edge eth59-rx-0 25: 113 PCI-MSI-edge eth59-tx-0 26: 0 PCI-MSI-edge eth58 27: 45 PCI-MSI-edge eth58-rx-0 28: 45 PCI-MSI-edge eth58-tx-0 29: 1280 PCI-MSI-edge snd_hda_intel NMI: 2 Non-maskable interrupts LOC: 24076 Local timer interrupts SPU: 0 Spurious interrupts PMI: 2 Performance monitoring interrupts IWI: 2856 IRQ work interrupts RTR: 0 APIC ICR read retries RES: 0 Rescheduling interrupts CAL: 0 Function call interrupts TLB: 0 TLB shootdowns TRM: 34 Thermal event interrupts THR: 0 Threshold APIC interrupts MCE: 0 Machine check exceptions MCP: 2 Machine check polls ERR: 0 MIS: 0

Cela se produit car sans l'ACPI de la table MADT (

Multiple APIC Description Table ) et les informations nécessaires de MPtable, le système d'exploitation ne connaît pas les identificateurs APIC (APIC ID) pour les autres processeurs et ne peut pas fonctionner avec eux, mais le LAPIC du processeur principal fonctionne. puisque nous n'avons pas interdit cela, et les interruptions MSI peuvent y arriver. Autrement dit, ce sera comme ceci:

Remarque 2

Remarque 2 : en général, le routage d'interruption lors de l'utilisation d'ACPI dans le cas d'APIC est identique au routage d'interruption via MPtable. Et le routage d'interruption ACPI dans le cas de PIC est le même que le routage d'interruption via $ PIR. Les conclusions de / proc / interruptions ne devraient donc pas différer. Cependant, au cours de la recherche, j'ai remarqué une étrangeté. Lors du routage via MPtable, pour une raison quelconque, la sortie contient une interruption en cascade «cascade XT-PIC-XT-PIC».

CPU0 CPU1 CPU2 CPU3 0: 15 0 0 0 IO-APIC-edge timer 1: 2 0 0 0 IO-APIC-edge i8042 2: 0 0 0 0 XT-PIC-XT-PIC cascade 8: 0 1 0 0 IO-APIC-edge rtc0 9: 0 0 0 0 IO-APIC-edge acpi ...

C'est un peu étrange que cela se produise, mais la

documentation du

noyau semble dire que c'est normal.

Conclusion:

En conclusion, nous désignons à nouveau les options analysées.

Options de sélection du contrôleur d'interruption:

- pci = nomsi - Les interruptions MSI deviendront IO-APIC / XT-PIC en fonction du contrôleur d'interruption utilisé

- noapic - Désactive les E / S APIC. Les interruptions MSI peuvent toujours aller à tous les CPU, les autres interruptions des périphériques ne peuvent aller qu'à PIC, et cela ne fonctionne qu'avec CPU0. Mais LAPIC fonctionne et d'autres processeurs peuvent fonctionner et gérer les interruptions

- noapic pci = nomsi - Toutes les interruptions des appareils ne peuvent aller qu'au PIC, et cela ne fonctionne qu'avec CPU0. Mais LAPIC fonctionne et d'autres processeurs peuvent fonctionner et gérer les interruptions

- nolapic - Désactive LAPIC. Les interruptions MSI ne peuvent pas fonctionner sans LAPIC, les E / S APIC ne peuvent pas fonctionner sans LAPIC. Toutes les interruptions des appareils iront au PIC, et cela ne fonctionne qu'avec CPU0. Et sans LAPIC, le reste du CPU ne fonctionnera pas.

Options pour choisir la table de priorité pour le routage d'interruption:

- aucune option - routage via APIC à l'aide des tables ACPI

- noapic - routage via PIC à l'aide de tables ACPI

- acpi = noirq ( pci = noacpi / acpi = off ) - routage via APIC à l'aide de MPtable

- acpi = noirq ( pci = noacpi / acpi = off ) noapic ( nolapic ) - routage via PIC à l'aide de la table $ PIR

Dans la partie suivante, nous verrons comment coreboot configure le chipset pour le routage des interruptions.