Dans les commentaires de mon

article sur le contrôle des LED RVB à l'aide du bloc de microcontrôleur UDB de Cypress PSoC, il a été suggéré qu'il serait bien de dire brièvement au début de l'article ce qu'est l'UDB. Comme je l'ai déjà noté dans l'article, je ne peux pas écrire brièvement sur UDB, mais vous pouvez simplement y transférer la documentation de l'entreprise pour familiariser le lecteur domestique avec un outil aussi puissant pour implémenter les fonctions du firmware.

Mais d'abord, regardons ce qu'est le PSoC. PSoC est une famille de chipsets Cypress pour la mise en œuvre de systèmes sur puce. Différentes familles ont un cœur de processeur différent (pour PSoC 3 c'est MCS-51, pour PSoC 4 c'est Cortex M0, pour PSoC 5LP c'est Cortex M3, et pour PSoC 6 c'est deux à la fois: Cortex M0 + et Cortex M4) et un ensemble de logique programmable. De plus, cette logique n'est pas purement numérique, il y a là des choses analogiques. En plus d'un ensemble de différents ADC, il existe également des commutateurs analogiques. Vous pouvez même connecter les jambes par programmation via des circuits analogiques, cependant, la résistance du circuit sera mesurée en kilogrammes. Il y a des amplificateurs opérationnels à l'intérieur de PSoC qui peuvent être commutés par programme, ce qui signifie que vous pouvez construire différents blocs analogiques sur eux.

Soit dit en passant, les PSoC peuvent être alimentés par n'importe quelle tension de 2,7 à 5,5 volts. Autrement dit, vous n'avez pas besoin de penser à aucun type de stabilisateurs avec alimentation par batterie ou alimentation USB.

Mais j'ai écrit sur les choses analogiques uniquement pour un mot rouge. Maintenant, nous allons nous concentrer sur les choses numériques. La plupart des contrôleurs modernes ont de puissantes unités périphériques qui offrent une grande variété de fonctions. Mais en pratique, dans chaque développement logiciel spécifique, ces blocs ne sont pas pleinement utilisés, mais seulement partiellement. Et dans PSoC, au lieu d'un tas de bonnes, la logique du programme est implémentée, similaire à la logique des FPGA classiques. En conséquence, il est possible d'implémenter exactement les blocs qui sont nécessaires sur celui-ci, en les incluant dans les modes requis. Et les ressources ne doivent pas être dépensées pour des modes inutilisés, les donnant pour la mise en œuvre de certaines choses personnelles.

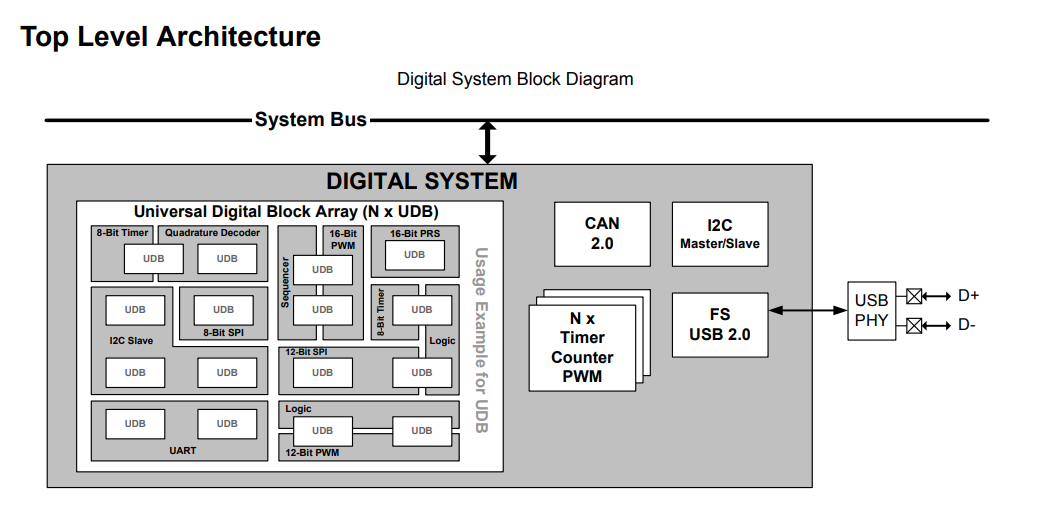

Et ici, un malentendu survient souvent. De nombreux développeurs sont habitués au fait qu'il existe deux types de circuits intégrés logiques programmables (FPGA): CPLD et FPGA. Par conséquent, beaucoup de ceux qui ont entendu parler de PSoC pensent qu'il existe une sorte de boîte CPLD qui peut être programmée dans Veriolg. En fait, oui et non. Un certain nombre de PLD (sans "C", juste des PLD) sont vraiment là, et vous pouvez vraiment les programmer sur Verilog. Mais vraiment, ces PLD font partie des blocs UDB. Et c'est l'UDB qui est l'élément principal de la logique programmable implémentée dans PSoC. Ce bloc est extrêmement original et offre simplement les opportunités les plus larges pour le développeur. Considérez la figure de la documentation propriétaire expliquant l'essence de l'utilisation des blocs UDB.

Puisque j'ai tout étudié en utilisant la famille PSoC 5LP comme exemple, je vais traduire la documentation en elle. Mais avant de commencer, je dirai quelques mots sur le prix de ces contrôleurs. Si vous allez à Ali Express et regardez la planche à pain pour eux, vous obtenez un sentiment triste. Franchement, en comparaison avec STM32-DISCOVERY, ils ne sont toujours rien, mais par rapport aux prototypes STM32F103C8T6, ils sont un peu chers. Tout d'abord, cela est dû au fait que les maquettes d'entreprise ont toujours non pas un, mais deux de ces contrôleurs. Les fonctions JTAG sont implémentées sur le PSoC 5LP, même si le contrôleur cible et le PSoC 4 (ce dernier ne possède généralement pas de port USB).

Mais en divisant le prix par deux, nous obtenons toujours qu'il est supérieur à celui du STM32F103, qui est similaire dans le cœur du processeur. Néanmoins, si nous ajoutons même le CPLD le plus simple à ce même STM32 de l'extérieur, le prix total bénéficiera déjà au PSoC. Et nous ajouterons les jambes perdues à la connexion de ces deux cas (PSoC a toutes les connexions à l'intérieur). Et aussi le prix des centimètres carrés de la planche. Il s'avère donc que si vous devez travailler uniquement avec le cœur du processeur, la PSoC n'est vraiment pas nécessaire. Si vous devez apporter des fonctionnalités au niveau du micrologiciel ou du matériel, vous avez besoin de PSoC. À ce sujet, le système sortira moins cher et plus facile.

En fait, j'ai une idée maniaque d'essayer de faire du support matériel pour le noyau de notre RTOS MAX. Pour ce faire, j'ai étudié la méthodologie de développement des applications Bare Metal pour Altera V SoC (hélas, il s'est avéré que la fonctionnalité d'architecture est telle que le système d'exploitation peut être ralenti, mais vous ne pouvez pas l'accélérer - les requêtes simples adressées au matériel sont accompagnées d'une latence folle). Pour cela, j'ai commencé à maîtriser le PSoC. Je n'ai pas atteint l'overclocking du noyau (il n'y a que des réflexions générales), mais j'ai vraiment aimé l'idée de la programmation UDB. Bien sûr, je suis maintenant intéressé à porter cette idée au maximum de programmeurs nationaux. Par conséquent, nous procédons à la traduction de la partie correspondante de la documentation propriétaire de Cypress sur UDB. La numérotation des chapitres et des figures est conservée conformément au document d'origine.

Le contenu général du cycle «UDB. Qu'est-ce que c'est? "

Partie 1. Introduction. Pld. (Article actuel)

Partie 2. Chemin de données.Partie 3. Datapath FIFO.Partie 4. Datapath ALU.Partie 5. Chemin de données. Petites choses utiles.Partie 6. Module de gestion et d'état.Partie 7. Module de commande de temporisation et de réinitialisationPartie 8. Adressage UDBUDB. Qu'est-ce que c'est? Partie 1

21. Blocs numériques universels

Dans ce chapitre, nous verrons comment les blocs numériques universels (UDB) permettent le développement de fonctions périphériques numériques programmables. L'architecture UDB établit un équilibre entre la granularité de la configuration et une mise en œuvre efficace. Les UDB sont constitués d'une combinaison de logique non commutée similaire à une matrice logique programmable (PLM, PLD anglais), de logique structurée (machines opérationnelles, ci-après dénommées Datapath) et d'un schéma de traçage flexible.

21.1 Caractéristiques

- Pour une flexibilité optimale, chaque UDB contient les composants suivants:

• Chemin de données 8 bits basé sur ALU (Arithmetic and Logic Unit, ALU) avec référentiel d'instructions à 8 instructions, plusieurs registres et tampons FIFO;

• deux PLD, chacun ayant 12 entrées, huit termes conjonctifs (termes du produit, PT) et quatre sorties macrocellulaires;

• registres de gestion et de statut;

• modules d'horloge et de réinitialisation. - PSoC 5LP contient une baie jusqu'à 24 UDB.

- Traçage flexible entre les éléments du tableau UDB.

- Les éléments UDB peuvent être divisés ou chaînés pour créer des fonctions plus importantes.

- Implémentation flexible d'un certain nombre de fonctions numériques, y compris les temporisateurs, les compteurs, les modulateurs de largeur d'impulsion (y compris PWM avec un générateur de bande morte), UART, bus I2C, bus SPI et vérification / génération CRC.

21.2 Schéma fonctionnel

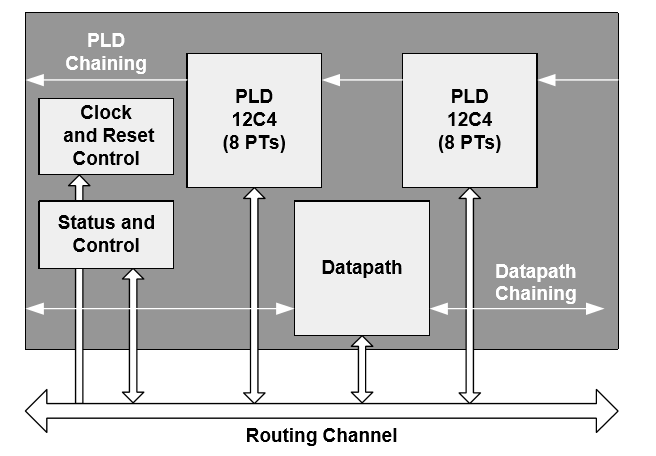

La figure 21-1 montre l'UDB en tant que construction contenant deux blocs logiques de base, PLD, Datapath et les fonctions de contrôle, d'état, d'horloge et de réinitialisation.

Figure 21-1. Schéma fonctionnel de l'UDB.

Figure 21-1. Schéma fonctionnel de l'UDB.21.3 Comment ça marche

Les principaux composants de l'UDB sont:

- PLD (2). Les données des ressources de trace sont transmises aux entrées de ces blocs. Ils implémentent la logique combinatoire et l'alignement des données, ce qui vous permet d'implémenter des machines à états finis, de contrôler les opérations du bloc Datapath, de configurer les conditions d'entrée et de contrôler les sorties.

- Datapath. Ce bloc contient ALU dynamiquement programmable, quatre registres, deux tampons FIFO, des comparateurs et la génération de conditions.

- Gestion et statut (Statut et contrôle). Ces modules fournissent un mécanisme pour l'interaction des microprogrammes du processeur central (CPU) et la synchronisation avec les opérations UDB. Les registres de contrôle agissent sur les éléments internes et les registres d'état lisent l'état des éléments externes.

- Horloge et contrôle de réinitialisation Ces modules permettent la sélection et l'activation de la synchronisation, ainsi que la réinitialisation de la sélection dans UDB.

- Chaînage des signaux. PLD et Datapath ont des signaux qui vous permettent de chaîner des blocs adjacents dans une chaîne pour créer des fonctions de bits supérieurs.

- Canal de traçage Les UDB sont connectés au canal de trace via des matrices de commutation programmables pour la communication entre les blocs au sein du même UDB et pour la communication avec les autres UDB de la matrice.

- Interface de bus système (interface de bus Sysytem). Tous les registres et la RAM de chaque UDB sont projetés sur l'espace d'adressage du système et leur accès peut être obtenu à l'aide du processeur central ou via un accès direct à la mémoire (English Direct Memory Access, DMA) sous la forme de 8 bits et 16 bits. les données.

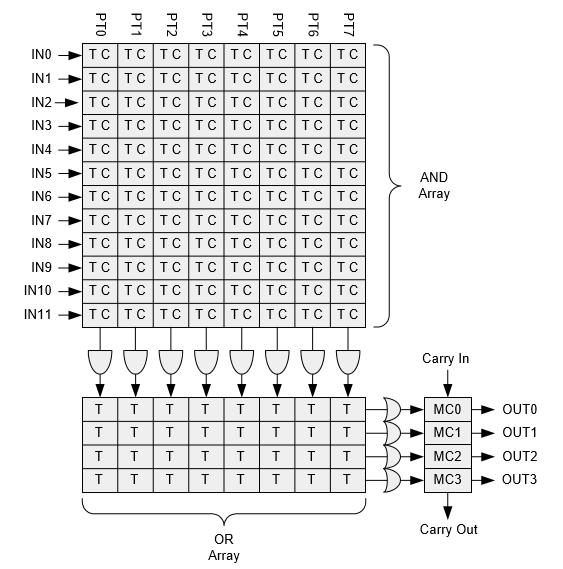

21.3.1. Pld

Chaque UDB possède deux PLD 12C4. Les blocs PLD illustrés à la figure 21-1 peuvent être utilisés pour implémenter des machines à états, traiter les données d'E / S et créer une logique de table (Eng. Lookup Table, LUT). De plus, PLD peut être configuré pour exécuter des fonctions arithmétiques, définir la séquence de chemin de données et générer un état. La logique générale peut être synthétisée et projetée sur des blocs PLD. Cette section fournit une vue d'ensemble de l'architecture PLD.

PLD dispose de 12 entrées qui transmettent des informations en 8 termes conjonctifs dans un tableau ET. Dans chaque terme conjonctif, vous pouvez choisir une entrée directe (vraie, T) ou inverse (complément, C). La sortie des termes conjonctifs va à l'entrée du tableau OU. La lettre «C» dans 12C4 indique que les termes OU sont constants pour toutes les entrées, et chaque entrée OU peut obtenir un accès programmatique à n'importe quel terme conjonctif. Cette structure offre une flexibilité maximale et garantit que toutes les entrées et sorties peuvent être déplacées.

Figure 21-2. La structure du PLD 12C4.

Figure 21-2. La structure du PLD 12C4.21.3.1.1 Macro PLD

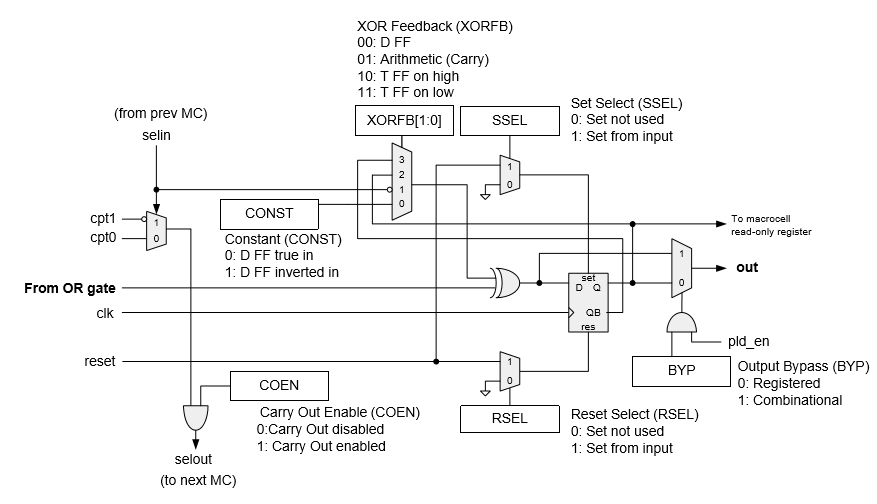

L'architecture des macrocellules est illustrée à la figure 21-3. La sortie contrôle le tableau de trace et peut être verrouillée ou Raman. Pour le verrouillage, un déclencheur D avec entrée directe ou inverse ou un déclencheur T avec un niveau d'entrée haut ou bas est utilisé. Le déclencheur de sortie peut être réglé ou réinitialisé pendant l'initialisation ou de manière asynchrone pendant le fonctionnement normal, par un signal externe provenant du canal de trace.

Figure 21-3. Architecture macrocellulaire.Registre de macro-cellules PLD en lecture seule

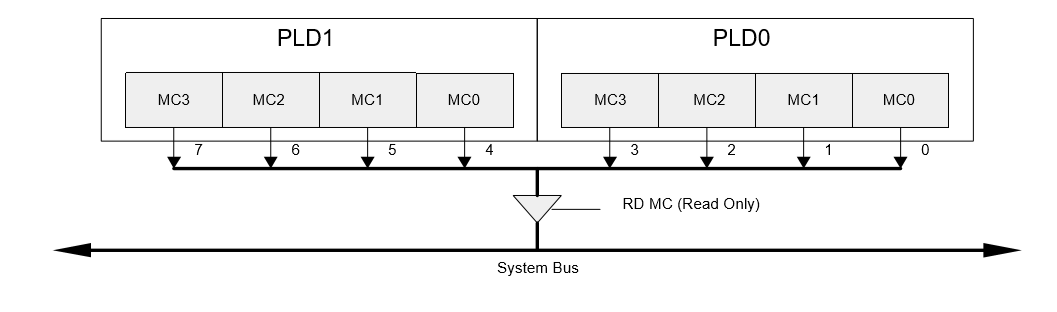

Figure 21-3. Architecture macrocellulaire.Registre de macro-cellules PLD en lecture seuleEn plus de contrôler le réseau de traces, les sorties de macrocellules des deux PLD sont projetées sur l'espace d'adressage sous la forme d'un registre en lecture seule de 8 bits, auquel on peut accéder à l'aide du CPU ou du DMA.

Figure 21-4. Registre de macrocellules PLD en lecture seule.

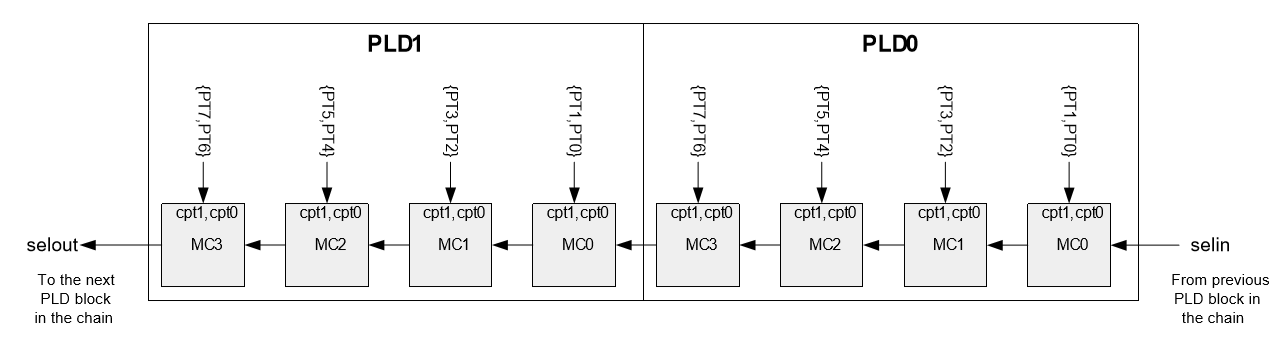

Figure 21-4. Registre de macrocellules PLD en lecture seule.21.3.1.2 Chaîne de césure PLD

Les PLD sont liés ensemble dans l'adressage UDB. Comme le montre la figure 21-5, l'entrée de la chaîne de transport Selin est transmise de l'UDB précédente au circuit, via chaque macro-cellule dans les deux PLD, puis elle est transmise à l'UDB suivante en tant que sortie de la chaîne de transport Selout. Pour soutenir le placement efficace des fonctions arithmétiques, des termes conjonctifs spéciaux (PT) sont générés, qui sont utilisés dans les macrocellules avec une chaîne de césure.

Figure 21-5. Chaîne de césure PLD et entrées de termes conjonctifs spéciaux.

Figure 21-5. Chaîne de césure PLD et entrées de termes conjonctifs spéciaux.21.3.1.3 Configuration PLD

Chaque PLD apparaît devant le CPU ou le DMA sous forme de RAM avec accès 16 bits. La matrice ET a 12 × 8 × 2 bits ou 24 octets pour la programmation, et la matrice OU a 4 × 8 bits ou 4 octets pour la programmation. De plus, chaque macro-cellule possède un octet de configuration, totalisant 32 octets de configuration par PLD. Étant donné que chaque UDB possède 2 PLD, la configuration totale de chaque UDB est de 64 octets.

La prochaine fois, nous considérerons les automates opérationnels (chemins de données).