Nous continuons à traduire la documentation propriétaire de Cypress en blocs UDB. De plus, tout coïncide très bien. Pour continuer l'

article pratique sur UDB, vous devrez utiliser FIFO, et dans la partie théorique, nous en sommes arrivés à la description même. Par conséquent, nous commençons à les étudier en détail.

Le contenu général du cycle «UDB. Qu'est-ce que c'est? "

Partie 1. Introduction. Pld.Partie 2. Chemin de données.Partie 3. Datapath FIFO. (Article actuel)

Partie 4. Datapath ALU.Partie 5. Chemin de données. Petites choses utiles.Partie 6. Module de gestion et d'état.Partie 7. Module de commande de temporisation et de réinitialisationPartie 8. Adressage UDB21.3.2.2 FIFO de chemin de données

Modes et configurations FIFO

Chaque tampon FIFO a plusieurs modes de fonctionnement et configurations disponibles:

Tableau 21-2. Modes et configurations FIFO.

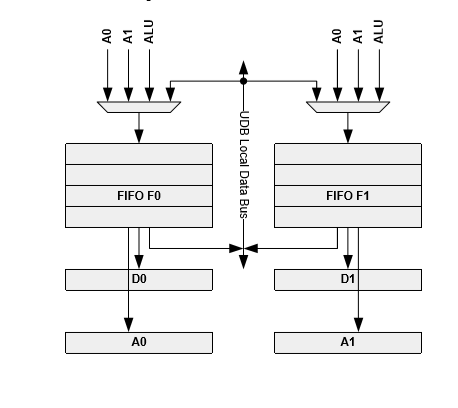

La figure 21-7 montre les options de configuration possibles pour la paire FIFO, selon les modes d'entrée / sortie sélectionnés pour chacun d'eux. Si un FIFO est en mode d'entrée et l'autre en mode de sortie, nous obtenons la configuration RX / TX. Un exemple typique où une telle configuration est nécessaire est le contrôleur de bus SPI. La configuration

Dual Capture (les deux FIFO sont configurés pour la sortie) permet une capture indépendante des paires A0 et A1 ou deux captures indépendantes des registres A0 ou A1. Enfin, en mode

Dual Buffer (tous deux en entrée), il est possible d'utiliser soit une paire de registres soit deux registres indépendants pour charger ou comparer.

Figure 21-7. Configurations FIFO.

La figure 21-8 montre en détail les sources et les récepteurs pour FIFO.

Figure 21-8. Sources et récepteurs FIFO.

Lorsque FIFO fonctionne en mode tampon d'entrée, la source est le bus système et les récepteurs sont les registres Dx et Ax. Lorsque vous travaillez en mode tampon de sortie, les sources sont les registres Ax et ALU, et le récepteur est le bus système. La sélection du multiplexeur est définie statiquement dans le registre de configuration UDB CFG15, comme indiqué dans le tableau pour F0_INSEL [1: 0] ou F1_INSEL [1: 0]:

Tableau 21-3. Un ensemble de multiplexeurs FIFO dans le registre de configuration UDB.

Statut FIFO

Chaque FIFO génère deux signaux d'état, «bus» et «bloc», qui sont transmis aux ressources de trace UDB via le multiplexeur de sortie Datapath. L'état du bus peut être utilisé pour interrompre ou demander une lecture / écriture DMA au FIFO. L'état «bloc» est principalement destiné à transmettre l'état FIFO aux entités UDB internes. la fonction des bits d'état dépend de la direction configurée (Fx_INSEL [1: 0]) et des bits de niveau FIFO. Les bits de niveau FIFO (Fx_LVL) sont définis dans le registre de commande auxiliaire dans l'espace de registre de travail. Les options d'état sont présentées dans le tableau suivant:

Tableau 21-4. Options d'état FIFO.

Illustration de travail FIFO

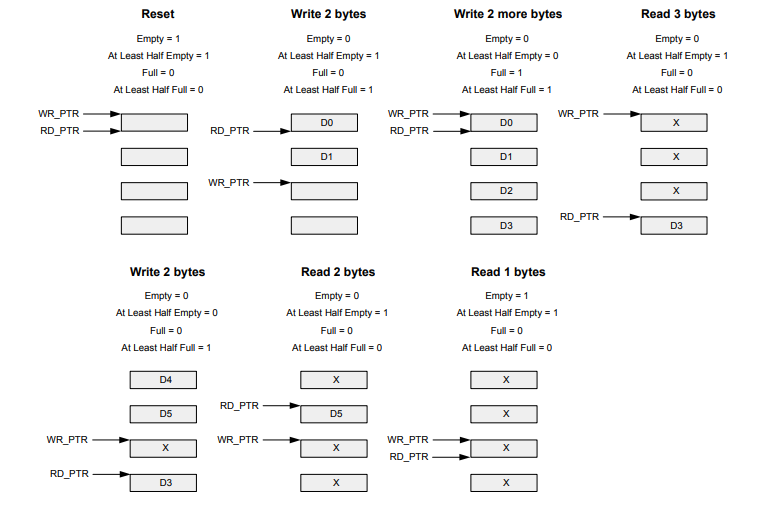

La figure 21-9 montre une séquence typique de lecture et d'écriture, ainsi que la génération de statuts associés à ces opérations. Dans la figure, la lecture et l'écriture se produisent à des moments différents, mais elles peuvent être effectuées simultanément.

Figure 21-9 Fonctionnement des récepteurs FIFO.

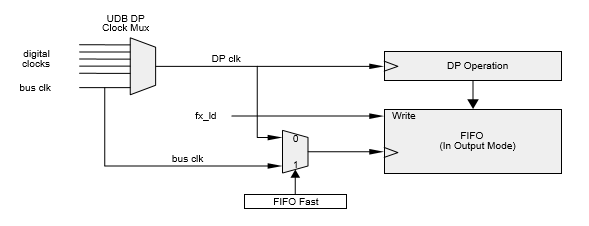

Mode rapide FIFO (FIFO RAPIDE)

Lorsque FIFO est en mode tampon de sortie, l'opération de démarrage FIFO utilise généralement la fréquence d'horloge du chemin de données sélectionné pour cadencer le signal d'écriture. Comme le montre la figure 21-10, lorsque vous sélectionnez le mode rapide FIFO (FIFO FAST), vous pouvez sélectionner la fréquence du bus pour cette opération particulière. Lorsqu'elle est utilisée en conjonction avec le mode

Level / Edge = Edge , cette opération réduit le délai de transmission de la batterie au FIFO de la période d'horloge Datapath à la période d'horloge du bus, car la fréquence du bus peut être beaucoup plus élevée. Cela permet au CPU ou au DMA de lire le résultat FIFO reçu avec un délai minimal.

Comme le montre la figure 21-10, l'opération de démarrage rapide est effectuée quelle que soit l'horloge actuelle du chemin de données, cependant, l'utilisation de la vitesse d'horloge du bus peut augmenter la consommation d'énergie.

Figure 21-10. Récepteurs FIFO à configuration rapide.

Mode d'enregistrement de bord / niveau FIFO (différentiel / niveau)

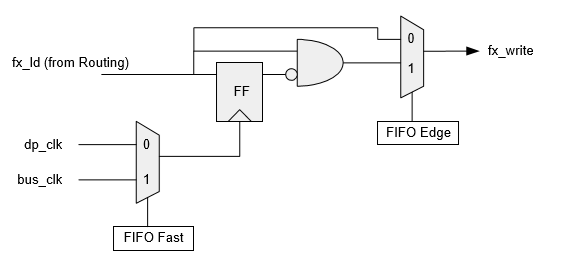

Il existe deux modes d'enregistrement dans FIFO de Datapath. Dans le premier mode, les données sont transférées de manière synchrone des batteries au FIFO. Le signal de commande de cet enregistrement (FX_LD) est généralement généré par une machine d'état ou par une condition synchronisée avec la synchronisation Datapath. L'écriture dans FIFO sera effectuée dans tout cycle au cours duquel le signal de commande de charge d'entrée est «1». Dans le deuxième mode, FIFO est utilisé pour capturer les valeurs de batterie en réponse à un front positif du signal FX_LD. Dans ce mode, le format du signal du signal est arbitraire (cependant, sa période doit être égale à au moins un cycle d'horloge Datapath). Un exemple de ce mode capture la valeur de la batterie en utilisant l'entrée du pied externe comme déclencheur. Une limitation de ce mode est que le paramètre d'entrée doit revenir à la valeur «0» au moins un cycle avant qu'une autre différence positive soit détectée.

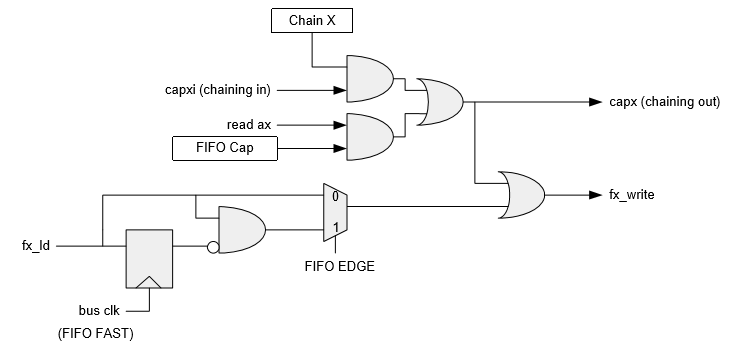

La figure 21-11 montre l'implémentation du mode de détection différentielle à l'entrée FX_LD. Le mode des deux FIFO dans UDB est contrôlé par le même bit, basculant cette option. Notez que la détection différentielle est cadencée à une fréquence égale à la fréquence du FIFO sélectionné.

Figure 21-11. Détection différentielle pour les récepteurs d'enregistrement FIFO internes.

Mode de capture du logiciel FIFO

Une exigence courante et importante est de permettre au CPU et au DMA de lire de manière fiable le contenu de la batterie pendant le fonctionnement normal. Cela se fait à l'aide de la capture logicielle et est activé à l'aide du bit de configuration FIFO Cap. Ce bit s'applique aux deux FIFO dans UDB, mais ne fonctionne que lorsque le FIFO est en mode tampon de sortie. Lorsque vous utilisez la capture logicielle, F0 doit lire depuis A0 et F1 depuis A1.

Comme le montre la figure 21-12, la lecture de la batterie lance l'écriture sur le FIFO à partir de la batterie. Le signal est lié dans une chaîne de sorte que la lecture d'un octet spécifique capture simultanément les valeurs de batterie de tous les UDB de la chaîne. Cela permet au processeur 8 bits de lire avec succès 16 bits ou plus en même temps. Les données renvoyées lors de la lecture de la batterie doivent être ignorées et la valeur capturée peut être immédiatement lue depuis FIFO.

Le signal FX_LD tracé, qui génère la charge FIFO, est envoyé au terme OR avec le signal de capture de programme. Lorsque la capture matérielle et logicielle est utilisée en même temps, le résultat peut être imprévisible. En règle générale, ces fonctions doivent s'exclure mutuellement, cependant, la capture matérielle et logicielle peut être utilisée simultanément dans les conditions suivantes:

- Le mode d'horloge de capture FIFO est réglé sur FIFO FAST.

- Le mode d'enregistrement FIFO est réglé sur FIFO EDGE.

Dans les conditions décrites ci-dessus, les captures matérielles et logicielles fonctionnent essentiellement de la même manière et pendant tout cycle d'horloge de bus, n'importe lequel de ces signaux peut déclencher une capture.

Il est également recommandé d'effacer le FIFO cible dans le code de programme (registre ACTL) avant le début de la capture du programme. Grâce à cela, les pointeurs de lecture et d'écriture FIFO seront mis dans un état connu.

Figure 21-12. Configuration de la capture de logiciels.

Note du traducteur:

Pendant longtemps, je n'ai pas pu comprendre le sens de cette section. Ensuite, pendant longtemps, j'étais sûr que la section était écrite pour PSoC3, dont le cœur à huit bits ne peut pas accéder à plus d'un octet. Mais lors de la création de la huitième partie de la traduction , il s'est avéré que même dans PSoC5LP, pour tous les cœurs de processeur ARM 32 bits, l'accès aux registres UDB fonctionnants peut être effectué en mode huit ou seize bits. A en juger par le document, pas plus. C'est là que les fonctionnalités décrites sont utiles.

Bits de contrôle FIFO

Le registre de contrôle auxiliaire, qui peut être utilisé pour contrôler FIFO pendant le fonctionnement normal, contient 4 bits.

Les bits FIFO0 CLR et FIFO1 CLR sont utilisés pour réinitialiser ou effacer les FIFO. Lorsque l'un de ces bits reçoit la valeur "1", la FIFO associée est réinitialisée. Le bit doit être restauré à sa valeur d'origine ('0') pour que FIFO continue de fonctionner. Si la valeur du bit reste égale à un, le FIFO correspondant sera désactivé et fonctionnera comme un tampon à un octet sans état. Les données peuvent être écrites sur FIFO, les données sont immédiatement lisibles et peuvent être écrasées à tout moment. La direction des données avec les bits de configuration FX INSEL [1: 0] peut toujours être définie.

Les bits FIFO0 LVL et FIFO1 LVL déterminent le niveau auquel FIFO armera le bit d'état

"bus" (lorsque le bus lit ou écrit dans FIFO). C'est-à-dire que l'état de l'état

«bus» dépend de la direction donnée, comme indiqué dans le tableau ci-dessous.

Tableau 21-5. Bits de contrôle de niveau FIFO

Fonctionnement asynchrone FIFO

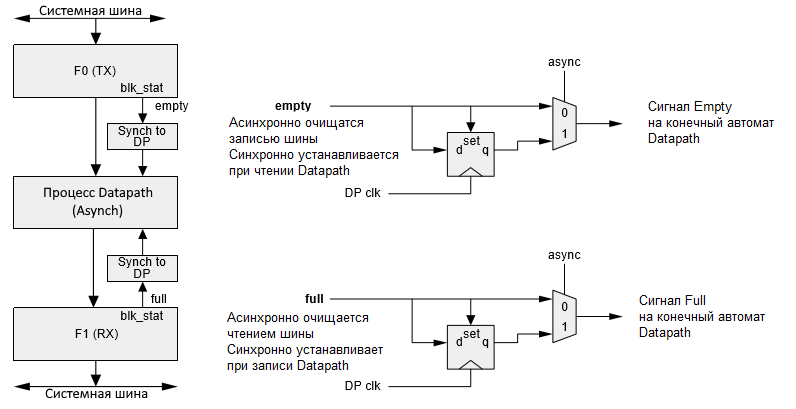

La figure 21-13 illustre le principe du fonctionnement FIFO asynchrone. Par exemple, imaginez que F0 fonctionne en mode tampon d'entrée et F1 en mode tampon de sortie, qui est une configuration typique des registres TX et RX.

Figure 21-13. Fonctionnement FIFO asynchrone.

Côté TX, la machine d'état Datapath utilise l'indicateur

Empty pour déterminer s'il y a des octets disponibles pour la réception. La valeur

Empty est définie de manière synchrone avec la machine d'état Datapath et est effacée de manière asynchrone en raison de l'écriture à partir du bus. Après le nettoyage, l'état est à nouveau synchronisé avec la machine d'état Datapath.

Du côté RX, la machine d'état RX utilise

Full pour déterminer s'il y a de l'espace libre pour écrire dans le FIFO. La valeur

Full est définie de manière synchrone avec la machine d'état Datapath et est effacée de manière asynchrone en raison de la lecture par le bus. Après le nettoyage, l'état est à nouveau synchronisé avec la machine d'état Datapath.

Un bit FIFO ASYNCH est utilisé pour activer cette méthode de synchronisation, après activation, cette méthode est appliquée aux deux FIFO.

Il s'applique uniquement à l'état de

bloc , car il est supposé que l'état du

bus est naturellement synchronisé par le processus d'interruption.

Tableau 21-6.

Bloquer les options de synchronisation d'état FIFO.

Débordement FIFO pendant le fonctionnement

Pour une mise en œuvre sûre des opérations de lecture et d'écriture internes (Datapath) et externes (CPU ou DMA), des signaux d'état FIFO doivent être utilisés. Il n'y a pas de protection intégrée contre les conditions de vidange et de débordement. Si la FIFO est pleine et que des opérations d'écriture ultérieures sont effectuées (débordement), les nouvelles données écrasent le début de la FIFO (les données en cours de sortie sont les suivantes dans la file d'attente de lecture). Si la FIFO est vide et que des lectures ultérieures sont effectuées (vidage ou épuisement), la valeur de lecture n'est pas définie. Les pointeurs FIFO restent précis indépendamment du débordement et du débordement.

Inversion d'horloge FIFO

Chaque FIFO a un bit de contrôle Fx CK INV, qui est responsable de la polarité de l'horloge FIFO en ce qui concerne la polarité de l'horloge Datapath. Par défaut, FIFO fonctionne avec la même polarité que le pointage Datapath. Lorsque ce bit est à 1, FIFO fonctionne avec une polarité inversée par rapport à Datapath. Cela fournit un support de protocole pour l'échange de données sur les deux fronts, comme SPI.

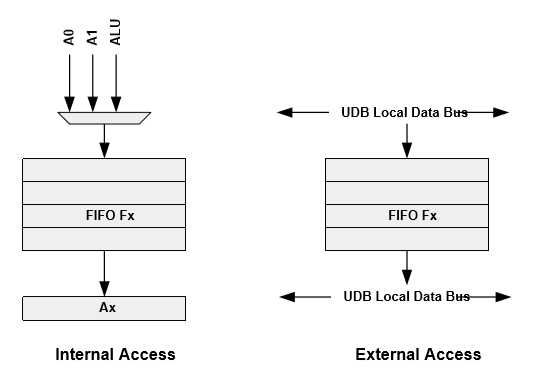

Contrôle FIFO dynamique

En règle générale, les FIFO sont configurés statiquement soit en mode tampon d'entrée, soit en mode tampon de sortie. Alternativement, chaque FIFO peut être configuré pour fonctionner dans un mode dans lequel la direction est contrôlée dynamiquement (sous l'influence de signaux externes). Un bit de configuration par FIFO (Fx DYN) est responsable de l'activation de ce mode. La figure 21-14 montre les configurations disponibles en mode dynamique FIFO.

Figure 21-14. Mode FIFO dynamique.

En mode d'accès interne, Datapath peut lire et écrire sur FIFO. Dans cette configuration, afin de sélectionner la source des opérations d'écriture en FIFO, les bits Fx INSEL doivent être définis sur 1. Fx INSEL = 0 (source de bus CPU) dans ce mode est incorrect, il ne peut prendre que les valeurs 1, 2 ou 3 (A0, A1 ou ALU ) Il est à noter que la lecture n'a accès qu'à la batterie appropriée, la direction des registres de données dans ce mode n'est pas disponible.

En mode d'accès externe, le CPU ou le DMA peut lire ou écrire sur FIFO.

La configuration bascule dynamiquement entre l'accès externe et interne en transmettant les signaux de Datapath. Pour cela, les signaux d'entrée Datapath d0_load et d1_load sont utilisés. Il convient de noter qu'en mode de commande dynamique, d0_load et d1_load ne sont pas disponibles pour leur utilisation normale lors du chargement des registres D0 / D1 à partir de F0 / F1. Les signaux Dx_load peuvent être déclenchés par n'importe quel signal de trace, y compris les constantes.

Prenons un exemple dans lequel, en commençant par un accès externe (dx_load == 1), le CPU ou le DMA peut écrire un ou plusieurs octets de données dans le FIFO. Ensuite, lors du passage à l'accès interne (dx_load == 0), Datapath peut effectuer des opérations sur les données. Après cela, lors du passage à un accès externe, le CPU ou le DMA peut lire le résultat des calculs.

Étant donné que Fx INSEL doit toujours être 01, 10 ou 11 (A0, A1 ou ALU), ce qui correspond au «mode tampon de sortie» pendant le fonctionnement normal, les signaux d'état FIFO ont les définitions suivantes (selon le paramètre Fx LVL):

Tableau 21-7. Statut FIFO.

Étant donné que Datapath et le CPU peuvent écrire et lire à partir de FIFO, ces signaux ne sont plus considérés comme des états de bloc et de bus. Le signal blk_stat est utilisé pour l'état d'écriture et le signal bus_stat pour l'état de lecture

21.3.2.3 Statut FIFO

Il existe quatre signaux d'état FIFO, deux pour chaque FIFO: fifo0_bus_stat, fifo0_blk_stat, fifo1_bus_stat et fifo1_blk_stat. La signification de ces signaux dépend de la direction de la FIFO particulière, qui est déterminée par la configuration statique. L'état FIFO est décrit en détail dans la section

21.3.2.2 FIFO de chemin de données .

Dans la partie suivante, nous allons passer à l'analyse de l'unité logique arithmétique (ALU).