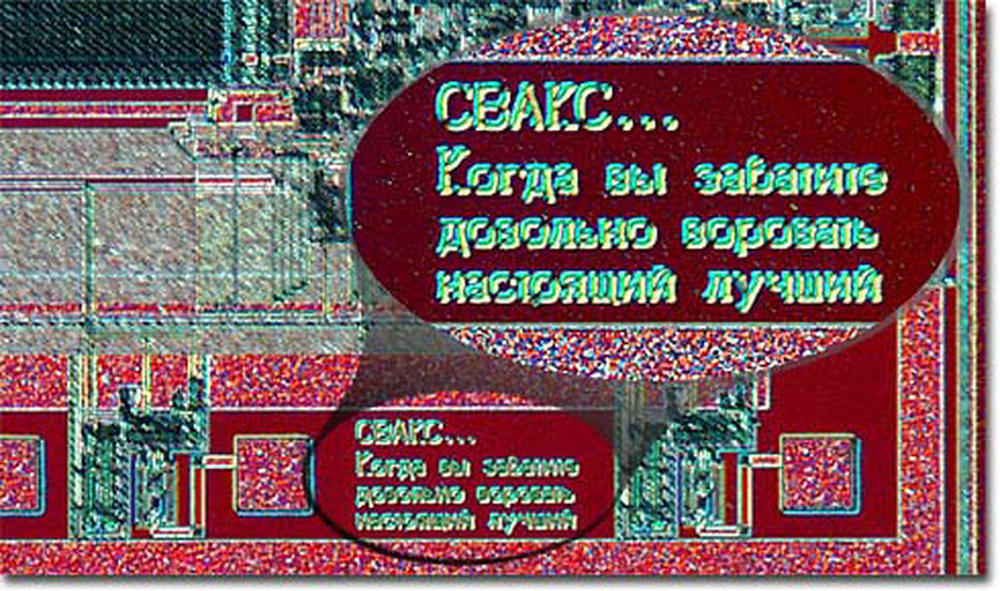

"CVAX - quand vous obtenez vraiment voler le meilleur."

"CVAX - quand vous obtenez vraiment voler le meilleur."L'inscription laissée par des ingénieurs américains à des collègues soviétiques dans la topologie des microprocesseurs.

L'ingénierie inverse des puces électroniques est un casse-tête pour les fabricants dès les premières années de l'existence de la microélectronique. Toute l'électronique soviétique à un moment donné a été construite dessus, et maintenant ils font à peu près la même chose dans l'Empire céleste, et pas seulement à l'intérieur, à une échelle beaucoup plus grande. En fait, la rétro-ingénierie est absolument légale aux États-Unis, dans l'Union européenne et dans de nombreux autres endroits, dans le but (je cite le droit américain) «d'enseigner, d'analyser ou d'évaluer les concepts ou les techniques utilisés dans le travail du masque ou les circuits».

Les utilisations légales les plus courantes de la rétro-ingénierie sont les tribunaux des brevets et des licences. L'espionnage industriel est également courant, d'autant plus que les circuits électriques (en particulier les circuits analogiques) sont souvent la propriété intellectuelle clé et rarement brevetés - juste pour éviter la divulgation de la propriété intellectuelle et la participation aux tribunaux des brevets en tant qu'accusateur. Bien sûr, dans une situation où vous devez protéger votre propriété intellectuelle sans la breveter, les développeurs et les fabricants tentent de trouver des moyens d'empêcher la copie de leurs développements.

Un autre domaine non moins (ou même plus) important de protection des micropuces contre la rétro-ingénierie est d'assurer la sécurité des informations stockées en mémoire. Ces informations peuvent être à la fois un micrologiciel FPGA (qui est, encore une fois, la propriété intellectuelle du développeur) et, par exemple, un code PIN d'une carte bancaire ou une clé de cryptage pour un lecteur flash sécurisé. Plus nous faisons confiance au monde qui nous entoure, plus il est important de protéger ces informations à tous les niveaux des systèmes de traitement, et le niveau matériel ne fait pas exception.

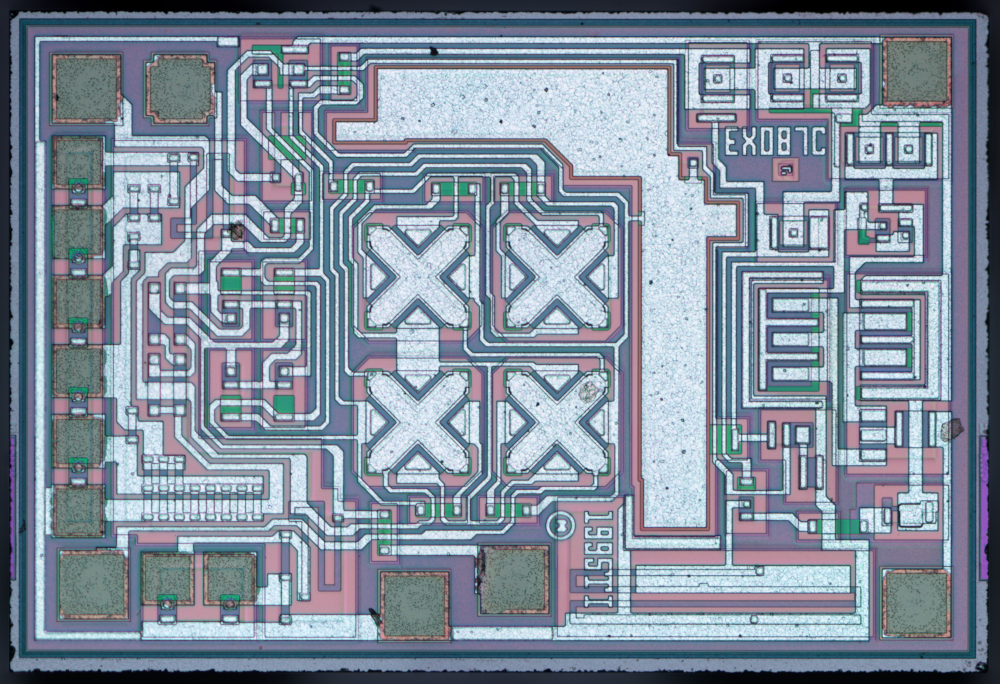

Tout d'abord: une chose importante à comprendre. En ce qui concerne à la fois l'ingénierie inverse et la protection contre la copie de données, vous devez comprendre qu'il n'existe pas de méthodes de protection absolument stables, et tout ce qui est réel est de rendre le processus si long et / ou coûteux qu'il devient économiquement inopportun.Il y a de nombreuses années, le travail d'un ingénieur inversé ou d'un pirate microélectronique était beaucoup plus facile que maintenant. Regardez, par exemple, cette image (merci à

BarsMonster pour notre enfance heureuse et de bonnes photos): avec une compréhension de base de la technologie, en restaurer un circuit électrique est une question de plusieurs heures.

Figure 2. Un instantané de la topologie de l'ampli-op OPA134PA. Source - zeptobars.comIci , en passant, il y a un exemple de rétro-ingénierie de la puce TL431 faite par Ken Shirriff à partir de photographies de BarsMonster. Et voici la traduction russe. Le blog de Ken a beaucoup de trucs sympas si vous êtes intéressé par le sujet de la rétro-ingénierie amateur.Et voici (attentivement, le trafic!) Voici un rapport de l'ingénierie inverse de la puce Zilog Z80-CTC, faite en 1979, presque immédiatement après la sortie de la puce. Maintenant, c'est un document historique unique, et puis ce sont des informations qui ont eu une énorme valeur commerciale et obtenues (à en juger par plusieurs références aux normes militaires), probablement en cours de certification d'un microcircuit pour des applications spéciales.

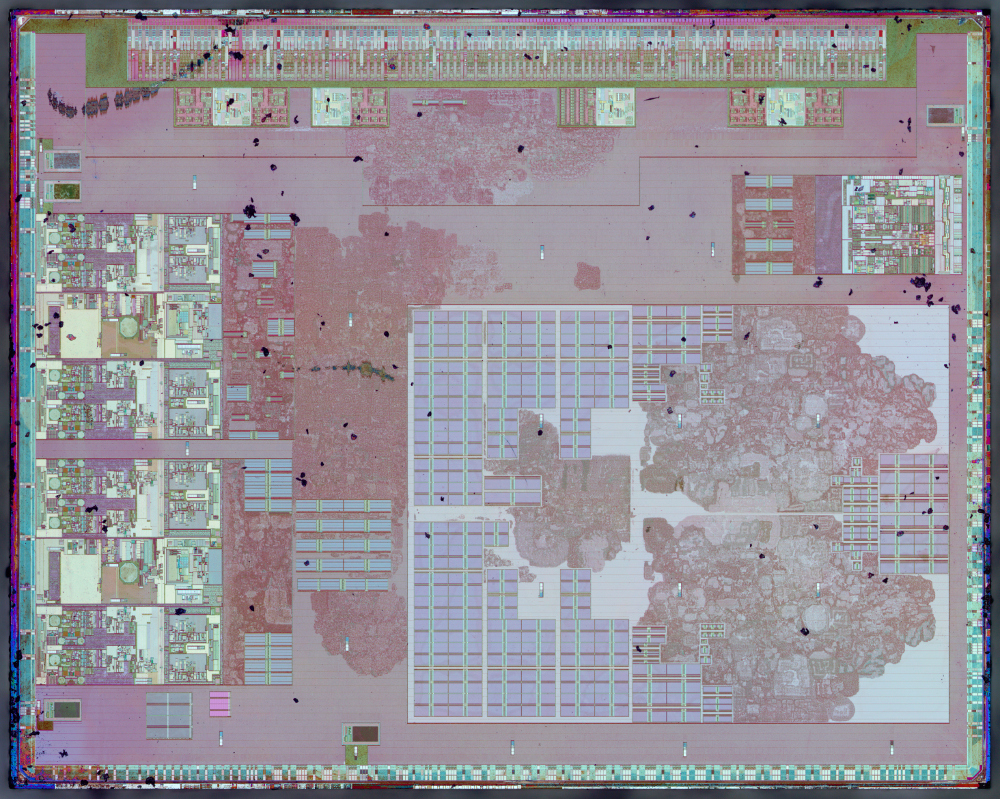

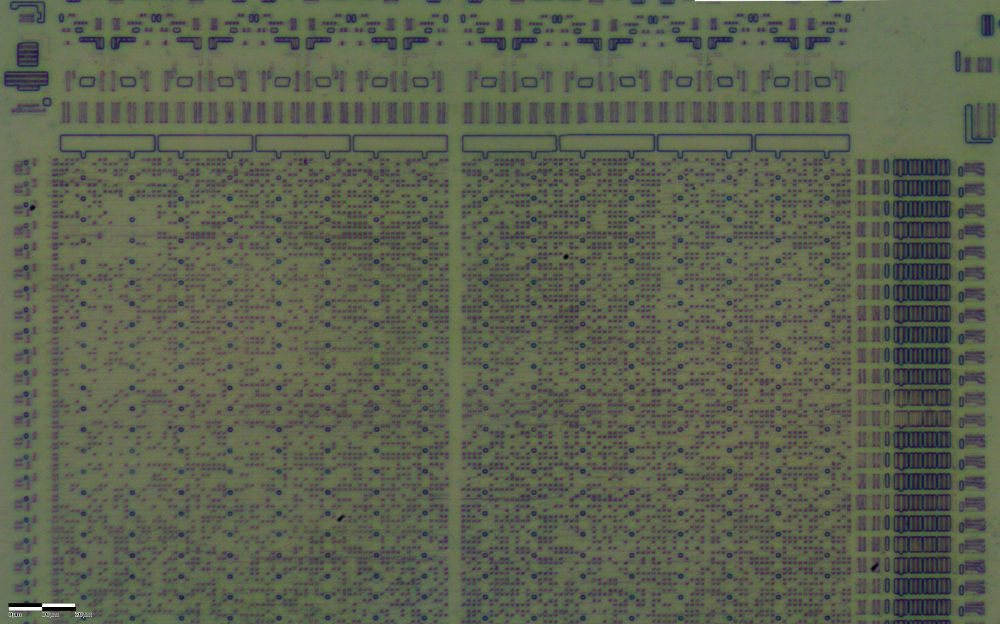

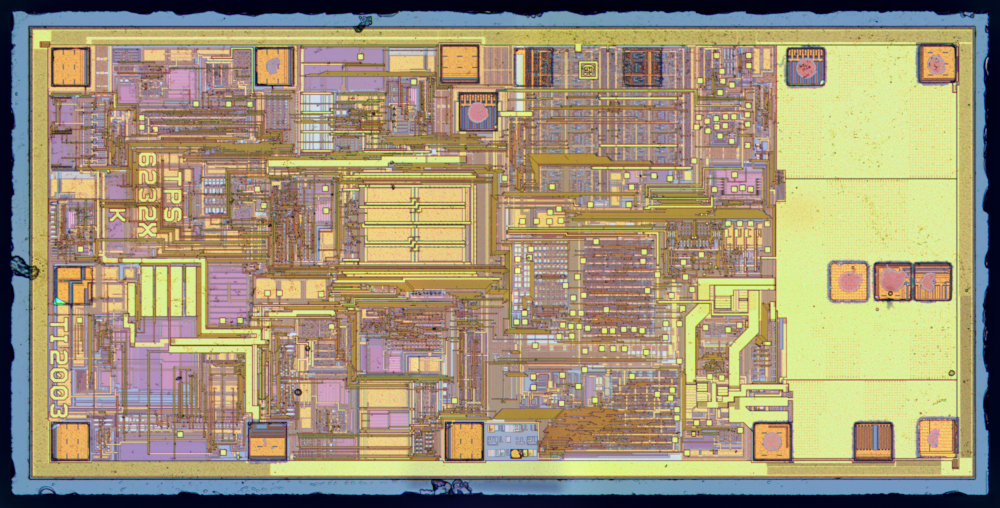

Figure 2. Un instantané de la topologie de l'ampli-op OPA134PA. Source - zeptobars.comIci , en passant, il y a un exemple de rétro-ingénierie de la puce TL431 faite par Ken Shirriff à partir de photographies de BarsMonster. Et voici la traduction russe. Le blog de Ken a beaucoup de trucs sympas si vous êtes intéressé par le sujet de la rétro-ingénierie amateur.Et voici (attentivement, le trafic!) Voici un rapport de l'ingénierie inverse de la puce Zilog Z80-CTC, faite en 1979, presque immédiatement après la sortie de la puce. Maintenant, c'est un document historique unique, et puis ce sont des informations qui ont eu une énorme valeur commerciale et obtenues (à en juger par plusieurs références aux normes militaires), probablement en cours de certification d'un microcircuit pour des applications spéciales.Mais nous vivons en 2019, et non en 1979, et inverser maintenant le schéma complet d'un nouveau microprocesseur Intel est une question de plusieurs mois ou années, même avec un bon niveau d'automatisation du processus (sans parler du fait que même la suppression de la topologie avec les normes de conception dans une résolution acceptable 14 -10-7 nm est une tâche très difficile). Qu'est-ce qu'Intel? Comparez la quantité de travail sur l'ingénierie inverse ou l'analyse de l'amplificateur à partir de l'image ci-dessus et du processeur Baikal-T1, réalisée selon le processus de fabrication très populaire et relativement abordable de 28 nm. La rétro-ingénierie complète de ces gros produits est extrêmement rare, il est souvent intéressant de regarder certains blocs spécifiques et relativement petits. Par exemple, pour savoir s'ils violent votre brevet, ou pour comparer votre décision avec les produits de concurrents et essayer de comprendre pourquoi c'est mieux ou pire. Ou, pour le savoir, les développeurs de puces ont eux-mêmes implémenté telle ou telle fonctionnalité, ou emprunté votre bloc IP.

Figure 3. Un instantané de la topologie du processeur Baikal-T1. Source - zeptobars.com

Figure 3. Un instantané de la topologie du processeur Baikal-T1. Source - zeptobars.comNous passons ici à la prochaine partie importante de l'histoire de la rétro-ingénierie. Dans les temps anciens, la puce entière a été développée du début à la fin au sein d'une entreprise, parfois même par les forces d'une très petite équipe ou d'un solitaire brillant comme Bob Widlar. Les microcircuits modernes regorgent de blocs IP, dont la vente et l'achat constituent un énorme marché, qui, bien sûr, est également soumis au contrôle du droit d'auteur, à l'espionnage industriel et au piratage. Par conséquent, il est possible et nécessaire d'examiner le problème de la protection contre la copie non autorisée non seulement du point de vue du développeur du produit final, mais également du point de vue du développeur IP, pour lequel le développeur du produit peut également être un pirate.

Dans le cas du piratage, la structure interne de l'intrus n'est généralement pas intéressante pour recevoir des données, et une rétro-ingénierie partielle est effectuée (le cas échéant) afin de trouver des vulnérabilités et d'exploiter ces vulnérabilités, soit par connexion directe, soit en utilisant d'autres méthodes. La tâche du développeur contre le piratage est d'empêcher l'utilisation de points potentiellement faibles et, si nécessaire, de détruire les données sensibles lors d'une tentative de piratage.

PERSONNES INTÉRESSANTES

Pour commencer, essayons de déterminer qui peut protéger la conception de la puce contre cela. Les entités suivantes sont impliquées dans la chaîne de l'idée à l'application, ayant différents types d'accès aux informations sur le contenu du microcircuit.

- Développeur de blocs IP. Il a toutes les informations, tous les fichiers nécessaires, les méthodes de mesure, etc. etc.

- Développeur de puces. Dans le cas de Soft IP, Verilog / VHDL a un code de bloc; dans le cas de Hard IP, il peut avoir une topologie ou une boîte noire. S'il y a des parties programmables ou logicielles dans l'unité, il y a également accès.

- Usine A accès aux fichiers de topologie GDSII, mais n'a pas accès à la partie logicielle de la puce (par exemple, au micrologiciel PROM).

- Production d'emballage et de test. Il a accès à la puce, ainsi qu'aux méthodes de test et aux cartes de micrologiciel pour une mémoire programmable unique. Il est rare que quiconque se défende délibérément contre eux, mais ils devraient être sur la liste, car certaines des méthodes appropriées pour la protection de l'usine ne fonctionnent pas contre eux.

- Concurrent / cracker. Il n'a accès qu'au produit fini et à la documentation utilisateur.

Dans le cas le plus simple, le concepteur de puces (2) veut se protéger de la copie par un concurrent (5) ou fabriquer une puce avec de la mémoire protégée contre une lecture non autorisée. Dans un peu plus compliqué, le développeur IP (1) veut s'assurer que le développeur respecte la puce (2) du contrat de licence. Il arrive également que le développeur de la puce (2) ne fasse pas confiance à l'usine (3) et soupçonne qu'elle puisse conduire des contrefaçons le soir.

J'ai écrit en détail sur ce qu'est l'IP dans les circuits intégrés il y a quelque temps, donc je ne répéterai pas cet article. Il y a aussi un peu sur la façon dont les développeurs IP protègent leur propriété intellectuelle. En bref, afin de protéger la topologie, l'usine participe généralement en tant que tiers, et l'acheteur ne reçoit pas la topologie appropriée, et des techniques d'obscurcissement similaires à l'obfuscation de tout autre code sont utilisées pour protéger le code Verilog.OUTILS

Quels outils d'analyse de micropuce existent? Le premier niveau est un peu d'acide pour ouvrir d'abord le boîtier du microcircuit, puis retirer les couches une par une, et un microscope optique ordinaire avec une caméra. Il est peu coûteux, il est facile de travailler avec eux, et pour l’analyse de circuits simples réalisés à l’aide de technologies non récentes, cela suffit.

Pour les schémas plus importants, il existe des systèmes de CAO spéciaux qui permettent d'une manière ou d'une autre d'automatiser la restauration des données de la topologie - offrant au rétro-ingénieur une interface plus pratique pour le travail que le simple dessin de lignes dans un éditeur graphique. L'automatisation est également simplifiée par le fait que tous les circuits numériques modernes sont construits à partir de bibliothèques, et après l'ingénierie inverse des éléments de bibliothèque pour assembler un circuit est une question de temps (ou de puissance de traitement disponible).

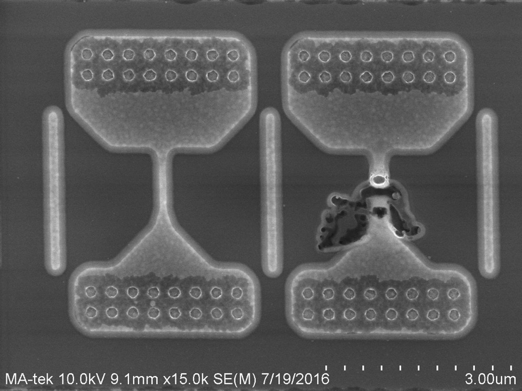

Le niveau suivant, inaccessible aux amateurs, mais présent dans les laboratoires spécialisés est le microscope électronique à balayage (MEB). Il utilise un faisceau d'électrons focalisé au lieu d'un faisceau lumineux. La résolution SEM peut aller jusqu'à 1 nm et même un peu plus bas, ce qui est suffisant pour analyser tous les circuits intégrés modernes.

Le FIB est un analogue du SEM, utilisant uniquement un faisceau d'ions plus lourds au lieu d'un faisceau d'électrons. En fait, FIB est Focused Ion Beam. La principale différence entre le FIB et le SEM est qu'avec son aide, vous pouvez non seulement analyser le microcircuit, mais aussi le modifier, par exemple, faire des coupes (afin de voir la section transversale du microcircuit ou enlever une pièce) ou pulvériser du matériel (afin de créer une connexion là-bas où il n'est pas). Les FIB sont largement utilisés par les développeurs et les fabricants de microcircuits pour travailler avec des échantillons de test, car il faut beaucoup de temps pour corriger l'erreur en l'utilisant, mais c'est toujours beaucoup plus rapide et moins cher que de redémarrer un lot expérimental. Pour un ingénieur inversé, c'est également un moyen unique d'accéder aux parties du cristal qui, selon l'intention du développeur, ne devraient pas être disponibles. Et, lors de la conception d'une puce protégée contre le piratage, cela doit également être pris en compte.

Figure 4. Coupe transversale d'un microcircuit réalisé en FIB. Source - SERESSA-2015 (soigneusement, beaucoup de trafic en pdf à partir du lien).

Figure 4. Coupe transversale d'un microcircuit réalisé en FIB. Source - SERESSA-2015 (soigneusement, beaucoup de trafic en pdf à partir du lien). Figure 5. Réalisation par modification FIB de la puce, modification de plusieurs connexions.

Figure 5. Réalisation par modification FIB de la puce, modification de plusieurs connexions.Un autre outil indispensable pour un ingénieur inversé est un ensemble de lasers. Les fans peuvent utiliser des lasers puissants avec lesquels ils peuvent ouvrir des microcircuits dans des boîtiers en plastique et accéder au cristal. Pour les lasers professionnels, selon la longueur d'onde, certaines parties de la conception du microcircuit peuvent être transparentes et d'autres non transparentes. Cela vous permet d'utiliser un laser, par exemple, pour ouvrir avec précision la passivation et l'isolation, afin que plus tard vous puissiez facilement rejoindre la ligne métallique sans risquer de la court-circuiter avec ses voisins. D'autres paramètres vous permettront de couper du métal ou de graver des transistors individuels. La troisième consiste à induire du courant dans les transistors en commutant des cellules de cache ou une sorte de lignes logiques. Cette dernière option est universellement utilisée comme une simulation peu coûteuse des effets des particules lourdes chargées, mais en principe, les dysfonctionnements dans un microcircuit de travail peuvent également être utiles pour compromettre les informations qu'il contient. Par exemple, il peut être intéressant de réécrire un indicateur dans le fichier de registre ou de corriger légèrement le fonctionnement du générateur de nombres aléatoires.

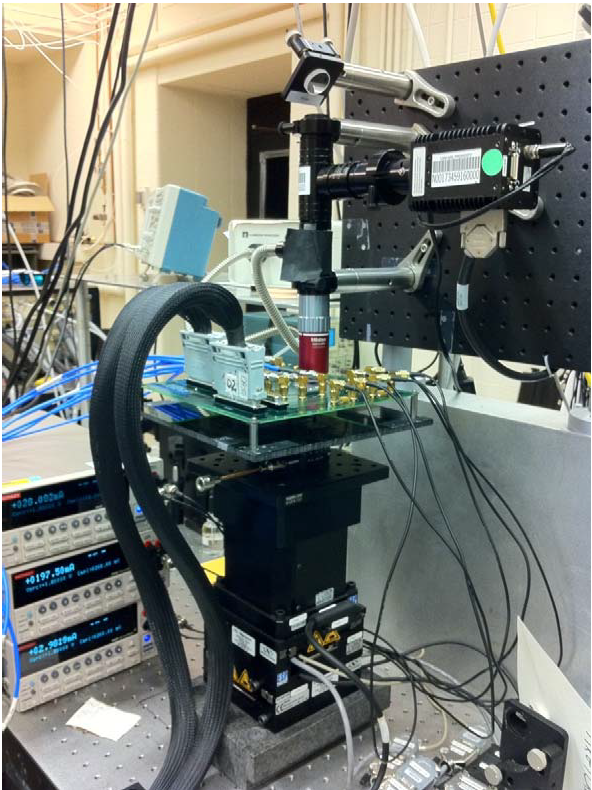

Figure 6. Aspect laser pour étudier l'effet des défaillances uniques sur les microcircuits. Source - SERESSA-2015.

Figure 6. Aspect laser pour étudier l'effet des défaillances uniques sur les microcircuits. Source - SERESSA-2015. Figure 7. Exemple de sensibilité d'une partie d'un microcircuit à un seul défaut et une défaillance obtenue à l'aide d'une carte laser. Source - SERESSA-2015.

Figure 7. Exemple de sensibilité d'une partie d'un microcircuit à un seul défaut et une défaillance obtenue à l'aide d'une carte laser. Source - SERESSA-2015.Dans les laboratoires avancés d'ingénierie inverse, vous pouvez trouver de nombreux autres outils intéressants; par exemple, un signal numérique jusqu'à plusieurs dizaines de MHz peut être surveillé en temps réel en plaçant un petit morceau de niobate de lithium sur la ligne correspondante et en l'illuminant à nouveau avec un laser.

CAS 1: USINE INUTILISABLE

Quelle pourrait être la raison de ne pas faire confiance à l'usine où vous fabriquez vos cristaux? Dans un monde idéal, bien sûr, vous ne vous impliquerez pas dans une usine à laquelle vous ne faites pas confiance, mais parfois des considérations commerciales vous obligent à prendre des risques. Il peut être minimisé de deux manières principales:

- La fabrication dite split ou, d'une manière simple, la production dans deux usines. Mais pas en parallèle (comme c'est généralement le cas pour minimiser le risque de pénurie en cas de retards imprévus de production), mais en partie dans les opérations d'une usine et d'une autre. Cela est plutôt gênant pour tous les participants au processus (et certainement pas toutes les usines seront d'accord avec cela), mais cela forcera l'usine peu fiable à au moins inverser le reste de la conception de la puce et à fabriquer les masques manquants par elle-même. (ce qui, idéalement, devrait faire en sorte que le jeu ne vaille pas la chandelle). Le principal inconvénient de cette approche est que les couches supérieures de la puce sont la métallisation, dont l'ingénierie inverse est assez simple. La fabrication en deux parties, cependant, peut être vraiment efficace en combinaison avec un certain savoir-faire technologique dans les métaux, qu'une usine peu fiable n'est pas en mesure de reproduire. Par exemple, si la deuxième usine de votre choix est capable de faire de la mémoire non volatile (MRAM, memristors ou quelque chose comme ça) dans la couche de métallisation supérieure, sans laquelle la conception entière perd son sens.

- Si vous ne possédez aucun savoir-faire technologique, alors le moyen simple et fiable est de rendre la puce vide de sens sans programmation supplémentaire. Les blocs programmables peuvent être réalisés indépendamment à l'aide de la mémoire de configuration, ou sous la forme d'un bloc basé sur un FPGA intégré (il existe de telles IP sur le marché). La mémoire de configuration comme moyen de protection vous permet d'être sûr que l'usine ne peut pas simplement prendre et produire votre puce en vous contournant. Mais vous pouvez lire la mémoire de configuration, non? Oui, mais la présence de la mémoire de configuration oblige une usine peu fiable, au lieu d'un moyen simple d'augmenter les volumes de production, à faire la même ingénierie inverse que tous les autres attaquants.

Séparément, je note que les deux méthodes de protection décrites contre une usine non fiable aident à empêcher la copie non autorisée, mais elles ne sauvent pas des «signets» populaires dans les cercles étroits. De plus, je parlerai un peu plus loin de la façon de mettre en signet la topologie nous-mêmes.

CAS 2: PROTECTION DE LA MÉMOIRE

La présence de blocs programmables et de mémoire de configuration dans la puce est un attribut presque indispensable de toute conception moderne, numérique et analogique. Avec une diminution des normes de conception, la propagation des paramètres de puce à puce augmente et le réglage numérique est le moyen le plus simple et le plus fiable de le surmonter. Et les circuits numériques (par exemple les microcontrôleurs) stockent généralement des données directement sur la puce et peuvent avoir une structure de mémoire à plusieurs niveaux, dont différentes parties ont différents niveaux d'accès et de protection. Par conséquent, il semble logique d'utiliser d'une part l'outil que nous avons déjà pour augmenter la sécurité et la résistance aux fissures, et d'autre part, l'idée de bien réfléchir au type de mémoire à utiliser.

Firmware avec connexions métalliques (Mask ROM). Cela ressemble généralement à la présence ou à l'absence de contact entre deux lignes métalliques, un peu moins souvent - à la présence ou à l'absence d'un transistor entre elles. Le plus en chêne est utilisé dans les cristaux à matrice de base (BMC) - non seulement dans l'ancienne industrie de la défense, comme vous pourriez le penser, mais aussi dans des solutions assez modernes, par exemple, dans les puces auxiliaires à l'intérieur des processeurs Xeon. De plus, en utilisant une telle mémoire, des familles de microcircuits sont réalisées (principalement des microcontrôleurs), car flasher la mémoire en usine en changeant un masque est moins cher que le firmware universel de chaque cristal produit sur une plaque ou dans un boîtier. Le masque ROM lit très facilement avec un microscope et une gravure précise. À la maison, vous pouvez le gérer.

Figure 8. Micrologiciel ROM avec interconnexions métalliques sur une fausse puce FTDI FT232RL. Source - zeptobars.com

Figure 8. Micrologiciel ROM avec interconnexions métalliques sur une fausse puce FTDI FT232RL. Source - zeptobars.com

Il convient également de noter ici qu'il est possible de flasher de la mémoire non seulement avec une couche de contacts entre les métaux, mais aussi avec la présence et l'absence de métal (facile à lire optiquement), la présence ou l'absence de dopage (facile à lire optiquement), ou, par exemple, la tension de seuil d'un transistor contrôlée par le niveau de dopage (mal lire optiquement). Donc, en principe, le masque ROM n'a pas tout perdu si vous voulez vraiment cacher son contenu.

Mémoire sur cavaliers brûlés (Fuse ROM). Il permet un enregistrement (y compris l'enregistrement par l'utilisateur sur l'appareil fini) et un nombre illimité de lectures, il est très simple à fabriquer et à programmer, et donc populaire pour toutes sortes de mémoire de configuration et de firmware.

Figure 9. Deux états de la ROM de fusible. Source - semiengineering.com

Figure 9. Deux états de la ROM de fusible. Source - semiengineering.comComme vous pouvez le voir, l'état d'un cavalier fusible ordinaire (Fuse) est très facile à voir à travers un microscope, c'est-à-dire qu'il est tout simplement impossible de se protéger d'ouvrir un cristal avec lui. Eh bien et, en plus de tout le reste, le cavalier grillé classique est assez grand (plusieurs microns carrés) et ne convient donc pas pour de grandes quantités de mémoire.

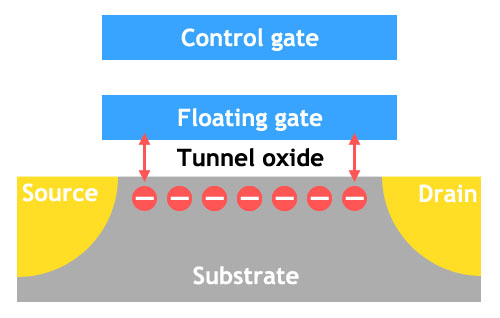

Mémoire flash et autres options EPROM et EEPROM basées sur des transistors à grille flottante.

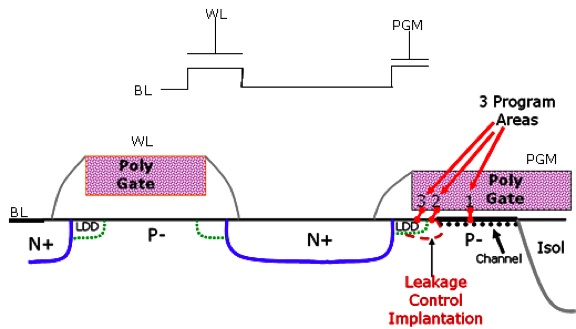

Figure 10. Schéma d'enregistrement Flash. Source - techreport.com

Figure 10. Schéma d'enregistrement Flash. Source - techreport.comLe principe de fonctionnement de ce type de mémoire est assez simple: une grille "flottante" est située dans une couche épaisse d'un diélectrique. Une charge électrique peut être placée dans ce volet par effet tunnel, en lui appliquant une haute tension. Et puis, si vous n'appliquez pas de haute tension, la charge peut être stockée pendant très longtemps dans l'obturateur «flottant».

Et la sécurité?

La bonne nouvelle est que l'état de l'EEPROM ne peut pas être vu avec un microscope. Mauvais? Il y en a plusieurs à la fois.La première mauvaise nouvelle est que l'EEPROM est effacée non seulement par la haute tension, mais aussi par l'exposition aux rayons ultraviolets (les anciens se souviennent probablement des éclats de verre de quartz). Dans le même temps, si vous examinez attentivement la topologie avec un microscope, vous pourrez peut-être couvrir toute la mémoire avec un matériau opaque, à l'exception des quelques bits qui incluent la protection en lecture et, après exposition, votre puce. Moralité: En utilisant l'EEPROM dans votre projet, couvrez-le avec du métal sur le dessus. Et il est souhaitable non seulement avec un écran solide contre les radiations, mais aussi avec certaines lignes importantes, de sorte que l'écran ne puisse pas être gravé avec précision. Cependant, une embuscade est également cachée ici (c'est aussi la deuxième mauvaise nouvelle), car en principe un microcircuit ou ses parties individuelles peuvent être mis en évidence par le bas. Ce n'est pas facile, car il faudra très probablement retirer la puce du boîtier et,par exemple, graver le fond du substrat, mais possible. Ces techniques sont populaires pour tester les microcircuits monopuce, car la métallisation est opaque aux UV et au laser, et le substrat de silicium est presque transparent, la question est de savoir comment focaliser correctement le faisceau de rayonnement si une exposition locale est nécessaire.Comme option alternative, vous pouvez configurer les bits d'activation / désactivation de la protection afin que leur effacement active la protection et non la désactive.La troisième mauvaise nouvelle est qu'il existe des capteurs qui peuvent lire la charge électrique dans une porte flottante ou ses restes après une opération d'effacement. De plus, pour lire électriquement la mémoire, en général, la puce n'a pas besoin d'être alimentée, c'est-à-dire qu'il n'y a aucun risque d'activer les mécanismes de destruction d'informations intégrés.Mram, bien que relativement rare, mérite également notre attention. Comme le flash, il ne peut pas être considéré optiquement. La MRAM, bien sûr, ne peut pas être effacée par la lumière ultraviolette, mais des capteurs de champ magnétique avec une résolution suffisamment élevée pour piquer les métaux supérieurs et lire la mémoire bit par bit existent. Bonne nouvelle? Il est peu probable qu'un attaquant potentiel les trouve rapidement et à peu de frais. En général, MRAM est une bonne alternative au flash du point de vue de la sécurité, mais jusqu'à présent, il n'est pas largement disponible et vient de se lancer dans la production de masse dans les technologies disponibles pour les entreprises sans usine.Aujourd'hui, la ROM antifusible est considérée comme la mémoire la plus protégée de l'ingénierie inverse.. Comme son nom l'indique, il représente un certain antipode des cavaliers brûlés, à savoir qu'il a une résistance élevée dans un état non programmé et faible dans un état programmé. Comment y parvient-on? Avec la rupture du diélectrique de grille de grille d'un transistor à haute tension. La zone de claquage est si petite qu'elle n'est visible ni du dessus au microscope ni dans la section sur le FIB, mais elle fournit également un bon et fiable changement de résistance de plusieurs ordres de grandeur, ce qui est tout à fait suffisant pour une lecture fiable de l'état de la mémoire de manière régulière. Une telle cellule de mémoire, cependant, peut être lue en se connectant directement à la grille et à la source du transistor de mémoire. Une cellule ininterrompue se comporte comme un condensateur, une cellule cousue se comporte comme une résistance. Figure 11. Section cellulaire d'une mémoire antifusible. Sont illustrés plusieurs domaines de panne possible du transistor. Cela peut compliquer le schéma de lecture.Bien sûr, il existe d'autres moyens de découvrir le contenu de la mémoire, en plus de l'inspection visuelle des cellules. Le moyen le plus simple consiste à utiliser FIB pour se connecter directement aux lignes de lecture correspondantes et à leur envoyer tous les signaux de commande qui doivent être envoyés afin de lire des informations inaccessibles de manière normale. Auparavant, vous pouvez désactiver la protection en lecture en coupant physiquement les lignes menant aux bits de mémoire correspondants. Comment vous en protéger? Ayant correctement conçu la topologie de votre puce et, éventuellement, y avoir intégré des fonctions supplémentaires. Voici un exemple de la façon dont Cypress fait cela:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.Habituellement, cela se fait: la mémoire est recouverte d'en haut par une grille de terre et de lignes électriques, et toutes les lignes de signaux sont situées strictement en dessous. Dans ce cas, il faut veiller à ce que les lignes électriques, d'une part, ne se dupliquent pas (c'est-à-dire, lors de la coupe de l'une d'entre elles, qu'une partie du microcircuit cesse de fonctionner), et d'autre part, de sorte que chacune d'elles serve beaucoup de bits de mémoire , et l'insertion d'un ampèremètre dans la ligne électrique n'a pas pu nous permettre d'estimer l'état de la mémoire par consommation en mode lecture (qui diffère pour différents états logiques dans la plupart des types de mémoire). Avec une telle organisation des couches supérieures de la puce, il sera extrêmement difficile pour un attaquant d'ouvrir une partie de la métallisation pour se connecter là où il en a besoin.Même dans le réseau de terrains et d'alimentations, des lignes de protection supplémentaires sont disposées de sorte qu'une coupure en elles (ou leur court-circuit à l'alimentation ou à la terre) lorsque l'alimentation est fournie à la puce déclenche l'effacement complet du contenu de la mémoire protégée (ou, comme nous l'avons vu ci-dessus, des dommages physiques puce). De telles lignes de protection, situées à côté des lignes terrestres et électriques, compliquent grandement le travail des attaquants, car les opérations avec la FIB nécessitent une place tangible par rapport aux processus technologiques actuels. De plus, en raison de la forme conique de la découpe créée par le microscope, plus la couche à laquelle vous souhaitez vous connecter est basse, plus vous devez nettoyer de surface.Mais en fait, très souvent, un attaquant peut ne pas avoir besoin de la valeur exacte du contenu de la mémoire, cela peut bien suffire à réduire le nombre d'options de tri de plusieurs ordres de grandeur. Par exemple, si une cellule mémoire consomme lors de la lecture d'une unité logique X et lors de la lecture d'un zéro logique 100 * X, alors lors de la lecture d'un octet d'une telle mémoire, nous obtiendrons une consommation différente en fonction du contenu de la mémoire:0 - 800 * X1,2,4, ..., 64, 128 - 701 * X3, 6, 7, ..., 160, 192 - 602 * X....255 - 8 * XAu total, si nous ne touchons pas à la mémoire, nous avons besoin de 256 tentatives pour sélectionner le mot de passe qu'il contient. Et si nous savons que la consommation en mode lecture est de 701 * X, alors il n'y en a que huit. Pratique, non? La façon la plus simple de résoudre ce problème consiste à stocker les données sous la forme d'une valeur et leur inversion dans une cellule voisine; alors la consommation de toute quantité de mémoire en mode lecture ne dépendra pas des informations stockées. Certes, cela nécessite deux fois plus de mémoire, mais la sécurité est importante pour nous, non?

Figure 11. Section cellulaire d'une mémoire antifusible. Sont illustrés plusieurs domaines de panne possible du transistor. Cela peut compliquer le schéma de lecture.Bien sûr, il existe d'autres moyens de découvrir le contenu de la mémoire, en plus de l'inspection visuelle des cellules. Le moyen le plus simple consiste à utiliser FIB pour se connecter directement aux lignes de lecture correspondantes et à leur envoyer tous les signaux de commande qui doivent être envoyés afin de lire des informations inaccessibles de manière normale. Auparavant, vous pouvez désactiver la protection en lecture en coupant physiquement les lignes menant aux bits de mémoire correspondants. Comment vous en protéger? Ayant correctement conçu la topologie de votre puce et, éventuellement, y avoir intégré des fonctions supplémentaires. Voici un exemple de la façon dont Cypress fait cela:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.Habituellement, cela se fait: la mémoire est recouverte d'en haut par une grille de terre et de lignes électriques, et toutes les lignes de signaux sont situées strictement en dessous. Dans ce cas, il faut veiller à ce que les lignes électriques, d'une part, ne se dupliquent pas (c'est-à-dire, lors de la coupe de l'une d'entre elles, qu'une partie du microcircuit cesse de fonctionner), et d'autre part, de sorte que chacune d'elles serve beaucoup de bits de mémoire , et l'insertion d'un ampèremètre dans la ligne électrique n'a pas pu nous permettre d'estimer l'état de la mémoire par consommation en mode lecture (qui diffère pour différents états logiques dans la plupart des types de mémoire). Avec une telle organisation des couches supérieures de la puce, il sera extrêmement difficile pour un attaquant d'ouvrir une partie de la métallisation pour se connecter là où il en a besoin.Même dans le réseau de terrains et d'alimentations, des lignes de protection supplémentaires sont disposées de sorte qu'une coupure en elles (ou leur court-circuit à l'alimentation ou à la terre) lorsque l'alimentation est fournie à la puce déclenche l'effacement complet du contenu de la mémoire protégée (ou, comme nous l'avons vu ci-dessus, des dommages physiques puce). De telles lignes de protection, situées à côté des lignes terrestres et électriques, compliquent grandement le travail des attaquants, car les opérations avec la FIB nécessitent une place tangible par rapport aux processus technologiques actuels. De plus, en raison de la forme conique de la découpe créée par le microscope, plus la couche à laquelle vous souhaitez vous connecter est basse, plus vous devez nettoyer de surface.Mais en fait, très souvent, un attaquant peut ne pas avoir besoin de la valeur exacte du contenu de la mémoire, cela peut bien suffire à réduire le nombre d'options de tri de plusieurs ordres de grandeur. Par exemple, si une cellule mémoire consomme lors de la lecture d'une unité logique X et lors de la lecture d'un zéro logique 100 * X, alors lors de la lecture d'un octet d'une telle mémoire, nous obtiendrons une consommation différente en fonction du contenu de la mémoire:0 - 800 * X1,2,4, ..., 64, 128 - 701 * X3, 6, 7, ..., 160, 192 - 602 * X....255 - 8 * XAu total, si nous ne touchons pas à la mémoire, nous avons besoin de 256 tentatives pour sélectionner le mot de passe qu'il contient. Et si nous savons que la consommation en mode lecture est de 701 * X, alors il n'y en a que huit. Pratique, non? La façon la plus simple de résoudre ce problème consiste à stocker les données sous la forme d'une valeur et leur inversion dans une cellule voisine; alors la consommation de toute quantité de mémoire en mode lecture ne dépendra pas des informations stockées. Certes, cela nécessite deux fois plus de mémoire, mais la sécurité est importante pour nous, non?CAS 3: SANS MÉMOIRE

Mais que se passe-t-il si votre puce ne contient pas de mémoire de configuration ou ne contient que quelques bits, qui n'ont aucun sens à cacher. Pourquoi? C'est donc beaucoup moins cher (non pas tant en réduisant le coût des masques pour la lithographie, mais par un processus plus simple d'emballage et de test), et pour la plupart des puces simples, le prix est un sérieux avantage concurrentiel.

En parlant de tests. Le processus de rejet des cristaux sur les wafers et de la mémoire de configuration clignotante est souvent externalisé, en particulier par les petites entreprises, car l'équipement approprié n'est généralement pas abordable pour les startups, et la qualité doit être assurée. Donc, si la production tierce est à jour avec vos méthodes de test et dispose d'un firmware de mémoire de configuration, il serait préférable pour vous de faire entièrement confiance à ces personnes. Ou disposez de méthodes de protection supplémentaires contre l'ingénierie inverse qui ne sont pas liées à la mémoire de configuration.

Que faire si la mémoire de configuration n'est pas une option de protection ou si elle n'est pas suffisante?

Le principal inconvénient d'un microscope optique et d'un SEM est qu'il est très difficile de distinguer les types de dopage du silicium. Autrement dit, la présence d'alliage est visible, mais le type ne l'est pas. Par conséquent, lors de l'analyse de la topologie et de l'extraction du circuit, le type de dopage est restauré à partir du contexte et de la logique implicite du circuit (les transistors à canal n sont connectés à la masse, les transistors à canal p sont connectés à l'alimentation, etc., etc.). Après avoir dessiné la topologie de votre microcircuit afin qu'elle ne coïncide pas avec l'option la plus intuitive du plus probable, vous pouvez très bien gâcher le sang d'un reverse engineering. Surtout si vous utilisez plusieurs schémas différents déguisés en les mêmes. Avec une certaine dextérité, vous pouvez non seulement compliquer l'analyse de votre circuit, mais aussi faire en sorte que le dispositif (ou du moins modélisé, mais plus amusant s'il est produit) en utilisant la topologie restaurée fasse quelque chose de spécifique, de court-circuiter le sol avec du pouvoir à émettre des mots obscènes à toutes les sorties. Soit dit en passant, le comportement déterministe d'une conception mal volée peut être utile non seulement pour brûler un oscilloscope aux pirates, mais aussi pour que lorsque des utilisateurs frustrés de vos puces vous reviennent plus tard, vous pouvez clairement leur démontrer qu'ils ont acheté faux.

Figure 12. Coupe de trois structures indiscernables au microscope. Celui de gauche est pMOSFET, celui du milieu est un court-circuit, celui de droite est une diode polarisée en inverse (écart).

Figure 12. Coupe de trois structures indiscernables au microscope. Celui de gauche est pMOSFET, celui du milieu est un court-circuit, celui de droite est une diode polarisée en inverse (écart). Figure 13. Topologie de trois cellules de bibliothèque numérique indiscernables par un microscope. Celui de gauche est l'onduleur, celui du milieu est la connexion directe de l'entrée et de la sortie, celui de droite est l'unité logique de sortie.

Figure 13. Topologie de trois cellules de bibliothèque numérique indiscernables par un microscope. Celui de gauche est l'onduleur, celui du milieu est la connexion directe de l'entrée et de la sortie, celui de droite est l'unité logique de sortie.Chacune des cellules de la figure ci-dessus ressemble presque à l'onduleur le plus ordinaire, mais il peut en fait être un onduleur, un répéteur ou un générateur d'un zéro logique ou d'une unité logique. Seuls nos contacts de diffusion depuis l'entrée et la sortie donnent notre «onduleur». Cependant, en les abandonnant, nous obtiendrons un circuit complètement indiscernable du circuit standard en échange de l'impossibilité de mettre en œuvre la connexion d'entrée et de sortie (mais nous pouvons utiliser deux onduleurs à cet effet). Cependant, avec la possibilité d'inverser ou de ne pas inverser un signal en utilisant la même cellule, la lutte contre un attaquant est beaucoup plus intéressante, car rien ne complique les tentatives de traiter des problèmes de conception inconnue comme un onduleur supplémentaire quelque part dans l'horloge ou le circuit marche / arrêt.

Bien que non, cela arrive. Une topologie manuelle bien construite est généralement bien lue. Un excellent

exemple est dans le blog de Ken Schirriff déjà mentionné.

Figure 14. Unité logique arithmétique (ALU) de la puce Intel 8008. Des chiffres séparés sont affichés.

Figure 14. Unité logique arithmétique (ALU) de la puce Intel 8008. Des chiffres séparés sont affichés.Sur la topologie de l'ALU Intel 8008, huit circuits identiques sont parfaitement visibles - par le nombre de bits. Comprenant qu'il s'agit d'ALU, vous pouvez facilement restaurer le schéma de topologie. Si certains de ses éléments sont faux, cela compliquera quelque peu votre travail, mais pas plus. Et tout cela parce que la topologie s'intègre bien dans l'idée de base des interfaces entre les parties constituantes. Afin de confondre un attaquant au point qu'il abandonne les tentatives de reverse engineering, il est nécessaire de rendre la topologie imprévisible et non répétable. Le moyen le plus simple n'est pas de créer des blocs manuellement, mais de générer la liste complète de la puce à l'aide de la CAO. Les traceurs automatiques, malgré les énormes économies de temps sur la création d'une topologie (par rapport au travail manuel), font un excellent travail de création d'un agencement non intuitif des éléments et par endroits des connexions complètement folles. Et plus la conception est grande, dont la topologie a été synthétisée dans son ensemble, plus il est difficile de faire de l'ingénierie inverse.

Mais c'est le moyen le plus simple. Il existe des options plus intéressantes. Par exemple, utilisez un ensemble de cellules de caméléon comme un ensemble de générateurs de zéros logiques et de uns pour les entrées du multiplexeur, tout en réalisant une fonction logique arbitraire. En fait, c'est ainsi que les éléments du FPGA, LUT (Look-Up Table) sont disposés.

Figure 15. Implémentation d'une LUT à trois entrées. Source

Figure 15. Implémentation d'une LUT à trois entrées. SourceEn plaçant plusieurs de ces LUT à différents endroits du circuit et en apportant des signaux aux entrées des «cellules de mémoire», nous résoudrons plusieurs problèmes à la fois:

- Si notre manœuvre reste non résolue, nous serons en mesure de définir exactement comment le circuit de rétro-ingénierie se comportera. Options - toutes, limitées uniquement par votre imagination.

- L'utilisation de signaux arbitraires provenant d'autres blocs comme «entrée» pour les cellules générant un zéro logique et un compliquera le processus de séparation visuelle de la conception en blocs.

- Même si l'ingénierie inverse se rend compte que nous utilisons de telles LUT protégées, il devra trier de nombreuses options pour restaurer la fonctionnalité du circuit en fonction de la topologie, de sorte que même un nombre relativement petit de cellules protégées puisse rendre l'ingénierie inverse inutilement longue. Mon préféré est d'assembler une machine d'état sur de telles LUT qui contrôle les transitions du microcircuit d'un mode de fonctionnement à l'autre.

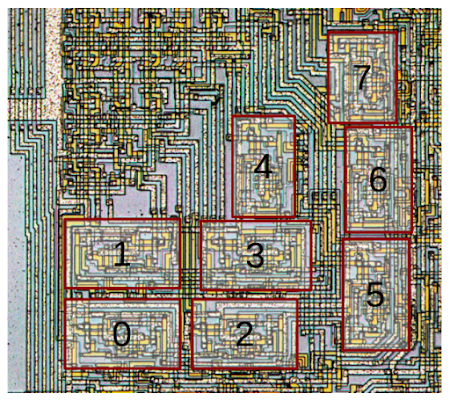

DIAGRAMMES D'ESSAI

Les bons ingénieurs aiment beaucoup tester leurs puces en détail. Et par «globalement», je veux dire - à peu près de la même manière que dans le convertisseur TI DC / DC de la figure ci-dessous. Des dizaines de petits plots de contact, auxquels vous pouvez vous connecter avant de couper la plaque en cristaux individuels, pour vérifier tous les paramètres nécessaires, l'état des lignes internes importantes, décider si la puce est appropriée ou non et, si nécessaire, trouver la cause des problèmes.

Figure 16. Topologie Texas Instruments TPS 62321. Source - zeptobars.com

Figure 16. Topologie Texas Instruments TPS 62321. Source - zeptobars.comUne bonne couverture avec des tampons de test pour les lancements de tests et les prototypes est particulièrement importante, mais pour la production en série, ils sont souvent désactivés (par correction d'un ou deux masques ou cavaliers brûlables) pour minimiser l'effet sur le comportement du produit. Alors, de quoi je parle? Les blocs de contact de test sont d'une grande aide pour un attaquant, car non seulement vous signalez vous-même les points importants de la conception, mais vous y donnez également un accès pratique. Le cavalier grillé est facilement restauré sur FIB, et le tour est joué! Idéalement, la sécurité nécessite le retrait complet des tampons de test de la puce série. Si cette option est irrationnelle (par exemple, vous avez également besoin de tests sur la plaque en production en série), assurez-vous au moins que le mécanisme de déconnexion des sites de test n'est pas récupérable, par exemple, est situé directement sous la plate-forme et a été tracé de sorte que l'écart n'a pas pu être connecté commodément.

Je ne veux même pas commencer par le fait que toutes les conceptions numériques modernes ont un JTAG intégré pour les tests, qui vous permet de voir directement l'état de tout déclencheur sur une puce. La pertinence des tests est l'une des caractéristiques clés de toute conception, et c'est ce fait qui rend extrêmement important la désactivation sûre et permanente de toutes les interfaces de test avant que la puce ne quitte les murs du fabricant.

Encore de bons ingénieurs aiment placer des circuits de test à la périphérie de la puce pour les prochaines révisions. Ce sont généralement des programmes assez importants, sinon pourquoi perdre du temps et des efforts à organiser leurs tests? "Les circuits importants qui constituent votre propriété intellectuelle et sont essentiels au fonctionnement de la puce?" Soigneusement mis à part le design entier? Merci beaucoup! ” - l'ingénieur inverse vous le dira pour un tel cadeau royal. Si vous ne voulez pas que les tests aident un attaquant à étudier et copier votre conception, assurez-vous qu'ils ne pénètrent pas dans les cristaux pour la production de masse ou qu'ils sont détruits après les tests sur des plaques pendant le processus de découpe de la plaque en cristaux.

UNE PETITE PRATIQUE

Afin de démontrer une nouvelle fois comment cela fonctionne, l'

exemple de l' ouverture du microcontrôleur PIC12C508A décrit dans la thèse de Sergei Skorobogatov, défendu en 2004 à Cambridge. La traduction est courte et plutôt gratuite:

Il faut ouvrir le boîtier et retrouver sur la puce une mémoire protectrice effacée par les rayons ultraviolets. Cela se fait assez facilement en visualisant les lignes allant à la broche de programmation de la puce. Ensuite, vous couvrez la mémoire principale avec un matériau opaque pour les UV, et après cinq à dix minutes d'exposition, vous pouvez considérer la mémoire comme un programmeur régulier. Une autre option - après avoir trouvé la mémoire de protection contre la copie, coupez simplement le chemin métallique qui y mène, qui sur cette puce est situé pour une raison quelconque loin des autres lignes - si loin que vous pouvez le couper non seulement avec FIB, mais juste avec une aiguille. Figure 17. Et voici la ligne très malheureuse. En effet, il est situé au milieu d'un espace vide, non protégé en aucune façon, il peut être coupé.

Figure 17. Et voici la ligne très malheureuse. En effet, il est situé au milieu d'un espace vide, non protégé en aucune façon, il peut être coupé.CONCLUSION

Bien sûr, il est impossible de saisir l'immensité, car la technologie et la rétro-ingénierie des microcircuits, et la protection contre eux, ne s'arrêtent pas et sont constamment améliorées. Le sujet de la sécurité de l'information est l'un des éléments clés de la conception de l'Internet des objets, donc les développeurs y prêtent beaucoup d'attention, et les rétro-ingénieurs ne peuvent pas s'attendre à une extraction aussi facile qu'il y a quinze ou vingt ans. Néanmoins, il faut toujours se rappeler qu'un système mal protégé signifie des pertes potentielles, d'énormes pertes ou même la vie de personnes, et la protection contre les accès non autorisés et la rétro-ingénierie devrait faire partie du système à tous les niveaux de fonctionnement, sans exclure le «fer». .