Comme promis la dernière fois, nous commençons une analyse détaillée de l'unité arithmétique et logique (ALU).

Le contenu général du cycle «UDB. Qu'est-ce que c'est? "

Partie 1. Introduction. Pld.Partie 2. Chemin de données.Partie 3. Datapath FIFO.Partie 4. Datapath ALU. (Article actuel)

Partie 5. Chemin de données. Petites choses utiles.Partie 6. Module de gestion et d'état.Partie 7. Module de commande de temporisation et de réinitialisationPartie 8. Adressage UDB21.3.2.4 Datapath ALU

Le noyau ALU se compose de trois fonctions programmables 8 bits indépendantes: un bloc arithmétique / logique, un bloc de registre à décalage et un bloc de superposition de masque.

Opérations arithmétiques et logiques

Les fonctions ALU sélectionnées dynamiquement à l'aide de la RAM de configuration sont présentées dans le tableau ci-dessous.

Tableau 21-8. Fonctions ALU

Porter

Carry in est utilisé dans les opérations arithmétiques. Comme le montre le tableau 21-9, des valeurs de report par défaut existent pour certaines fonctions.

Tableau 21-9. Fonctions Carry In.

En plus de ces applications arithmétiques régulières, il existe trois autres options d'utilisation de la césure. Les bits CI SELA et CI SELB définissent les règles d'utilisation de l'entrée de report pour chaque mesure. La RAM de configuration dynamique sélectionne la configuration A ou B à chaque cycle. Les paramètres sont indiqués dans le tableau 21-10.

Tableau 21-10. Caractéristiques supplémentaires

Si le report est utilisé, il est utilisé dans un certain nombre de fonctions, comme indiqué dans le tableau 21-11. Veuillez noter que pour les fonctions de décrémentation et de soustraction d'unité, le niveau de transfert actif est faible (inverse).

Tableau 21-11. Fonctionnalités de suivi tracées.

Réaliser

Exécution - sortie Datapath en option, formée sur la base d'un bit élevé statiquement spécifié. La valeur peut être transmise le long de la chaîne à l'entrée de transfert vers un bloc plus ancien. Notez que dans le cas des fonctions de décrémentation et de soustraction, l'exécution est inversée.

Tableau 21-12. Caractéristiques Carry Out.

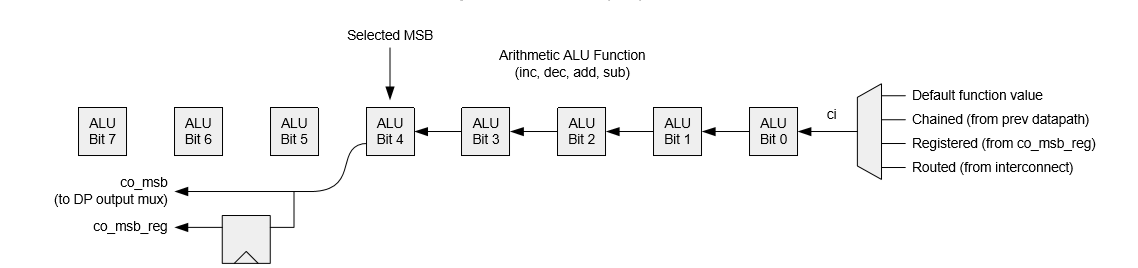

Structure de transfert

Les paramètres de

report et pour le choix du bit le plus significatif, pour générer le

report, sont illustrés à la Figure 21-15. Les valeurs de

report verrouillées peuvent être utilisées comme

report pour des opérations arithmétiques ultérieures. Cette fonctionnalité peut être utilisée pour implémenter des fonctions de capacité supérieure à l'aide de cycles.

Figure 21-15. Opération de transfert.

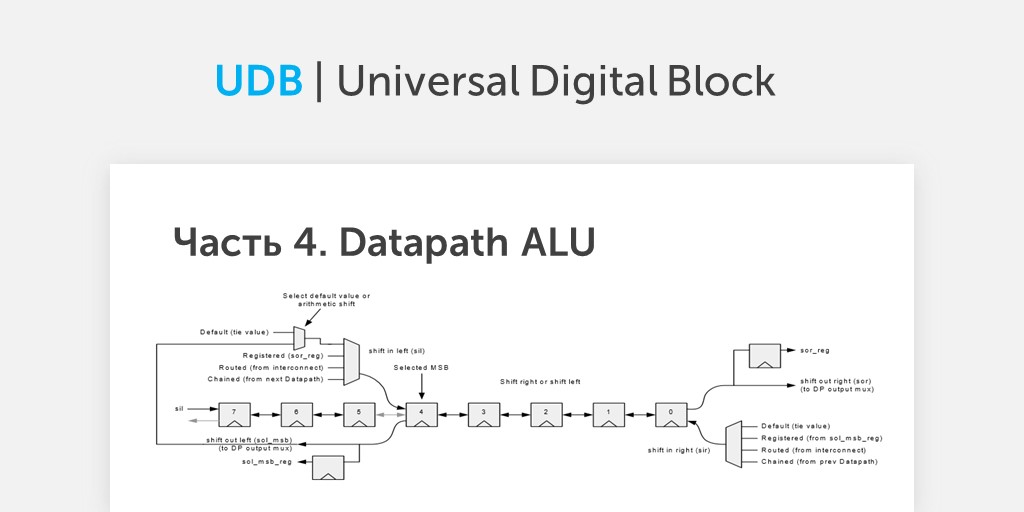

Figure 21-15. Opération de transfert.Opération de décalage

L'opération de décalage se produit indépendamment du fonctionnement de l'ALU, selon le tableau 21-13.

Tableau 21-13. Fonctions de l'opération de décalage.

La valeur de sortie de l'opération de décalage est émise avec Datapath. Les sorties de décalage vers la droite (

sor ) et vers la gauche (

sol_msb ) sont

configurées avec les mêmes bits. Le bit de configuration statique (SHIFT SEL dans le registre CFG15) détermine quelle sortie de décalage est utilisée comme sortie Datapath. En l'absence de décalage,

sor et

sol_msb sont définis respectivement comme LSB et MSB de la fonction ALU.

Les bits de configuration SI SELA et SI SELB déterminent le décalage de données pour l'opération spécifiée. La RAM de configuration dynamique sélectionne la configuration A ou B pour chaque cycle d'horloge. Les données poussées ne sont utilisées que pour les déplacements vers la gauche et la droite, cette entrée n'est pas utilisée lors du saut et de la réorganisation des grignotages. Les valeurs et les cas d'utilisation sélectionnés se rapportent à la fois à un décalage à droite et à un décalage à gauche, et sont présentés dans le tableau 21-14.

Tableau 21-14. Changement de fonctions

La sortie lors du décalage vers la gauche est prise à partir du bit spécifié comme haut. Lorsqu'elles sont décalées vers la droite, les données d'entrée sont poussées à partir de la position senior (MSB) sélectionnée. La sortie, même lors d'un décalage vers la gauche, même lors d'un décalage vers la droite, est verrouillée et peut être utilisée sur la mesure suivante. Cette fonctionnalité peut être utilisée pour implémenter un décalage de plus grande capacité en plusieurs cycles.

Figure 21-16. Opération de décalage.

Figure 21-16. Opération de décalage.Il est à noter que les bits isolés en choisissant MSB sont toujours décalés. Dans l'exemple illustré, le bit 7 est toujours décalé vers sil lorsqu'il est décalé vers la droite, et le bit 5 est décalé vers le bit 4 lorsqu'il est décalé vers la gauche. Le bit de sortie (droite ou gauche) d'un groupe isolé sera perdu.

Opération de superposition de masque ALU

Le registre de masque à 8 bits dans l'espace statique des registres de configuration UDB définit l'opération de masquage. Dans cette opération, un masque (opération ET) avec la valeur de ce registre est superposé à la sortie ALU. Une utilisation typique de l'opération de masquage ALU est la mise en œuvre de temporisateurs et de compteurs autonomes avec une résolution qui est un multiple d'une puissance de deux.

21.3.2.5. Entrées de chemin de données et multiplexage

Comme le montre le tableau 21-15, chaque chemin de données a 9 entrées, dont 6 entrées de suivi de canal. Il s'agit notamment des adresses de configuration de la RAM, du FIFO, des signaux de commande pour le chargement des registres de données, ainsi que du décalage et du transfert des entrées de données.

Tableau 24-15. Entrées de chemin de données

Comme le montre la figure 21-17, chaque entrée a un multiplexeur 6 en 1, par conséquent, toutes les entrées sont interchangeables. Les entrées sont traitées de deux manières: soit par niveau, soit par différentiel. L'adresse dans la RAM de la configuration dynamique, ainsi que les valeurs de décalage et de données sont sensibles au niveau. Les signaux de données FIFO et de registre de charge sont sensibles aux différences.

Figure 21-17. Signaux d'entrée de chemin de données.

Figure 21-17. Signaux d'entrée de chemin de données.Dans le prochain article, nous passerons à un examen de petites choses utiles.