Bien que 14 ans se soient écoulés depuis l'introduction du

premier SSD SATA , de nombreux consommateurs se réfèrent toujours aux

disques SSD avec beaucoup de scepticisme. La principale raison de la méfiance est la ressource de travail limitée de la mémoire flash, en raison de la dégradation progressive de la structure semi-conductrice des puces, à la suite de laquelle les appareils perdent tôt ou tard leur capacité à enregistrer et stocker des informations. Les spécifications techniques détaillées ne font qu'aggraver les choses: il est difficile pour un client de comprendre si le TBW 500 TB mentionné dans la description du SSD Western Digital Blue 3D NAND SATA pour deux téraoctets est beaucoup ou peu? Combien durera un tel disque dans des conditions de fonctionnement réelles et pourra-t-on lui faire confiance avec les fichiers les plus précieux? Essayons de comprendre ce problème ensemble et parlons de la fiabilité de la mémoire flash moderne.

À strictement parler, la réponse à la «principale question de la vie, l'univers et tout ce qui» a été reçue en décembre 2014, lorsque les gars de la publication du réseau

TechReport ont terminé de tester les SSD grand public, qui ont duré un total d'un an. À l'aide d'exemples HyperX, Corsair, Kingston et Samsung, ils ont prouvé de façon convaincante que la vie réelle des SSD dépasse 1 pétaoctet de doublage. De tels volumes sont presque impensables non seulement pour l'utilisateur moyen, mais même pour les créateurs de contenu professionnels: le lecteur deviendra moralement obsolète bien avant que ses ressources ne soient épuisées.

Cependant, il y a une nuance importante: il y a quatre ans, des puces MLC NAND étaient utilisées, capables de stocker 2 bits d'informations dans chaque cellule et fabriquées à l'aide d'une technologie de processus de 25 nanomètres. À cette époque, c'était un bon compromis entre le SLC très fiable (cellule à un niveau) et le TLC plus spacieux et peu coûteux (cellule à trois niveaux): les puces avec des cellules à deux bits fournissaient une densité de stockage de données acceptable, supportant jusqu'à 5000 cycles d'écriture / effacement (en en moyenne, ce chiffre atteint 3 000). Ce que l'on ne peut pas dire de leurs frères les plus proches: pour tous les avantages, qui incluent une grande capacité et un faible coût, les TLC ont été beaucoup moins robustes, ayant à peine dépassé la barre des 1500000 cycles de programmation / effacement, malgré le fait que la plupart des microcircuits plans peuvent à peine en supporter mille.

Le principal coupable de cette situation a été la transition vers un procédé de 15 nanomètres utilisé dans la production de puces. Pour comprendre pourquoi cela s'est produit, rappelez-vous simplement comment fonctionne la mémoire NAND. Le codage des bits d'information se produit en modifiant la charge sur une grille flottante en raison de la tunnellisation quantique des électrons à travers la couche diélectrique, en raison de la forte intensité du champ électrique.

Circuit transistor à grille flottanteDu point de vue de la physique, il ne s’agit que du phénomène de panne réversible de type avalanche. En accélérant dans un champ électrique, les électrons reçoivent suffisamment d'énergie cinétique pour l'ionisation par impact des molécules diélectriques, résultant en une paire de particules élémentaires portant la charge opposée, qui sont également accélérées par un champ électrique, et le processus se répète, tandis que le nombre de porteurs de charge augmente de façon exponentielle (d'où le nom ) Il est facile de deviner que de tels processus provoquent une usure progressive des couches diélectriques, en conséquence, la probabilité de fuite de charge vers les cellules voisines augmente, ce qui, à son tour, entraîne des dommages, voire une perte complète des données. Et la transition vers une nouvelle technologie de processus ne fait qu'exacerber la situation: une diminution de l'épaisseur du diélectrique conduit au fait que les cellules tombent en panne beaucoup plus tôt.

Cependant, si le problème n'était que cela, les consommateurs ordinaires et les utilisateurs d'entreprise ne remarqueraient tout simplement pas la différence entre MLC et TLC, et dans les spécifications techniques des SSD, nous verrions des chiffres beaucoup plus impressionnants. En réalité, une image complètement différente apparaît sous nos yeux, et l'architecture des puces flash et les spécificités de leur travail en sont la raison: les cellules individuelles sont combinées en pages et les pages en blocs, tandis que les informations ne peuvent être écrites que sur des pages vierges et leur suppression est effectuée bloc par bloc.

Qu'est-ce que cela signifie dans la pratique? Supposons que nous ayons un bloc partiellement rempli et que nous voulons y écrire de nouvelles données. Si leur volume est inférieur à l'espace libre restant, l'enregistrement se produit instantanément, sans aucune manipulation supplémentaire. S'il n'y a pas assez d'espace, des algorithmes complexes à plusieurs étapes entrent en jeu. Considérez la situation dans le diagramme ci-dessous.

Voici comment les données sont écrites dans la mémoire flashLes nouvelles données que nous voulons enregistrer occupent deux pages dans un bloc, mais une seule est vraiment gratuite: bien que l'ancienne page (surlignée en jaune) ait été supprimée par l'utilisateur plus tôt, en fait, les informations enregistrées n'ont pas disparu. Pour libérer de l'espace pour les nouvelles données, le contrôleur lance une procédure connue sous le nom de garbage collection, supprimant les données inutiles et redistribuant celles existantes. Pour ce faire, toutes les pages, à l'exception des pages inutiles, sont copiées dans le deuxième bloc libre, tandis que la première est complètement effacée. Ensuite, les pages réelles sont retransférées dans le premier bloc, supprimées du second, et seulement après que les nouvelles données prennent la place qui leur revient.

Dans l'exemple ci-dessus, pour enregistrer deux pages, nous avons dû réécrire complètement 2 blocs deux fois, six pages chacun. En fait, le processus «Garbage Collection» sera beaucoup plus compliqué et, par conséquent, le nombre de cycles de réécriture sera beaucoup plus important. L'image réelle ne peut être estimée qu'en connaissant le coefficient d'amplification d'écriture, qui montre combien de fois la charge réelle sur la mémoire flash dépasse celle calculée. Cet indicateur ne peut être égal à l'unité que lors de l'enregistrement d'informations sur un disque parfaitement propre et juste formaté, dans tous les autres cas, sa valeur variera de 2 à 25. De plus, même à première vue, des lecteurs identiques, il peut varier considérablement, donc en fonction du modèle du contrôleur utilisé et des fonctionnalités du firmware. Ainsi, la tolérance aux pannes SSD est déterminée non seulement par le type de mémoire flash, mais également par la capacité des développeurs à optimiser les performances de la couche FTL (Flash Translation Layer).

Pourquoi l'augmentation spectaculaire de la densité de stockage n'a-t-elle pas affecté la fiabilité de la mémoire NAND 3D?

Ainsi, nous savons maintenant comment fonctionne la mémoire flash et quels facteurs déterminent la fiabilité d'un disque SSD. Il est temps de comprendre les avantages de la transition des puces «plates» aux puces tridimensionnelles. Tout d'abord, la 3D NAND diffère de ses prédécesseurs en raison de l'utilisation du «piège de charge» (Charge Trap Flash) au lieu des volets flottants familiers. Si dans ce dernier, du polysilicium avec des dopants est utilisé pour stocker les charges, alors dans le CTF, il s'agit d'une région isolée de matériau non conducteur, le plus souvent SiN - nitrure de silicium. Une telle approche a permis de minimiser la probabilité de fuite de charge et, par conséquent, d'augmenter la stabilité de la cellule.

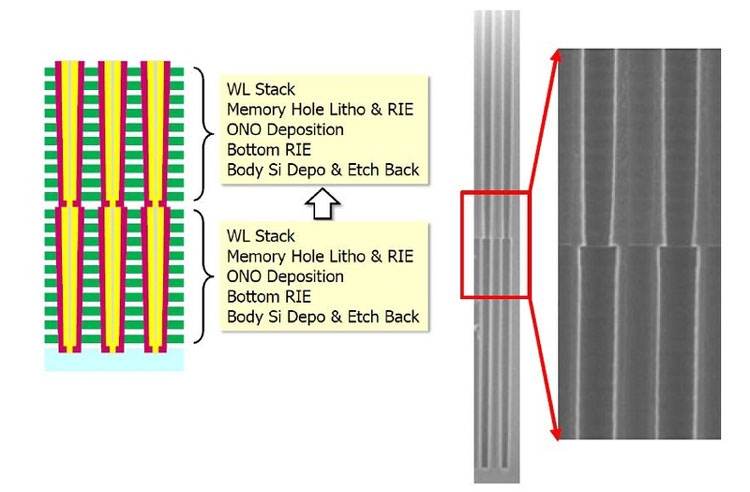

L'architecture des puces de mémoire tridimensionnelles a également subi des changements importants par rapport à son prédécesseur, car maintenant chaque cellule a une structure cylindrique: la couche externe est une porte de contrôle et l'intérieur est un isolant. Les cellules étant désormais situées l'une au-dessus de l'autre, elles forment un empilement, à l'intérieur duquel passe un canal en silicium polycristallin. Il est facile de comprendre que le nombre de couches dans une puce détermine le nombre de cellules dans la pile.

Dispositif de cellule à puce NAND 3DCette structure a permis de réduire les interférences entre les cellules et ainsi de simplifier l'algorithme d'enregistrement: puisqu'il n'était pas nécessaire de vérifier l'état de charge, l'enregistrement dans la cellule a commencé en une seule étape. Autre nuance importante: pour la production de 3D NAND, des processus de rodage sont utilisés, malgré le fait que la densité de tassement des cellules a pu augmenter de manière significative. Ainsi, par exemple, même des puces à 48 couches (la troisième génération de mémoire flash tridimensionnelle) ont été produites en utilisant une technologie de processus de 40 nanomètres. Cela a permis non seulement d'augmenter leur fiabilité, mais aussi de réduire le coût de production, car les lignes de production existantes ne nécessitaient qu'une modernisation minimale, et le besoin de lithographie en ultraviolet profond a complètement disparu.

En parlant spécifiquement des produits Western Digital, puis dans les

SSD modernes

WD Black SN750 NVMe , dont le début des ventes a commencé le 18 janvier 2019, le TLC 3D NAND BiCS (Bit Cost Scalable) 64 couches, fabriqué à l'aide de la technologie de processus de 28 nanomètres, est utilisé. En plus d'augmenter la densité d'emballage de 1,4 fois (le modèle haut de gamme a désormais une capacité de 2 To, soit le double de la taille du produit phare de la génération précédente), une caractéristique importante de ce type de puce est l'utilisation de cordes en forme de U.

Architecture 3D NAND BiCSÉtant donné que le transistor de commutation et la ligne source sont maintenant situés dans la partie supérieure de la puce, ils ne sont pratiquement pas exposés à des influences à haute température, qui peuvent elles-mêmes entraîner des erreurs lors des opérations de lecture / écriture, ce qui améliore encore la fiabilité des disques SSD.

Comment les algorithmes d'enregistrement affectent-ils la durée de vie d'un SSD?

Nous avons déjà écrit ci-dessus que peu importe la robustesse et la sécurité de la mémoire flash elle-même, sa ressource sera gaspillée si les développeurs de SSD ne se donnaient pas la peine de créer des algorithmes d'enregistrement efficaces. Pour optimiser cette procédure, deux techniques très efficaces sont utilisées: la mise en cache SLC et la mise à niveau d'usure.

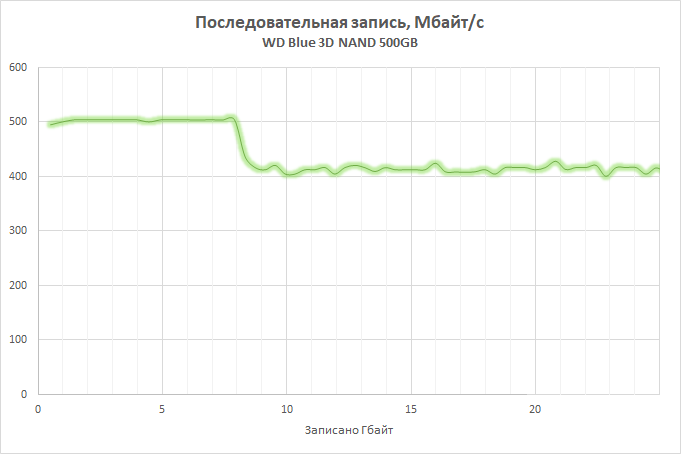

L'essence de la première est qu'une partie de la matrice mémoire disponible, dont la taille dépend du volume total du disque (par exemple, lors du développement du

SSD WD Blue 3D NAND, nous sommes partis du calcul de 4 Go de cache pour chaque 250 Go de capacité) est transférée en mode de fonctionnement SLC, c'est-à-dire , un seul bit d'information est enregistré dans chaque cellule, ce qui permet à la fois d'augmenter significativement ses performances et de réduire le taux d'usure. Le SLC est impliqué dans l'enregistrement et la consolidation des données stockées sur le SSD, ce qui permet non seulement d'augmenter la vitesse des opérations, mais également de réduire le taux d'usure des cellules. Dans les versions actuelles des SSD Western Digital, la technologie nCache 3.0 est utilisée, dont la dernière version a acquis la fonction direct-to-TLC, qui a permis de trouver un équilibre entre la mise en cache et la vitesse: les données sont écrites en contournant le cache lorsqu'il est plein ou en utilisant SLC- le tampon n'est pas pratique. Cela, d'une part, a aidé à décharger le cache et en même temps à éviter une baisse spectaculaire des performances lors du remplissage.

Quant à la technologie de nivellement de l'usure, elle permet de s'assurer que tous les blocs de page disponibles sont utilisés de manière aussi homogène que possible. Comme vous le savez, tout système d'exploitation utilise un mécanisme logique pour adresser les blocs de données (LBA), tandis que le contrôleur lui-même fonctionne avec des adresses physiques (PBA), en les corrélant avec des adresses logiques. Par conséquent, peu importe où se trouvent réellement les fragments des fichiers, grâce à quoi il est possible d'écrire un microprogramme qui garantira que la charge entre les cellules est répartie uniformément.

La mise à niveau d'usure assure une charge uniforme sur les cellulesDans le cas général, son algorithme est le suivant. Vous avez acheté un tout nouveau SSD et bien qu'il y ait de l'espace libre dessus, les informations seront enregistrées dans des blocs libres. Au fur et à mesure que vous opérez, vous commencez à supprimer les fichiers inutiles et le mécanisme de récupération de place les nettoie en arrière-plan.Cependant, ils ne seront utilisés pour l'enregistrement qu'après qu'il ne reste plus un seul bloc sur le disque au moins une fois dans lequel les données ont été écrites. Bien sûr, en réalité, tout est beaucoup plus compliqué, mais le sens ne change pas.

Et ici, une autre remarque importante doit être faite concernant les produits Western Digital. Lorsque nous avons décidé de développer le marché des SSD, nous pouvions procéder de deux manières: acheter de la mémoire et des contrôleurs auprès de fabricants tiers, en se concentrant uniquement sur le développement et l'optimisation de micrologiciels, ou mettre en place une production à cycle complet. Exécuter un tel projet à partir de zéro ne serait pas pratique, et même l'

achat de SanDisk nous

a coûté un joli sou. Mais les fonds investis ont battu leur plein: en contrôlant la production de puces, nous avons eu l'opportunité d'adapter les microprogrammes aux caractéristiques des microcircuits.

Il faut comprendre que l'écriture de bits d'informations dans des cellules de mémoire flash est un processus beaucoup plus compliqué qu'il n'y paraît à première vue: il prend en compte des centaines de paramètres différents, dont les plus importants sont la tension requise pour le transfert de charge et le temps d'enregistrement. Au fur et à mesure que les puces s'usent, leurs caractéristiques physiques changent également: pour un enregistrement des données réussi, moins de tension est requise, et en même temps, le temps nécessaire de son influence sur la cellule est réduit. Dans la plupart des SSD, ces paramètres sont constants, mais dans les SSD Western Digital, au contraire, ils changent dynamiquement à mesure que les cellules s'usent, ce qui permet de maximiser la durée de vie de chacun d'entre eux, minimisant ainsi l'impact négatif sur les structures semi-conductrices.

QLC 3D NAND - mémoire flash de dernière génération

Si vous suivez l'actualité du monde des hautes technologies, vous savez sans doute que Western Digital maîtrise activement la production de mémoire tridimensionnelle de nouvelle génération - QLC 3D NAND (la première annonce a eu lieu en juin 2018). L'acronyme QLC signifie cellule à quatre niveaux. En d'autres termes, 16 niveaux de charge peuvent être stockés dans une cellule, encodant non seulement trois, mais quatre bits d'information. Par rapport à TLC 3D NAND, la densité d'enregistrement en QLC a augmenté de 33%: ainsi, la capacité d'une puce 64 couches est passée à 768 Gbps. Mais ce n'est pas la limite: en août 2018, nous avons commencé la sortie de microcircuits à 96 couches. En augmentant le nombre de couches, nous avons pu obtenir une augmentation de 50% de la capacité et surmonter la barrière de 1 Tbit: de nouvelles puces, appelées 3D NAND BiCS4, peuvent accueillir 1,33 Tbit d'informations, soit environ 166 Go. Il était possible d'atteindre une densité de stockage de données aussi élevée en combinant deux cristaux à 48 couches (c'est aujourd'hui l'approche la plus viable économiquement).

L'augmentation de la capacité est potentiellement capable de réduire les performances des SSD, mais ne vous inquiétez pas: la nouvelle mémoire flash 3D NAND BiCS4 utilise quatre au lieu de deux matrices physiques, ce qui permet d'optimiser la lecture et l'écriture des données en parallélisant les opérations, et ceci, à son tour, Cela aidera à utiliser plus efficacement le cache et à contrôler le niveau d'usure des cellules, tout en maintenant la durée de vie des puces QLC à un niveau comparable aux solutions TLC modernes. Cependant, une description des technologies sous-jacentes à QLC dépasse le cadre de ce document et mérite certainement un article séparé.