Nous continuons à considérer UDB basé sur la documentation propriétaire de Cypress, à savoir des anecdotes utiles liées à Datapath.

Le contenu général du cycle «UDB. Qu'est-ce que c'est? "

Partie 1. Introduction. Pld.Partie 2. Chemin de données.Partie 3. Datapath FIFO.Partie 4. Datapath ALU.Partie 5. Chemin de données. Petites choses utiles. (Article actuel)

Partie 6. Module de gestion et d'état.Partie 7. Module de commande de temporisation et de réinitialisationPartie 8. Adressage UDB21.3.2.6 Prise en charge CRC / PRS

Datapath prend en charge la génération du contrôle de redondance cyclique (CRC) et des séquences pseudo-aléatoires (Pseudo Random Sequence, PRS). Les signaux chaînés sont tracés entre les blocs Datapath pour prendre en charge CRC / PRS de plus de 8 bits.

Le numéro du bit le plus significatif (bit le plus significatif anglais, MSB) du bloc CRC / PRS le plus élevé est sélectionné et tracé (et lié dans une chaîne avec d'autres blocs) aux blocs inférieurs. Après cela, l'opération XOR avec des données d'entrée (données SI) est appliquée au MSB, fournissant un signal de rétroaction (rétroaction, FB). Après cela, le signal de rétroaction est tracé (et connecté en chaîne avec d'autres blocs) aux blocs inférieurs. Cette valeur de rétroaction est utilisée sur tous les blocs pour effectuer l'opération

XOR du polynôme (à partir du registre Data0 ou Data1) avec la valeur actuelle de la batterie.

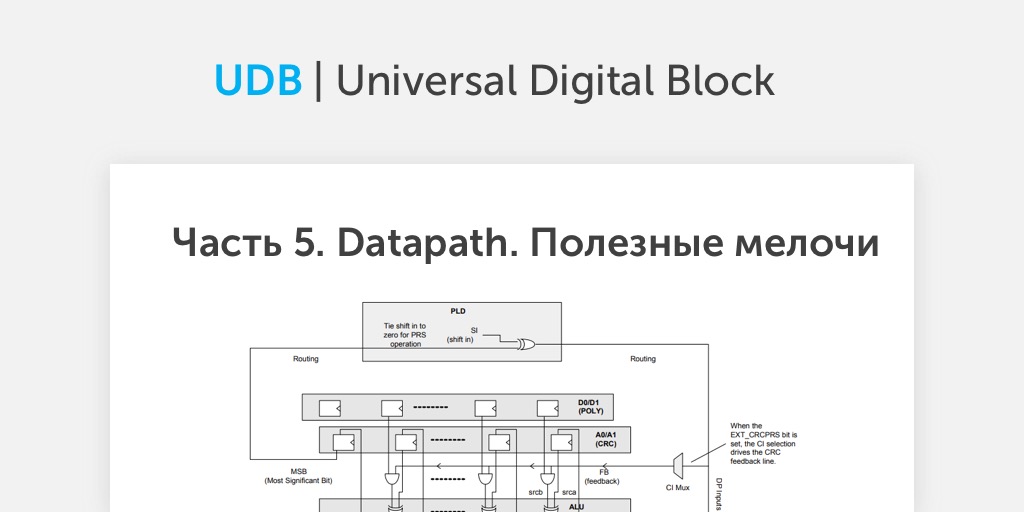

La figure 21-18 montre la configuration structurelle de l'opération CRC. La configuration PRS est identique, mais l'entrée de décalage (SI) est tirée à 0. En mode PRS, D0 ou D1 contient la valeur polynomiale et A0 ou A1 contient la valeur initiale (valeur de départ) et la valeur CRC obtenues après le calcul.

Note du traducteur.Apparemment, il y a une faute de frappe dans la documentation propriétaire de cette phrase, car un nombre aléatoire doit être obtenu en mode PRS. Et les informations sur le CRC se trouvent juste en dessous. Figure 21-18. Structure fonctionnelle du CRC.

Figure 21-18. Structure fonctionnelle du CRC.Pour activer la prise en charge de CRC, vous devez définir le bit

CFB_EN dans la RAM de configuration dynamique sur 1. Ceci active l'opération

ET par rapport à l'entrée SRCB ALU et au signal de rétroaction CRC. Si ce bit est mis à zéro, le signal de rétroaction sera attribué à un, ce qui permet d'effectuer des opérations arithmétiques normales. Le contrôle dynamique de ce bit à chaque cycle vous permet d'alterner les opérations CRC / PRS avec d'autres opérations arithmétiques.

Chaînage CRC / PRS

La figure 21-19 montre un exemple de liaison de CRC / PRS en chaînes entre trois UDB. Ce scénario prend en charge le fonctionnement en modes avec une résolution de 17 à 24 bits. Les bits de liaison de contrôle dans les chaînes sont définis en fonction de la position du chemin de données dans la chaîne (voir figure).

Figure 21-19. Liaison de chaîne de CRC / PRS.

Figure 21-19. Liaison de chaîne de CRC / PRS.Comment le signal de rétroaction CRC / PRS (cfbo, cfbi) est connecté dans une chaîne:

- Si le bloc sélectionné est le plus jeune, le signal de retour sur ce bloc est généré à partir de la logique intégrée, qui prend l'entrée de décalage vers la droite (monsieur) et effectue une opération XOR sur eux avec le bit le plus significatif. (Dans le cas de PRS, le signal «monsieur» est réglé sur «0»).

- Si le bloc sélectionné n'est pas un bloc d'ordre faible, le bit de configuration CHAIN FB doit être armé et la rétroaction est transmise dans une chaîne à partir du bloc précédent.

Comment la chaîne du signal CRC / PRS MSB (cmsbo, cmsbi):

- Si le bloc sélectionné est haut, le bit de configuration MSB (selon le polynôme sélectionné) est configuré à l' aide des bits de configuration MSB_SEL .

- Si le bloc sélectionné n'est pas haut, le bit de configuration CHAIN MSB doit être armé et le signal MSB sera envoyé le long de la chaîne à partir du bloc suivant.

Spécification polynomiale CRC / PRS

Comme exemple de configuration du polynôme pour l'écriture dans le registre correspondant D0 / D1, considérons le polynôme

CCITT CRC-16 , qui a la forme x

16 + x

12 + x

5 + 1. La méthode pour extraire le format de données du polynôme est illustrée à la figure 21-20. Le terme X0, par définition, est toujours 1, il n'a donc pas besoin d'être écrit. Pour tous les autres membres du polynôme, l'unité est réglée sur les positions nécessaires, comme indiqué sur la figure.

Figure 21-20. Format du polynôme CCITT CRC16.

Figure 21-20. Format du polynôme CCITT CRC16.Veuillez noter que le format du polynôme est légèrement différent du format spécifié dans le format hexadécimal classique. Par exemple, le polynôme

CCITT CRC16 est communément appelé

1021H . Pour le convertir au format requis pour Datapath, vous devez effectuer un décalage vers la droite d'une position et ajouter 1 au bit MSB. Dans ce cas, la valeur polynomiale correcte à écrire en D0 ou en D1 est

8810H .

Exemple de configuration CRC / PRS

Voici une brève description des exigences de configuration du CRC / PRS, à condition que D0 soit un polynôme et que le CRC / PRS soit calculé en A0:

- Choisissez un polynôme approprié (exemple ci-dessus) et écrivez-le à D0.

- Sélectionnez la graine appropriée (par exemple, tous les zéros pour CRC ou tous ceux pour PRS) et écrivez-la dans A0.

- Si nécessaire, configurez le chaînage comme décrit ci-dessus.

- Sélectionnez un élément MSB comme décrit ci-dessus.

- Configurer la RAM dynamique Champs RAM:

a. Sélectionnez D0 comme ALU «SRCB» (source de données ALU B)

b. Sélectionnez A0 comme ALU «SRCA» (source de données ALU A)

c. Sélectionnez

XOR pour le fonctionnement ALU

d. Sélectionnez

SHIFT LEFT pour l'opération SHIFT

e. Sélectionnez

CFB_EN pour activer la prise en charge CRC / PRS.

f. Sélectionnez ALU comme source d'enregistrement A0

Lorsque vous choisissez CRC, vous devez configurer le

décalage dans le champ de

droite pour les données d'entrée et soumettre des données sur cette entrée à chaque étape. Lorsque vous choisissez PRS, vous devez définir le

décalage vers la droite sur 0.

Cette configuration de l'UDB génère le CRC nécessaire ou produit le bit le plus significatif, qui peut être transmis à l'extérieur, en supprimant une séquence pseudo-aléatoire.

Mode externe CRC / PRS

Pour activer le calcul CRC ou PRS externe, vous pouvez spécifier un bit de configuration statique (

EXT CRCPRS ). Comme le montre la figure 21-21, le calcul de rétroaction CRC est effectué dans le bloc PLD. Lorsque le bit est armé, le signal de rétroaction CRC est transmis directement à partir du multiplexeur d'entrée CI (Carry In), en contournant les calculs internes. La figure montre une configuration simple qui prend en charge CRC ou PRS jusqu'à 8 bits. Habituellement, des circuits électroniques intégrés sont utilisés, mais ce paramètre vous permet d'implémenter des configurations plus complexes, par exemple, des fonctions CRC / PRS 16 bits dans un UDB, en utilisant le multiplexage temporel.

Figure 21-21. Mode externe CRC / PRS.

Figure 21-21. Mode externe CRC / PRS.Dans ce mode, le bit

CFB_EN de la RAM de configuration dynamique contrôle également si l'opération

ET est utilisée sur le signal de rétroaction CRC à l'entrée CRCB ALU ou non. Ainsi, comme dans le cas du mode CRC / PRS interne, cette fonction peut, si nécessaire, alterner avec d'autres fonctions.

21.3.2.7 Sorties de chemin de données et multiplexage

Les conditions sont générées à partir des valeurs de déclenchement de la batterie, des sorties ALU et de l'état FIFO. Ces conditions peuvent être transmises via des canaux de traçage numérique à d'autres UDB pour former des demandes d'interruption soit au DMA soit aux «jambes de la puce». 16 conditions possibles sont présentées dans le tableau ci-dessous.

Tableau 21-16. Génération de conditions de chemin de données.

Il existe six sorties de Datapath. Comme le montre la figure 21-22, chaque sortie possède un multiplexeur 16 en 1 qui vous permet de router n'importe lequel des 16 signaux vers n'importe quelle sortie Datapath.

Figure 21-22. Connexions au multiplexeur de sortie.

Figure 21-22. Connexions au multiplexeur de sortie.Comparaisons

Il existe deux comparaisons, dont l'une a des sources fixes (

Comparer 0 ), et l'autre est sélectionnée dynamiquement (

Comparer 1 ). Chaque comparaison possède un registre de masquage statique à 8 bits, permettant des comparaisons dans le champ de bits spécifié. Par défaut, le masquage est désactivé (tous les bits sont comparés) et doit être activé manuellement.

Les entrées Compare 1 sont configurées dynamiquement. Comme indiqué dans le tableau ci-dessous, quatre paramètres de comparaison 1 s'appliquent aux conditions inférieures et égales. Les

bits de configuration

CMP SELA et

CMP SELB déterminent les configurations de comparaison possibles. Les bits RAM de la configuration dynamique spécifient une des configurations (A ou B) à chaque cycle.

Tableau 21-17. Configuration de comparaison.

Compare 0 et

Compare 1 sont associés indépendamment aux conditions générées dans le chemin de données précédent (dans l'ordre de traitement). Le fait de chaîner ou non les comparaisons est spécifié statiquement dans les registres de configuration UDB. La figure 21-23 montre la liaison «égal» à la chaîne de comparaison, ce qui revient à appliquer l'opération

ET à la comparaison «égale» de ce bloc et à l'entrée du bloc précédent.

Figure 21-23. Le lien avec la chaîne de comparaison est "égal".

Figure 21-23. Le lien avec la chaîne de comparaison est "égal".La figure 21-24 montre la liaison avec la chaîne de comparaison la moins importante. Dans ce cas, le résultat de sortie (cl0) pour un bloc donné est généré par le circuit de comparaison «inférieur à» et est inconditionnel. Ce signal est combiné

OU avec le résultat entrant de la chaîne si la condition est égale au bloc actuel et que le mode de liaison est activé.

Figure 21-24. Lien inférieur à

Figure 21-24. Lien inférieur àDétection de tous les zéros et de tous les uns

Chaque batterie a un détecteur de tous les zéros et un détecteur de toutes les unités. Ces conditions peuvent être chaînées statiquement comme indiqué dans les registres de configuration UDB. Le mode de liaison est défini dans les registres de configuration UDB. La liaison dans la chaîne de détection des zéros se fait selon le même concept que la comparaison "égal". Si le chaînage est activé, l'opération

ET est appliquée aux données correctement liées.

Débordement

Un débordement est défini comme une opération de transfert

XOR dans un MSB et un transfert à partir d'un MSB. Les calculs sont effectués avec le MSB actuel, comme indiqué dans les bits

MSB_SEL . Cette condition ne peut pas être enchaînée, cependant, le calcul sera correct si la fonction de capacité totale est effectuée sur le chemin de données supérieur jusqu'à ce que le transfert entre les blocs soit connecté.

21.3.2.8 Chemin de données d'entrées et de sorties parallèles

Comme le montre la figure 21-25, les signaux

Parallel In (PI) et

Parallel Out (PO) offrent une capacité limitée à fournir des données et des ressources de trace à Datapath et à en sortir des données. Les signaux PO sont toujours disponibles pour le traçage en tant que choix d'ALU asrc entre A0 et A1.

Note du traducteur.Il s'agit d'un mécanisme extrêmement important qui permet à UDB de fonctionner non seulement avec des données en série, mais également avec des données parallèles. Pour une raison quelconque, ce document ne le souligne pas, mais vous pouvez le lire en passant dans l'une des notes d'application. Figure 21-25. Signaux de chemin de données d'entrée / sortie parallèle.

Figure 21-25. Signaux de chemin de données d'entrée / sortie parallèle.Pour entrer des données dans l'ALU, vous devez sélectionner

Parallel In . Il existe deux modes: statique et dynamique. En mode statique, le bit

PI SEL convertit la valeur asrc ALU en PI. Le bit

PI DYN est utilisé pour fournir le mode dynamique PI. Lorsqu'il est armé, et à condition également que

PI SEL soit à 0, le multiplexeur PI peut contrôler le bit de commande dynamique

CFB_EN . La fonction principale du bit

CFB_EN est de fournir la fonctionnalité PRS / CRC.

21.3.2.9 Chaînage du chemin de données

Chaque bloc Datapath possède une ALU 8 bits, qui est conçue pour enchaîner les traits d'union, les décalages, capturer les déclencheurs et les signaux conditionnels au Datapath voisin le plus proche pour créer des fonctions arithmétiques et des registres à décalage avec des profondeurs de bits plus élevées. Ces signaux, connectés en chaînes, sont isolés et vous permettent de mettre en œuvre efficacement des fonctions 16-24 et 32 bits en un seul cycle sans course et autres problèmes résultant de retards dans les canaux de trace. De plus, les poignées de chaînage prennent en charge la lecture atomique des batteries dans les blocs liés. Comme le montre la figure 21-21, tous les signaux conditionnels et de capture générés sont connectés dans une chaîne qui se déplace du plus jeune au plus ancien bloc. Un décalage vers la gauche est également effectué de junior à senior. Un décalage vers la droite est effectué du plus vieux au plus jeune. Le signal de chaînage CRC / PRS pour la rétroaction est acheminé de haut en bas, et la sortie MSB est envoyée de haut en bas.

Figure 21-26. Chaîne d'enfilage Datapath.

Figure 21-26. Chaîne d'enfilage Datapath.21.3.2.10 Configuration dynamique de la RAM

Chaque chemin de données contient une RAM de configuration dynamique avec 8 mots de 16 bits chacun (voir la figure 21-27). Le but de cette RAM est de contrôler les bits de la configuration du chemin de données à chaque cycle, en fonction de l'horloge sélectionnée pour ce chemin de données. La RAM possède des ports de lecture et d'écriture synchrones pour le téléchargement des configurations via le bus système.

Pour sortir rapidement ces mots de 16 bits vers Datapath, un port de lecture asynchrone supplémentaire est fourni en tant que bits de contrôle. Les entrées d'adresse asynchrones sont sélectionnées par les multiplexeurs à partir des entrées Datapath, qui peuvent être prises à partir de tous les signaux possibles, y compris les jambes de microcircuit, les sorties PLD, les sorties de l'unité de contrôle ou toute sortie Datapath.

Le but principal d'un port de lecture asynchrone est de fournir un décodage rapide des bits de commande Datapath en un seul cycle.

Figure 21-27. Configuration d'E / S RAM.

Figure 21-27. Configuration d'E / S RAM.Les champs du mot RAM de la configuration dynamique sont indiqués dans les tableaux suivants avec une description de l'utilisation de chaque champ.

Tableau 21-18. Référence de configuration dynamique.

(a. - Pour les champs CI, SI et CMP, les champs RAM vous permettent de sélectionner l'une des deux options prédéfinies. Voir la configuration du registre statique).

À suivre ...