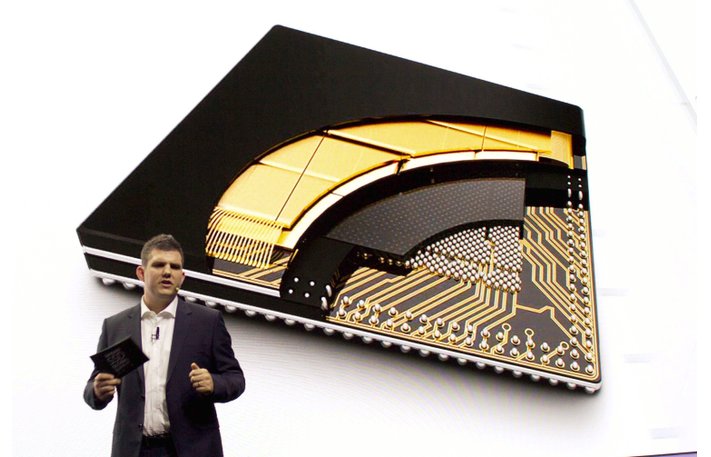

Intel Foveros 3D

Intel Foveros 3DÉtant donné que la loi de Moore ne s'applique plus, les concepteurs de puces doivent rechercher d'autres moyens d'améliorer les performances. Une technologie appropriée pour cela est appelée empilement de puces 3D. Il s'agit d'une architecture de pile en trois dimensions de puces, dans le développement de laquelle Intel est le leader. Il y a deux mois, Intel a présenté l'architecture

Foveros 3D : une structure tridimensionnelle qui comprend un processeur de 10 nm, une puce d'E / S et des connexions électriques verticales TSV (Through Silicon Via) au centre de la puce, et une puce de mémoire au-dessus de la puce entière.

Lors de la conférence sur le calcul haute performance de Rice Oil and Gas HPC, AMD a

assuré qu'il travaillait sur sa propre version de l'architecture de la puce 3D.

Forrest Norrod, vice-président directeur et directeur général, a déclaré que la société développait plusieurs technologies pour augmenter les retours et contourner les problèmes associés à la fin de la loi de Moore et aux conséquences de l'arrêt de la croissance de la densité des transistors et de la fréquence d'horloge. Ce sont des conséquences inévitables lorsque les fabricants approchent de la limite où la taille du transistor n'est que de quelques atomes (la taille d'un atome de silicium est de 0,2 nanomètre). La croissance de la puissance informatique ces dernières années n'est pas tant due à une augmentation de la vitesse de calcul, mais à une augmentation du parallélisme.

Comme d'autres sociétés, AMD a été confronté à une limitation de la surface de la puce d'environ 700 mm² et est contraint de développer une architecture 3D. La société adopte déjà cette approche en plaçant la mémoire HBM2 à côté du substrat GPU, c'est-à-dire dans le même cas que le processeur. Mais à l'avenir, la société prévoit de passer à un empilement 3D plus avancé.

Norrod a déclaré qu'AMD travaille à placer SRAM et DRAM directement sur les composants informatiques (tels que les processeurs et les GPU) pour fournir encore plus de bande passante et de performances.

Samsung Polaris

Samsung PolarisCette approche diffère des implémentations habituelles de package sur package (PoP), qui mettent simplement deux boîtiers finis l'un sur l'autre, comme Norrod l'a montré en utilisant la puce Samsung Polaris comme exemple. Dans cet exemple, le boîtier DRAM est connecté via deux rangées supplémentaires de connecteurs BGA qui entourent la puce de base. Ces connecteurs BGA transfèrent des données entre deux puces. Comme pour toute conception standard, la logique est au bas de la pile en raison du besoin de plus de connecteurs, mais les deux cristaux ne sont pas directement connectés. Ainsi, l'approche PoP fournit une densité maximale, mais ce n'est pas l'option la plus rapide.

Dans un véritable empilement 3D, deux puces (dans ce cas, la mémoire et le processeur) sont situées l'une au-dessus de l'autre et connectées par des connexions verticales TSV qui les interfacent directement. Ces connexions TSV transfèrent les données entre les cristaux à la vitesse la plus élevée possible et sont généralement situées au centre de la puce, comme nous l'avons vu avec Intel Foveros 3D. Cette association directe améliore les performances et réduit la consommation d'énergie (tous les mouvements de données nécessitent de l'énergie, mais les connexions directes optimisent le processus). L'empilement 3D augmente également la densité.

Norrod n'est pas entré dans les détails des projets en cours de développement, mais cela pourrait s'avérer être un changement fondamental dans la conception du processeur AMD.

La nouvelle technologie Intel Foveros 3D peut s'avérer être un moment déterminant pour l'industrie, il n'est donc pas surprenant d'entendre qu'AMD va dans cette direction,

écrit Tom's Hardware .

Jusqu'à présent, il n'y a pas de détails techniques sur la technologie d'empilage 3D d'AMD, à part ce que Forrest Norrod a déclaré lors d'une présentation intitulée Working Beyond Moore's Law, voir la vidéo ci-dessous.

Quelles autres alternatives existe-t-il pour revenir à la courbe de croissance exponentielle prédite par Gordon Moore? Il n'y a pas de réponse unique à cette question. L'industrie des semi-conducteurs expérimente des matériaux qui peuvent être utilisés à la place du silicium. Certains matériaux semi-conducteurs III-V peuvent fonctionner

à des tensions plus basses et à des fréquences plus élevées que le silicium , mais ils ne rendent pas les atomes plus petits ou plus légers. Des restrictions physiques s'appliquent toujours.

La question reste de savoir comment les futures puces 3D vont refroidir. Comment refroidir efficacement une telle puce lorsque l'énergie est distribuée à travers elle? Le microcircuit ne pourra pas transférer de puissance à tous les circuits simultanément sans surchauffe. Elle devra probablement garder certaines pièces déconnectées la plupart du temps et alimenter chaque pièce uniquement pendant l'utilisation.