Linux Foundation a ouvert une nouvelle direction - CHIPS Alliance. Dans le cadre de ce projet, l'organisation développera un système d'instruction RISC-V gratuit et des technologies pour créer des processeurs basés sur celui-ci. Nous dirons plus en détail ce qui se passe dans ce domaine.

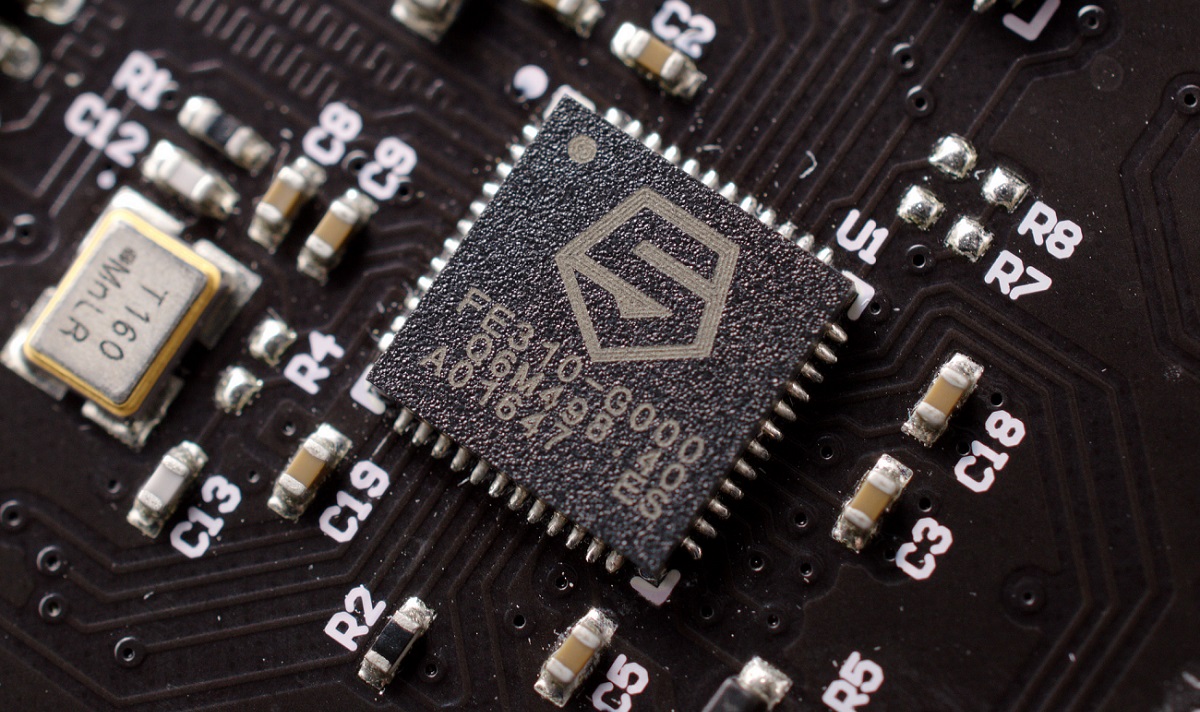

/ photo Gareth Halfacree CC BY-SA

/ photo Gareth Halfacree CC BY-SAPourquoi l'Alliance CHIPS est apparue

Les correctifs qui protègent contre Meltdown et Spectre, dans certains cas,

réduisent les

performances du serveur de 50%. Dans le même temps, de nouvelles variantes de vulnérabilités associées à l'exécution spéculative de commandes apparaissent toujours. L'un d'eux

est devenu connu début mars - des experts en sécurité de l'information l'ont surnommé Spoiler. Cette situation affecte la

discussion sur la nécessité de revoir les solutions matérielles existantes et les approches de leur développement. En particulier, Intel

prépare déjà une nouvelle architecture pour ses processeurs, non concernés par Meltdown et Spectre.

Ils ne se sont pas écartés de la Linux Foundation. L'organisation a lancé sa propre initiative - l'Alliance CHIPS - dont les membres seront engagés dans le développement de processeurs basés sur RISC-V.

Quels projets se développent déjà

La liste des membres de l'Alliance CHIPS comprend Google, Western Digital (WD) et SiFive. Chacun d'eux a présenté ses propres développements. Parlons de certains d'entre eux.

RISCV-DV

Le géant de l'informatique de recherche a été transféré sur la plate-forme open source pour tester les processeurs basés sur RISC-V. La solution

génère aléatoirement

des commandes qui

vous permettent de vérifier l'opérabilité de l'appareil: test des processus de transition, piles d'appels, registres

CSR , etc.

Par exemple,

voici une classe chargée de réaliser un simple test d'instructions arithmétiques:

class riscv_arithmetic_basic_test extends riscv_instr_base_test; `uvm_component_utils(riscv_arithmetic_basic_test) `uvm_component_new virtual function void randomize_cfg(); cfg.instr_cnt = 10000; cfg.num_of_sub_program = 0; cfg.no_fence = 1; cfg.no_data_page = 1'b1; cfg.no_branch_jump = 1'b1; `DV_CHECK_RANDOMIZE_WITH_FATAL(cfg, init_privileged_mode == MACHINE_MODE; max_nested_loop == 0;) `uvm_info(`gfn, $sformatf("riscv_instr_gen_config is randomized:\n%0s", cfg.sprint()), UVM_LOW) endfunction endclass

Selon

les développeurs, la plate-forme diffère des analogues en ce qu'elle vous permet de vérifier systématiquement tous les composants de la puce, y compris le bloc de mémoire.

Protocole OmniXtend

Il s'agit d'un protocole réseau de WD qui assure la cohérence du cache lors du transfert de données via Ethernet.

OmniXtend vous permet d'échanger des messages directement avec le cache du processeur et est utilisé pour connecter différents accélérateurs: GPU ou FPGA. Il convient également pour créer des systèmes basés sur plusieurs puces RISC-V.

Le protocole est déjà pris en charge par les

puces SweRV axées sur le traitement des données dans les centres de données. SweRV est un processeur superscalaire 32 bits à double pipeline basé sur une technologie de processus de 28 nanomètres. Chaque pipeline possède neuf niveaux, ce qui permet de charger et d'exécuter plusieurs commandes simultanément. L'appareil fonctionne à une fréquence de 1,8 GHz.

Générateur de puces de fusée

Une solution de SiFive, fondée par les développeurs de la technologie RISC-V.

Rocket Chip est un générateur de cœur de processeur RISC-V dans Chisel. Il

s'agit d'une collection de bibliothèques paramétrées utilisées pour créer

SoC .

Quant à

Chisel , il s'agit d'un langage de description matérielle basé sur Scala. Il génère du code de bas niveau sur Verilog,

adapté au traitement sur ASIC et FPGA. Ainsi, il permet l'utilisation des principes OOP dans le développement de

RTL .

Perspectives de l'Alliance

Les experts disent que l'initiative Linux Foundation rendra le marché des processeurs plus démocratique et ouvert à de nouveaux acteurs. IDC

note que la popularité croissante de ces projets aura un effet positif sur le développement des technologies d'apprentissage automatique et des systèmes d'IA en général.

/ photo Fritzchens Fritz PD

/ photo Fritzchens Fritz PDLe développement de processeurs open source réduira également le coût de conception de puces personnalisées. Cependant, cela ne se produira que si la communauté Linux Foundation parvient à attirer suffisamment de développeurs.

Projets similaires

D'autres organisations développent des projets liés au matériel ouvert. Un exemple serait le consortium CXL, qui a introduit la norme Compute Express Link à la mi-mars. La technologie est un analogue d'OmniXtend et connecte également CPU, GPU, FPGA. Pour l'échange de données, la norme utilise le bus PCIe 5.0.

Un autre projet impliqué dans le développement de technologies de processeur est MIPS Open, qui est apparu en décembre 2018. L'initiative a été créée par la startup Wave Computing. Les développeurs prévoient d'

ouvrir les derniers jeux d'instructions MIPS 32 bits et 64 bits à la communauté informatique. Le démarrage du projet

est attendu dans les prochains mois.

En général, l'approche open source est généralement acceptée non seulement pour les logiciels, mais aussi pour le matériel. Ces projets sont soutenus par de grandes entreprises. Par conséquent, nous pouvons nous attendre à ce que dans un avenir proche davantage d'appareils apparaîtront sur le marché, qui sont basés sur des normes matérielles ouvertes.

Nouveaux articles de notre blog d'entreprise:

Messages de notre chaîne Telegram: