Et si le TFT n'était jamais inventé? LCD matrice CSTN

Entrée

Lorsque les moniteurs CRT ont prévalu, l'argument suivant a été avancé en leur faveur: malgré toutes les améliorations, les écrans LCD ne surclasseront jamais les écrans à tube en qualité d'image. Comme précédemment, ils ne trouveront d'application que là où l'efficacité énergétique et une faible épaisseur sont nécessaires [1]. Des décennies ont passé et nous savons maintenant si les partisans de cet argument avaient raison. Mais aujourd'hui, il est intéressant de regarder les LCD de l'époque: sont-ils vraiment de si mauvaise qualité? À quoi ressemble la matrice CSTN en 2019?

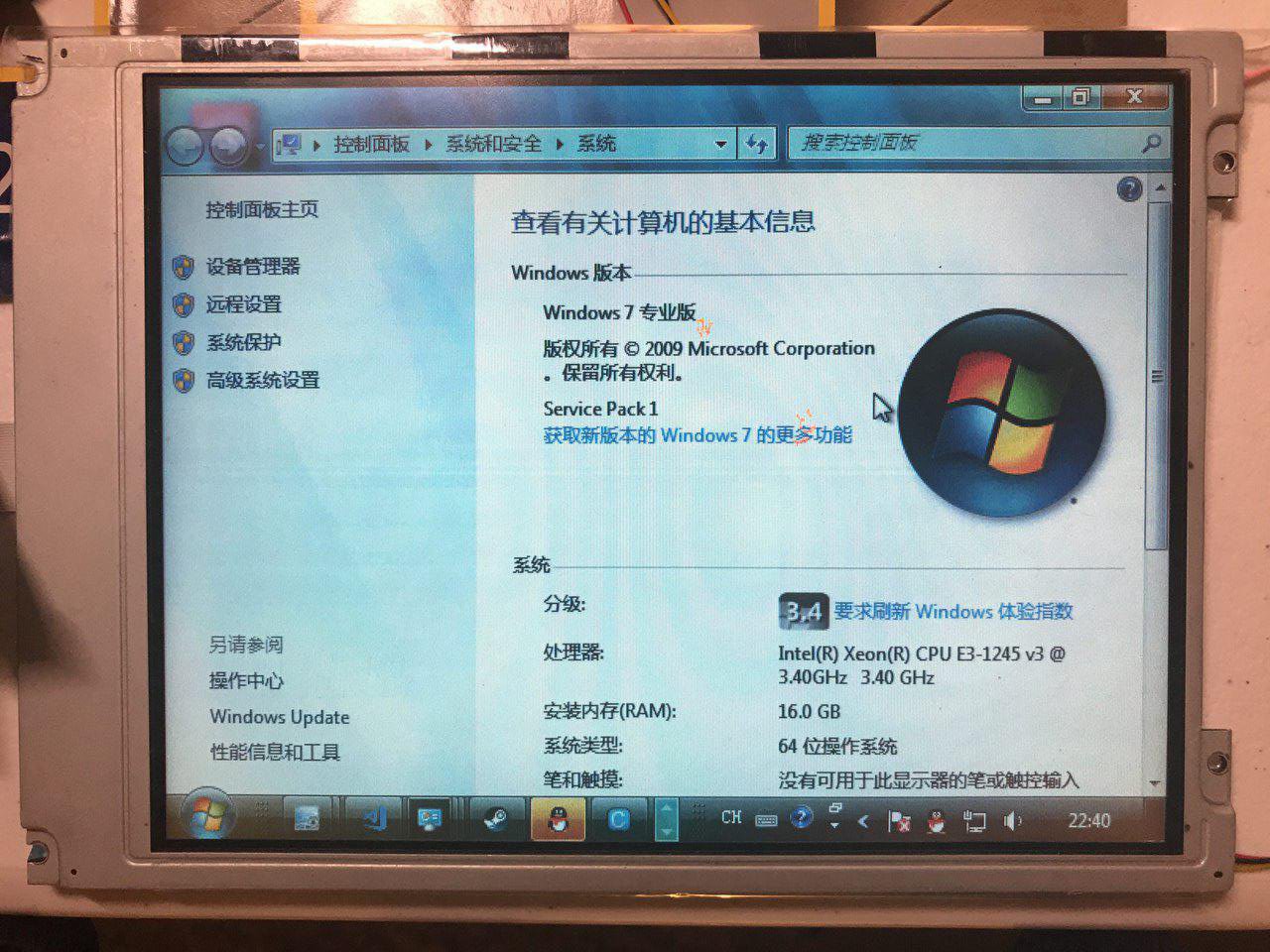

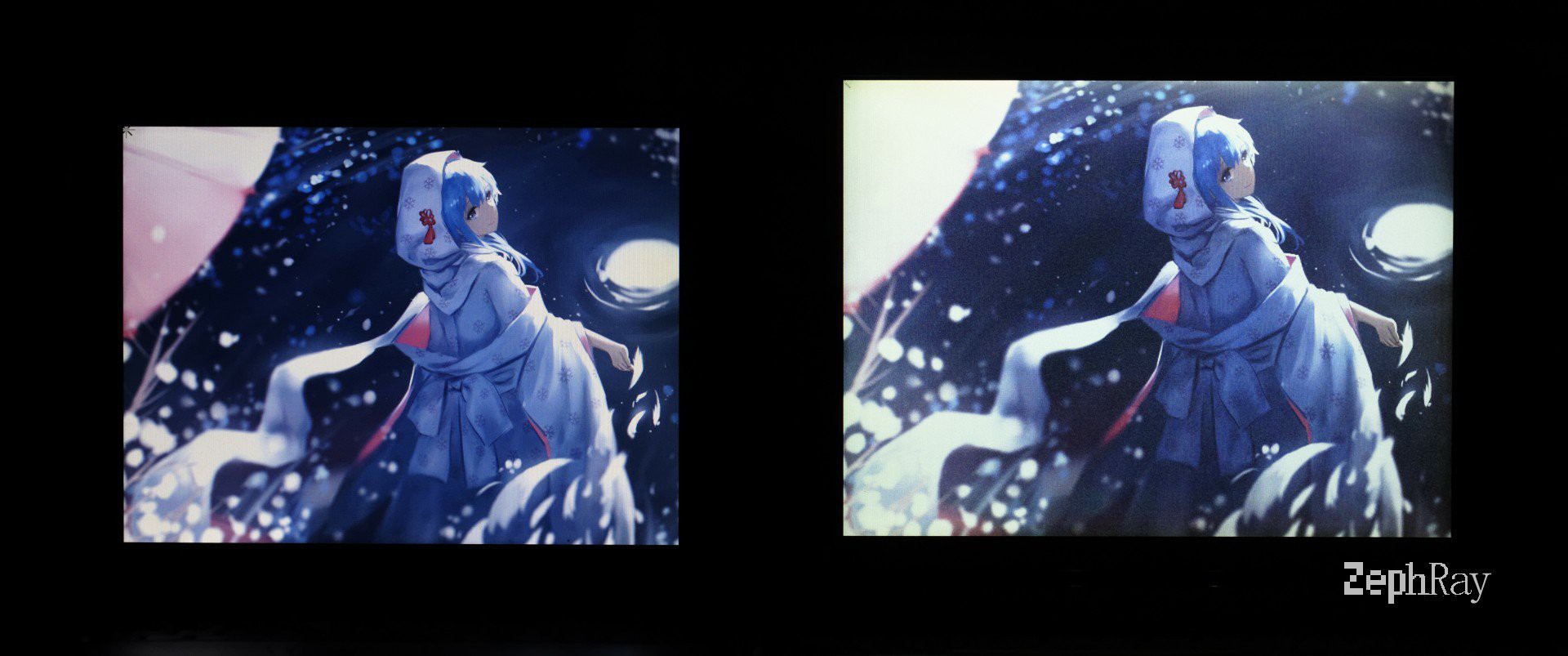

TFT gauche, CSTN droit, les deux écrans des années 90

TFT gauche, CSTN droit, les deux écrans des années 90LCD au siècle dernier

Avant de passer au TFT, diverses technologies d'affichage étaient utilisées dans les ordinateurs portables. Au début, ils utilisaient les mêmes moniteurs CRT que sur les ordinateurs de bureau, seulement des plus petits. Par exemple, dans Compaq Portable (1983), IBM 5155 (1984) ou Commodore SX-64 (également 1984).

IBM 5155, auteur: Soupmeister, sous licence: CC-BY-SA-2.0, d'ici

IBM 5155, auteur: Soupmeister, sous licence: CC-BY-SA-2.0, d'iciPorter un tel PC partout avec vous était difficile, une chose complètement différente - un ordinateur portable avec un TN-LCD (twist nematic), par exemple, IBM 5140 (1986), Toshiba T1000 (1987). Ces écrans ont un contraste et un angle de vision bas.

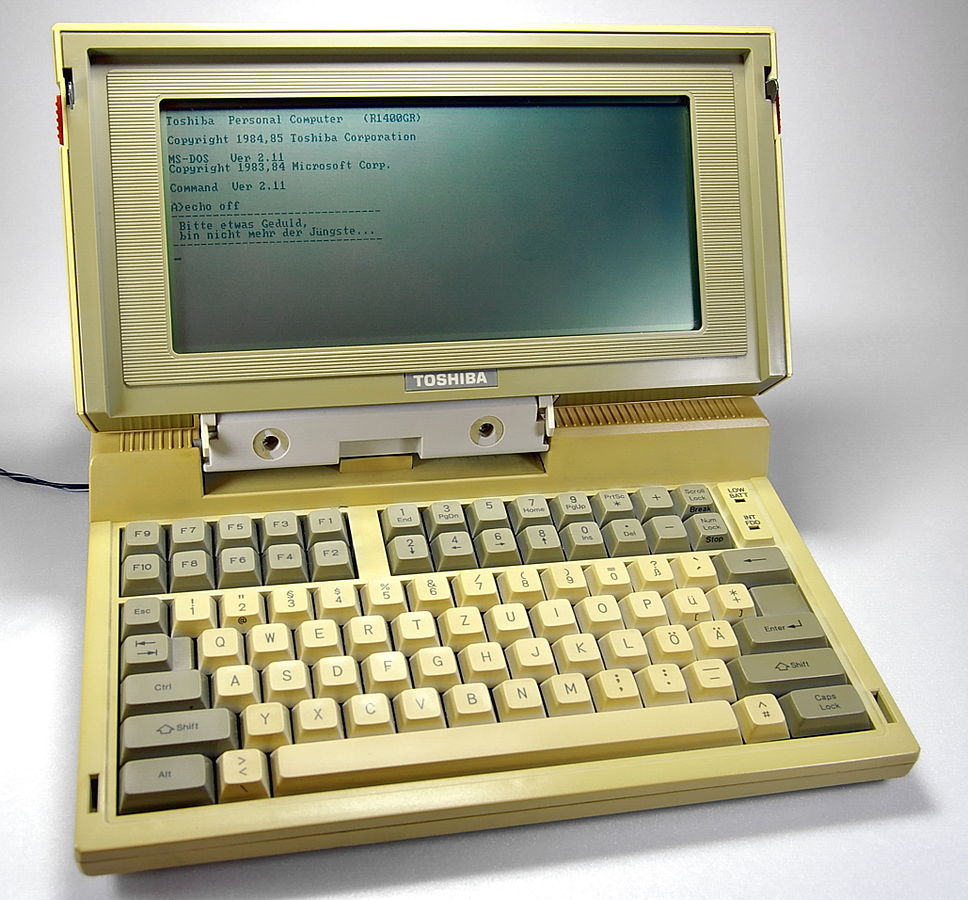

Toshiba T1100 avec écran TN monochrome, auteur: Johann H. Addicks, licence: GFDL, d' où le lien est rompu, dans l'original aussi

Toshiba T1100 avec écran TN monochrome, auteur: Johann H. Addicks, licence: GFDL, d' où le lien est rompu, dans l'original aussiCertains fabricants ont expérimenté des matrices à décharge, comme Toshiba T3200 (1987) et IBM PS / 2 P70 (1991) ont vu le jour. Ils fournissaient un contraste élevé et plusieurs gradations de luminosité de la lumière rouge-orange, mais ils étaient assez chers. Enfin, des STN-LCD (supertwist nematic) ont été développés, comme par exemple dans Electronics MC1504 et son prototype Toshiba T1100. Le contraste était bien meilleur - de 1: 5 à 1:50, et quelques gradations de luminosité étaient suffisantes pour les applications professionnelles (utiliser un ordinateur portable au quotidien était encore trop cher). Mais que se passe-t-il si l'utilisateur veut une image couleur? Dans ce cas, on lui a proposé deux technologies: TFT et CSTN (color supertwist nematic). Le premier ordinateur portable avec TFT - NEC PC9801NC - a été introduit en 1990, la qualité d'image pour ces années-là était avant tout une louange, mais il coûtait "un tel jouet" est beaucoup plus cher que les autres ordinateurs portables si chers. Eh bien, un affichage CSTN est juste un affichage STN, sur lequel un filtre est superposé. Pendant longtemps, les ordinateurs portables ont utilisé des matrices des deux types. Et dans le métro de New York, les moniteurs CSTN fonctionnent toujours.

L'un d'eux, source: Transit + PLUS

L'un d'eux, source: Transit + PLUSCstron

L'auteur a voulu regarder l'affichage du CSTN. Comment? Pour commencer, il suffit d'acheter un vieil ordinateur portable et de l'utiliser. Il s'est avéré être un processeur AMD 5x86-P133. C'est-à-dire que la chose la plus dynamique que vous pouvez exécuter est les jeux DOS (eh bien, il tirera MPEG1 dans le programme QV - traducteur). Bien sûr, les jouer est génial, mais je voulais voir à quoi ressemble YouTube, par exemple, ou un jeu moderne sur un tel écran - mais c'est impossible.

Ou?

En général, vous devez en quelque sorte y ajouter une entrée VGA ou HDMI - et vous pouvez envoyer un signal à partir de quelque chose de moderne. Les écrans TFT des ordinateurs portables sont donc souvent refaits en moniteurs. Achetez simplement une planche qui correspond à la matrice - et vous avez terminé. Et vous pouvez créer votre propre préfixe sur le FPGA, qui convertit un signal VGA ou HDMI en un flux de données de pixels.

Il était une fois des cartes produites pour convertir des matrices CSTN en moniteurs VGA, mais cela ne se trouve plus. Mais vous pouvez adapter la carte de débogage pour FPGA ML505 pour cela.

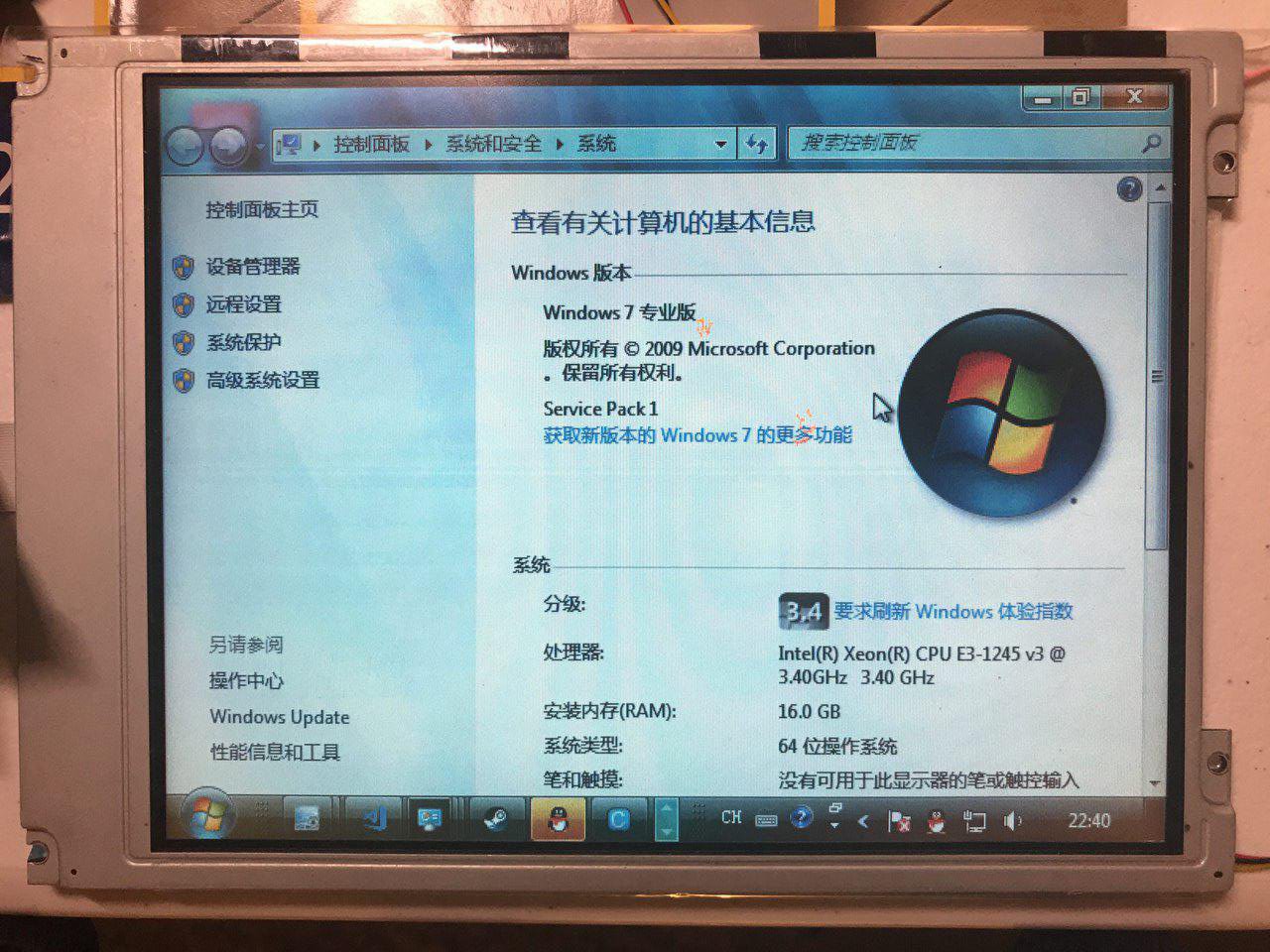

Le résultat final. Il est assez inhabituel d’observer cela sur un écran CSTN: 16 Go de RAM.

Le résultat final. Il est assez inhabituel d’observer cela sur un écran CSTN: 16 Go de RAM.Gestion matricielle

Commençons par les bases. Comme tout affichage matriciel, l'affichage CSTN comporte des lignes et des colonnes. Avez-vous déjà contrôlé une matrice LED à partir d'un microcontrôleur? C'est la même chose ici, mais les tensions sont variables. Vous devez appliquer certains signaux aux lignes et colonnes sélectionnées et non sélectionnées - et le pixel à l'intersection de la ligne et de la colonne sélectionnées montrera ce dont vous avez besoin. La forme des signaux est très complexe, la valeur carrée moyenne de la tension, le déphasage entre les tensions sur la ligne et la colonne, et le décalage ... Et donc, pixel par pixel, une image se forme.

Heureusement, les FPGA ne sont pas tenus de générer tous ces signaux, et même sur un si grand nombre de lignes. Tout cela se fait par le module intégré à l'écran. Là, le convertisseur d'impulsions augmente la tension constante, il traverse le diviseur et le répéteur, de sorte que la tension de polarisation est obtenue. Les pilotes de ligne et de colonne transforment cette tension en une variable de la forme requise. Il suffit de soumettre un flux de données d'état des pixels au module d'affichage.

Sur un TFT-LCD avec une interface DPI (interface parallèle numérique), toutes les données concernant un pixel arrivent à la fois en un seul cycle. Sur la ligne de synchronisation horizontale et de trame, des impulsions sont reçues après chaque ligne et trame, respectivement. Les pixels sont simplement transmis en continu ligne par ligne, image par image. Si la transmission plein format prend 1/60 s, la fréquence de rafraîchissement est de 60 Hz. La largeur du bus de données est égale à la profondeur de couleur en bits, généralement 16 (5 bits pour le rouge et le bleu, 6 pour le vert), 18 (6 bits pour chaque couleur) ou 24 (8 bits pour chaque couleur). LVDS est la même chose, seuls les bits ne sont pas transmis en parallèle, mais séquentiellement en paires différentielles, mais en MIPI DSI ils sont également combinés en paquets. Le bus SPI / i80 vous permet de transmettre diverses commandes au contrôleur, et cela, en les exécutant, génère des signaux pour DPI ou une interface similaire. Ce qui, à son tour, rappelle quelque peu le VGA, seules les données sur la luminosité de chacune des couleurs sont reçues non pas en analogique, mais sous forme numérique. Il existe des convertisseurs VGA en DPI et vice versa. Les cartes sont très pratiques, vous permettant de recevoir un signal VGA du Raspberry Pi, bien qu'au départ cet ordinateur ne produise que du HDMI et de la vidéo composite.

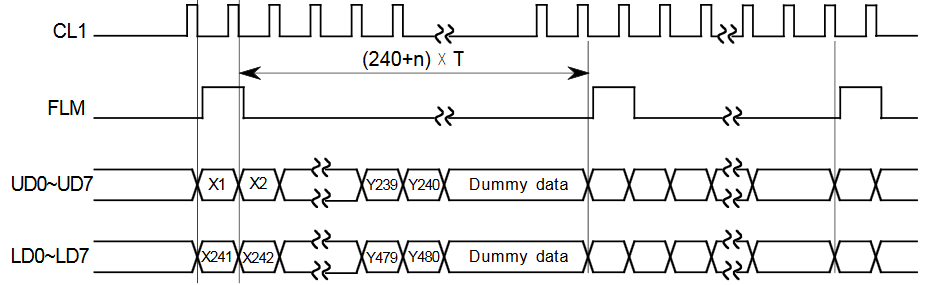

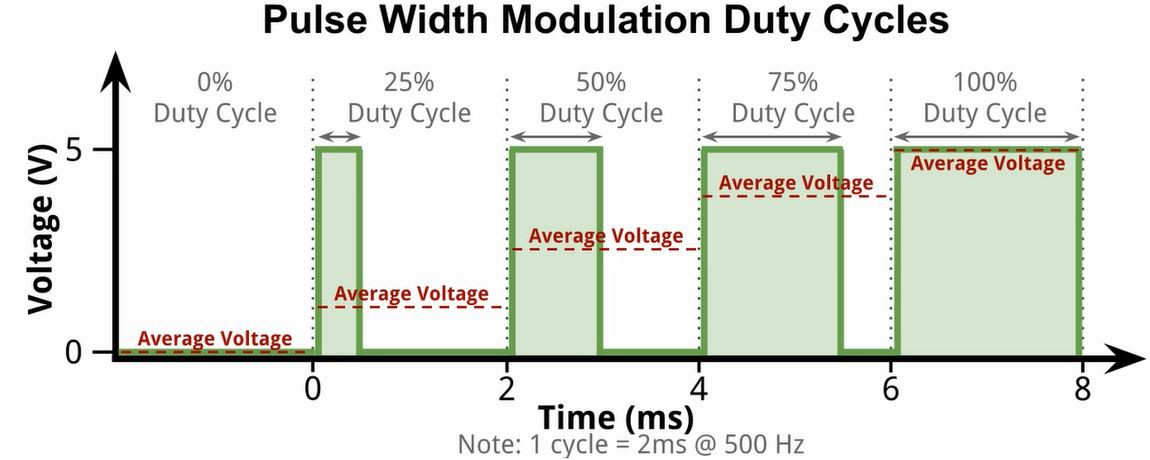

Des signaux très similaires à ceux fournis à une matrice TFT avec une interface DPI doivent être fournis au module d'affichage de la matrice CSTN. La fiche technique du SX21V001 [2] montre comment contrôler un écran CSTN avec une résolution de 640x480:

Cela montre le transfert de la trame entière. Le signal arrive sur la ligne CL1 après chaque ligne, sur FLM après chaque trame. Et il y a un bus de données de 16 lignes. En fait, une erreur a été commise sur cette figure: lors de la transmission des première et deuxième lignes, les données Y1 et Y2, et non X1 et X2, mais Y140 et Y242, respectivement, sont reçues sur les lignes UD0-UD7. Ici U et L sont respectivement supérieur et inférieur, c'est-à-dire que l'affichage se compose de deux matrices avec une résolution de 640x240, situées l'une au-dessus de l'autre. Le voici, le mystérieux «double balayage» d'une vieille publicité pour ordinateur portable, d'où vient une bande horizontale sur tout l'écran. Pour les affichages STN et CSTN, le contraste est inversement proportionnel au nombre de lignes, donc cette séparation permet de l'augmenter. Mais ce n'est pas la seule façon dont ils diffèrent dans la façon dont ils sont contrôlés à partir du TFT.

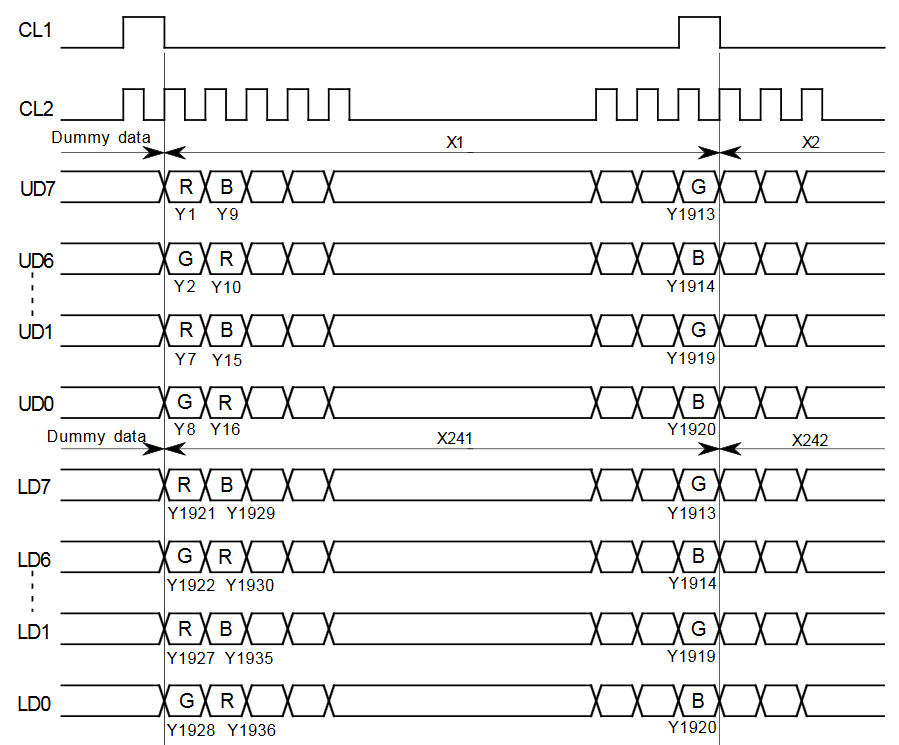

On ne sait pas pourquoi l'axe horizontal a été appelé Y ... Mais en tout cas, CL2 ici est une ligne pour fournir des impulsions d'horloge qui commutent les pixels. Mais sur les bus UD et LD en un cycle, non pas des données sur un pixel multi-bits, comme dans TFT, sont transmises, mais des données sur plusieurs pixels à la fois, trois bits chacune. Un bit par couleur, trois bits par pixel - huit couleurs au total.

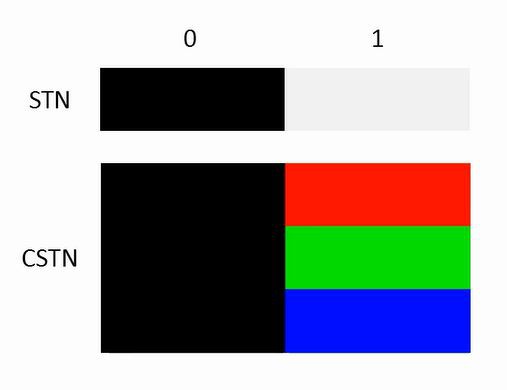

Mais comment ça? Il est clair que les écrans CSTN ont peu de couleurs, par exemple 4096 ou 32768, mais pas 8. Il s'avère que PWM est appliqué ici. Les LED sont contrôlées de cette façon, ce qui signifie que les pixels LCD sont possibles. Vous avez besoin, par exemple, d'une luminosité de 50% - allumez le pixel dans les images paires et désactivez-le dans les images impaires. Cette méthode est appelée FRC (frame rate control), mais PWM dans ce contexte est appelé contrôle de la luminosité des pixels de la même manière, mais dans deux images ou plus, mais une seule. FRC implémente un périphérique externe et PWM implémente des puces de module d'affichage, si cette fonction est prise en charge. L'auteur ne connaît pas les écrans CSTN avec PWM, mais il suggère qu'il s'agit de matrices de type HPA. Dans tous les cas, comme PWM n'est pas disponible, la profondeur de couleur nécessaire peut être obtenue en utilisant FRC.

Le scintillement en sera le prix, donc des fréquences d'images monstrueuses (par rapport à TFT) peuvent être trouvées dans les écrans CSTN. Par exemple, ce module avait initialement 120 Hz, et l'auteur l'a overclocké à 240.

Comment il a été mis en œuvre

Le développeur a rencontré plusieurs difficultés à la fois:

- le signal d'entrée a une fréquence d'images de 60 Hz, il doit être doublé voire quadruplé

- dans le signal d'entrée, le cadre n'est pas divisé en moitiés supérieure et inférieure de 640x240 pixels chacune, mais ici, il est nécessaire de diviser

- vous devez également implémenter FRC, sinon la profondeur de couleur sera de 3 bits par pixel

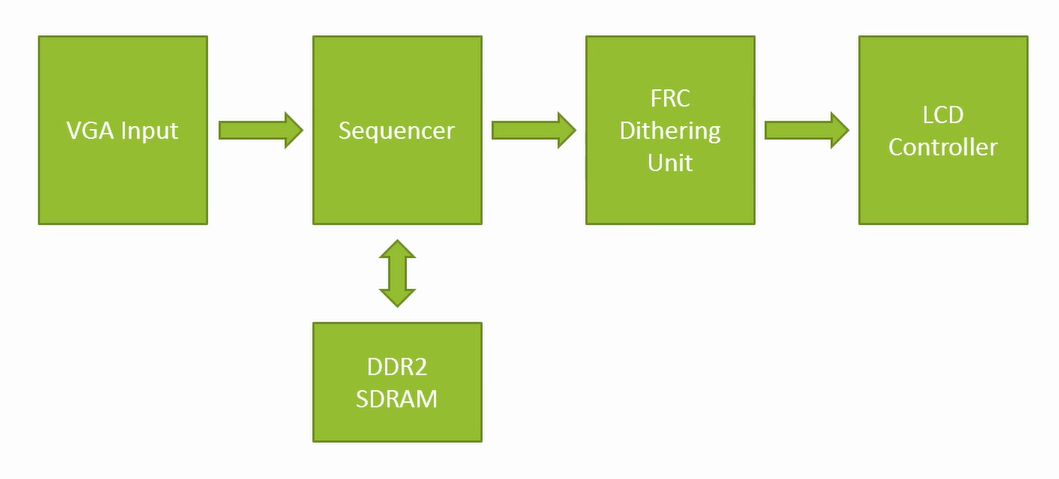

Les deux premiers points signifient qu'un framebuffer est nécessaire, et pas un simple, mais un à deux ports. Eh bien, la troisième tâche est résolue en utilisant GLDP LUT (table de recherche de modèle d'affichage de niveau de gris) [3]. La table de recherche comporte deux types de données d'entrée: la couleur à afficher et l'état du compteur de trames. Et un type de sortie: ces trois bits qui doivent être soumis aux sous-pixels d'un pixel donné à un moment donné. Par conséquent, les nœuds suivants seront requis:

La première chose à faire est de remplir tout l'écran avec de la couleur. A ce stade, il n'est pas nécessaire de savoir où se trouve le pixel, il suffit de s'assurer que le module d'affichage délivre les signaux de forme nécessaires à la matrice. Le code pour remplir le FPGA est

ici .

Essayez maintenant de faire ressortir quelque chose, et avec une luminosité incomplète également. Recherche de tables de recherche FRC pour minimiser le scintillement. L'auteur a proposé deux tableaux appliqués aux pixels en damier. Par conséquent, tous les deux pixels voisins scintillent de manière asynchrone. Le code est

ici .

Donc, nous avons déjà «appris» à la carte à afficher l'image, la prochaine chose qui sera nécessaire est un framebuffer. À 640x480 et 5 bits pour chacune des couleurs, son volume sera d'environ 600 kilo-octets. Pas beaucoup, mais tellement dans les FPGA. Eh bien, la carte dispose de RAM comme DDR2 et Xilinx MIG pour le contrôler. Deux FIFO sont implémentés, l'un pour la lecture et l'autre pour l'écriture. L'arbitre décide si le prochain échange de données avec DDR2 est lu ou écrit. Il y a deux tampons, l'enregistrement va dans l'un, en lisant dans l'autre, et lors du changement d'images, ils changent de place. Le code d'arbitre est

ici .

Il reste à implémenter la capture vidéo, dans l'un des projets précédents l'auteur a déjà un temps de fonctionnement similaire, après raffinement, le code du convertisseur de VGA en DPI est devenu

comme ça .

Et que s'est-il passé?

Regardez-le!

Il s'agit du troisième projet FPGA pour l'auteur, il était intéressant de travailler avec Xilinx MIG et DDR2, ainsi qu'avec un simple convoyeur. Un meilleur FRC avec modulation delta sigma est prévu, ainsi que des expériences avec des panneaux CSTN ultérieurs utilisant la technologie Sharp de HPA (High Performance Addressing).

Merci de votre attention!

Les sources

1. Li, W. et Guo, Q. (2000). Technologie d'application d'affichage à cristaux liquides. Pékin: Presse de l'industrie électrique.

2. HITACHI (1999). Spécifications d'acceptation du client SX21V001-Z4.

3. Hsueh, Y. et Lee, J. (2008). Méthode d'amélioration de l'image pour le contrôleur de fréquence d'images LCD. 2008 Symposium international de l'IEEE sur l'électronique grand public. doi: 10.1109 / isce.2008.4559534