L'autre jour, la

station automatique japonaise Hayabusa-2 a largué une bombe sur l'astéroïde Ryugu . Le vaisseau spatial est contrôlé par un système stable aux radiations basé sur une puce HR5000 (JAXA2010 / 101) avec un cœur de processeur MIPS 5Kf 64 bits. L'ordinateur de bord exécute le système d'exploitation en temps réel uITRON, l'une des familles RTOS standard de TRON, qui est apparu au Japon dans les années 80

et mérite un poste séparé .

Dans cette note, je décrirai brièvement ce qui est inclus dans le SoC HR5000 et son cœur de processeur, je montrerai des photos de deux des principaux développeurs des lignes MIPS 4K et 5K, et dirai également comment vous pouvez jouer à la maison sur le FPGA avec le «descendant d'un jeune frère» de cet ordinateur - Le noyau MIPS microAptiv UP 32 bits, dont le code dans le langage de description du matériel Verilog était basé sur MIPS 4KEc.

L'agence aérospatiale japonaise JAXA a concédé sous licence le cœur du processeur MIPS 5Kf à MIPS Technologies, une société américaine. Cela s'est produit dans les années 2000. Le groupe qui a développé ce noyau existe dans différentes configurations depuis 40 ans:

- Tout d'abord, en 1978-1984, MIPS était un projet à Stanford, dirigé par John Hennessey. Sur le succès de ce projet, Hennessey est devenu l'auteur du manuel le plus célèbre sur l'architecture informatique et à un moment donné - le président de Stanford.

- Puis, en 1984, MIPS est devenue une société commerciale - MIPS Computer Systems. La même année, ARM a également été commercialisé. En 1991, MIPS a lancé le premier microprocesseur 64 bits au monde - MIPS R4000.

- Après cela, MIPS a été absorbé par Silicon Graphics et dans les années 1990, il a été utilisé dans des stations graphiques où les premiers films avec des graphismes réalistes ont été réalisés à Hollywood (Jurassic Park).

- Dans les années 2000, le groupe s'est séparé en MIPS Technologies et a notamment conçu un processeur pour JAXA. Le siège social de MIPS était situé en Californie; certains des développeurs de MIPS 5Kf étaient basés chez MIPS Europe à Copenhague.

- En 2012, MIPS Technologies a été acheté par la société britannique Imagination Technologies, qui est devenue célèbre en tant que développeur de GPU dans les premiers iPhone d'Apple.

- En 2017, Apple a lancé Imagination, et après quelques perturbations, la technologie et une partie du groupe MIPS ont été intégrées à Wave Computing, une startup qui développe une puce pour accélérer les réseaux de neurones.

- La puce Wave Computing est une combinaison d'un cluster de processeurs MIPS I6500 64 bits, d'un multiplicateur matriciel basé sur un tableau systolique à la Google TPU et d'un processeur de traitement de données basé sur un appareil avec une architecture reconfigurable à grain grossier - CGRA ) Les processeurs classiques du cluster I6500 chargent le multiplicateur matriciel et le processeur de flux de données, le multiplicateur matriciel fournit une densité de calcul et le processeur de flux de données de tâche est situé au milieu entre les processeurs classiques et le multiplicateur matriciel - il est plus flexible que le multiplicateur et plus productif que le CPU classique.

J'ai donc pris une photo avec l'un des deux principaux développeurs de la gamme MIPS 4K et 5K - Larry Hudepohl, Larry Huedepol (à droite dans une chemise rouge). Larry a commencé sa carrière chez Digital Equipment Corporation (DEC) en tant que concepteur de processeurs pour MicroVAX. Ensuite, Larry a travaillé pour une petite entreprise Cyrix, qui à la fin des années 1980 a mis au défi Intel et a fabriqué un coprocesseur FPU compatible avec Intel 80387 et 50% plus rapide. Larry a ensuite conçu les puces MIPS chez Silicon Graphics. Lorsque MIPS Technologies s'est séparé de Silicon Graphics, Larry et Ryan Quinter ont lancé ensemble le premier produit MIPS indépendant, MIPS 4K, qui est devenu l'épine dorsale de la gamme qui a dominé l'électronique domestique des années 2000 (lecteurs DVD, appareils photo, téléviseurs numériques). Ensuite, le MIPS 5K a volé dans l'espace - il a été utilisé par l'agence spatiale japonaise JAXA. Ensuite, Larry, en tant que VP Hardware Engineering, a dirigé le développement des lignes suivantes, et maintenant il travaille sur de nouvelles architectures d'accélérateurs Wave:

Revenons maintenant au processeur de Hayabusa-2 (dans Hayabusa-1, c'est différent). Voici une

fiche technique pour le cœur du processeur MIPS64 5Kf et une

page avec les données système sur une puce HR5000 . Notez quelques points intéressants.

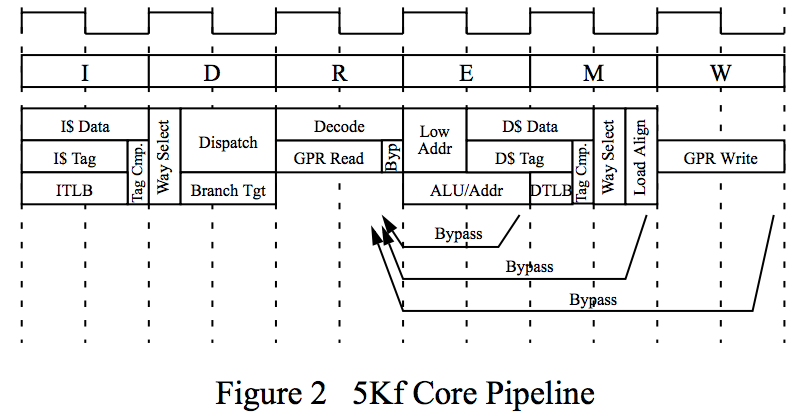

Tout d'abord, MIPS 5Kf est un processeur pipeline. Si vous ne savez pas comment cela fonctionne, alors le moyen le plus simple de vous connaître est d'étudier le septième chapitre du livre "Circuit numérique et architecture informatique" de David M. Harris et Sarah L. Harris, dont la dernière version peut être téléchargée en russe

ici ou

ici ) . Le convoyeur de MIPS 5Kf est différent du convoyeur MIPS classique de Harris & Harris. Ceux d'entre vous qui ont lu X&X peuvent regarder les différences et deviner pourquoi:

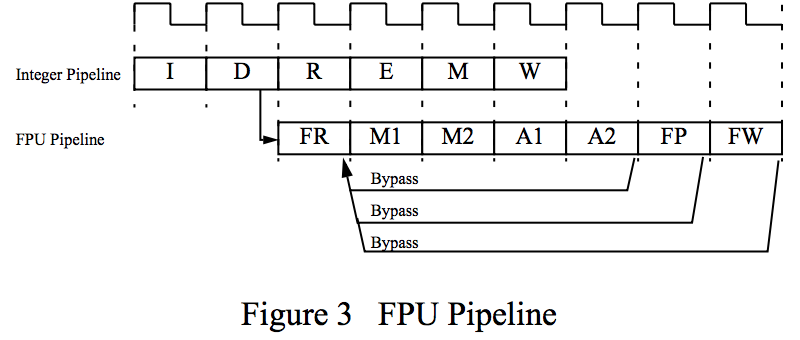

Bien sûr, MIPS 5Kf n'a pas cinq étapes de pipeline, mais six, avec une étape de répartition supplémentaire. Cette étape est nécessaire pour rendre le MIPS 5Kf superscalaire borné. Il peut effectuer non seulement des opérations les unes après les autres dans le pipeline, mais il peut également effectuer une opération à virgule flottante simultanément avec une opération entière ou avec une opération de mémoire (chargement ou sauvegarde). Stage Dispatch lance un coprocesseur à virgule flottante qui possède son propre pipeline à sept étapes:

Et ici à droite sur la photo, Darren Jones, Darren Jones, développeur FPU chez MIPS 5Kf. La lettre "f" dans "5Kf" signifie exactement qu'elle a une virgule flottante:

Ici, dans cette plaque, vous pouvez voir combien de cycles nécessitent différentes opérations dans le FPU et à quelle fréquence (taux de répétition) ils peuvent être exécutés dans le pipeline. Par exemple, la multiplication simple précision nécessite quatre cycles, mais vous pouvez démarrer une nouvelle multiplication dans le pipeline à chaque cycle. Ainsi, le FPU peut traiter simultanément quatre multiplications en simple précision à chaque étape de traitement. Mais la multiplication en double précision nécessite cinq cycles, et vous ne pouvez la démarrer qu'avec une pause dans le cycle. L'opération complexe consistant à prendre la racine carrée de la double précision nécessite jusqu'à 32 cycles, et vous ne pouvez commencer une nouvelle prise de la racine carrée qu'après 29 cycles. C'est ainsi que le calcul des coordonnées du navire et de ses formules de mouvement dans l'espace est optimisé:

Hayabusa-2 utilise la configuration MIPS 5Kf avec des caches d'instructions et de données séparés de 32 kilo-octets. Dans le même temps, la

brève description du HR5000 n'indique pas

clairement s'il utilise un cache à quatre canaux de 8 kilo-octets - ou un cache à deux canaux de 16 kilo-octets. Vous pouvez lire comment ces caches fonctionnent à la fois dans X&X et dans

mon ancienne présentation sur les caches , ainsi que dans le livre utile

Voir MIPS Run Linux 2nd Edition par Dominic Sweetman:

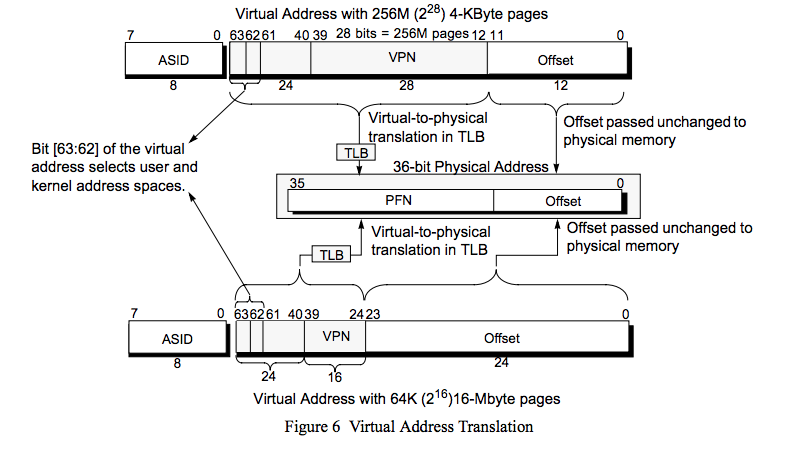

Hayabusa-2 possède également une unité de gestion de la mémoire (MMU), avec un tampon de traduction (TLB). TLB est un outil universel pour convertir rapidement des adresses du virtuel au physique. TLB vous permet de:

Masquez la mémoire du système d'exploitation du code non privilégié.

Protégez les programmes utilisateur les uns des autres.

Fournissez un accès au programme à la quantité de mémoire virtuelle qui dépasse la quantité de RAM physique.

Adresse mémoire physique plus grande que les adresses virtuelles sont disponibles.

Placez le programme dans n'importe quelle partie de la mémoire physique.

Permet à plusieurs régions de mémoire de ressembler à une pièce séquentielle.

Vous permet de charger des morceaux du programme à partir d'un périphérique externe selon vos besoins.

Le TLB associe également divers attributs à l'adresse: lecture, écriture et exécution, ainsi que des attributs de cache et de cohérence.

L'attribut de cache est nécessaire pour montrer au processeur où l'espace d'adressage est pour le niveau de cache suivant et où pour les résistances d'E / S qui ne peuvent pas être mises en cache.

Des attributs de cohérence sont nécessaires pour que plusieurs cœurs de processeur fonctionnent ensemble, chacun avec son propre cache de premier niveau, et ensemble, ils utilisent un cache de deuxième niveau commun.

TLB peut stocker un indicateur qu'une page avec une adresse donnée a été enregistrée. Cela aide lors de l'échange, du chargement-déchargement des pages de mémoire sur des systèmes avec moins de mémoire physique que ce dont l'application a besoin pour adresser toutes les parties de son code et de ses données avec des adresses virtuelles.

Voici à quoi ressemble la traduction d'une adresse virtuelle 64 bits en une adresse physique 36 bits sur MIPS 5Kf. Pourquoi sur Hayabusa-2 un processeur 64 bits avec des adresses physiques 36 bits? Je soupçonne que Hayabusa-2 prend des photos et doit traiter des images, ce qui nécessite beaucoup de mémoire. Peut-être que pour certains algorithmes, les échanges d'arithmétique 64 bits et de cache 64 bits (ou les échanges de mémoire non cache 64 bits) améliorent quelque chose, et cela s'avère utile dans l'espace. Mais je ne sais pas avec certitude, je dois probablement demander à

Zelenyikot et à l’

amartologie , qui en savent plus que moi sur l’espace.

Vous pouvez lire sur TLB dans X&X et Voir MIPS Run, mais il y a une nuance: les deux livres décrivent à quoi ressemble TLB du point de vue d'un programmeur. Mais du point de vue du développeur matériel, les concepteurs de processeur trompent le programmeur en lui montrant le TLB comme une table de traduction associative, malgré le fait qu'il y ait en fait trois tables à l'intérieur du TL: il y a trois instructions micro-TLB, des données micro-TLB et un commun (Joint TLB). Tout d'abord, le dispositif de gestion de la mémoire recherche ITLB et DTLB, et seulement s'il ne le trouve pas, il le prend à JTLB. Cela coûte au processeur 2 cycles supplémentaires. Voir aussi

mon ancienne présentation sur TLB :

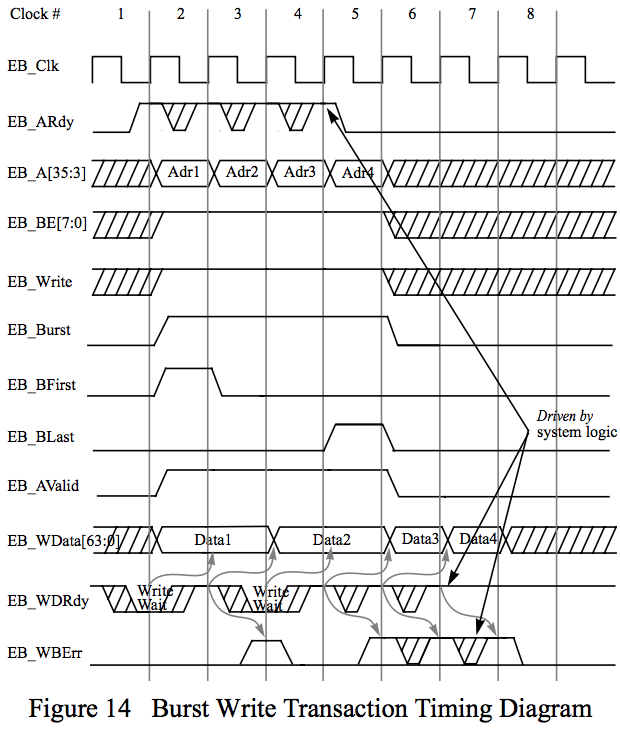

L'interface entre les caches de premier niveau et le contrôleur de mémoire dans MIPS 5Kf dans Hayabusa-2 est appelée EB (prononcé IB). C'est l'abréviation de bus externe. Il est similaire à AHB et AXI, et vous permet d'éclater, de vider du cache ou de remplir toute la ligne avec le cache, en utilisant des transferts en boucles séquentielles.

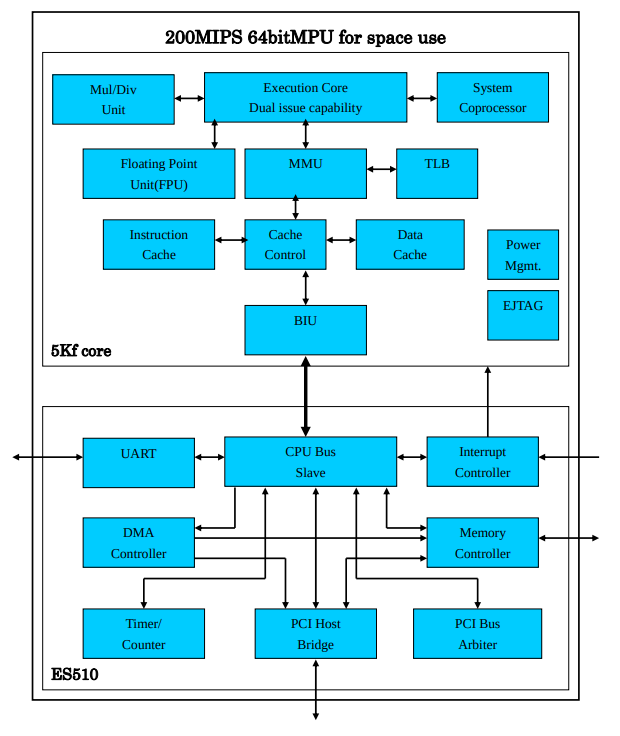

En dehors du cœur du processeur, le HR5000 dispose d'un contrôleur d'interruption, d'un module UART, d'un contrôleur d'accès direct à la mémoire, de minuteries et d'un contrôleur PCI:

Pour travailler dans l'espace, la puce doit être protégée des radiations. Je ne suis pas spécialiste de la radioprotection, pour cela il y a une

amartologie sur Habré, mais je sais qu'une telle protection peut se faire à la fois au niveau de la technologie de production physique, et au niveau des différents contrôles ECC, et même au niveau de l'architecture, avec triple, etc. Les créateurs du système cristallin HR5000 ont décidé d'utiliser la voie RTL2GDSII habituelle adoptée dans les applications commerciales, synthèse d'un graphe à partir d'éléments logiques à partir de code dans le langage de description matérielle Verilog. Cependant, après avoir reçu un tel graphique (netlist), ils le modifient en utilisant une bibliothèque spéciale de dureté par conception primitive (HBD) (jamais utilisé, donc toute clarification dans les commentaires est la bienvenue):

Étant donné que MIPS 5Kf est écrit en Verilog, il peut être transformé non seulement en une netlist, et non seulement en un masque pour fabriquer une puce dans une usine, mais aussi en une configuration FPGA. Malheureusement, les sources de MIPS 5Kf ne sont pas dans le domaine public, mais dans le domaine public sont le code source d'un descendant de son "frère cadet", un processeur MIPS 4K 32 bits. Ce "descendant" est appelé MIPS microAptiv UP, et sa configuration de base est incluse dans le package MIPSfpga. Le code MIPS 4K / 4KEc / microAptiv UP / M5150 (ce sont toutes des versions progressives de la ligne) a également été écrit par Larry, Ryan et Darren.

Vous pouvez jouer avec le pipeline, les caches, le dispositif de gestion de la mémoire et les interruptions du noyau MIPS microAptiv UP, l'exécuter sur un simulateur ou une carte avec FPGA / FPGA. Pour ce faire, téléchargez simplement le

package de démarrage MIPS Open ™ FPGA , ainsi que

MIPS Open ™ FPGA Labs et (c'est important!) Complétez-le avec

MIPSfpga + . Dans ce dernier, il existe des

laboratoires sur le pipeline, le cache et le périphérique de gestion de la mémoire .

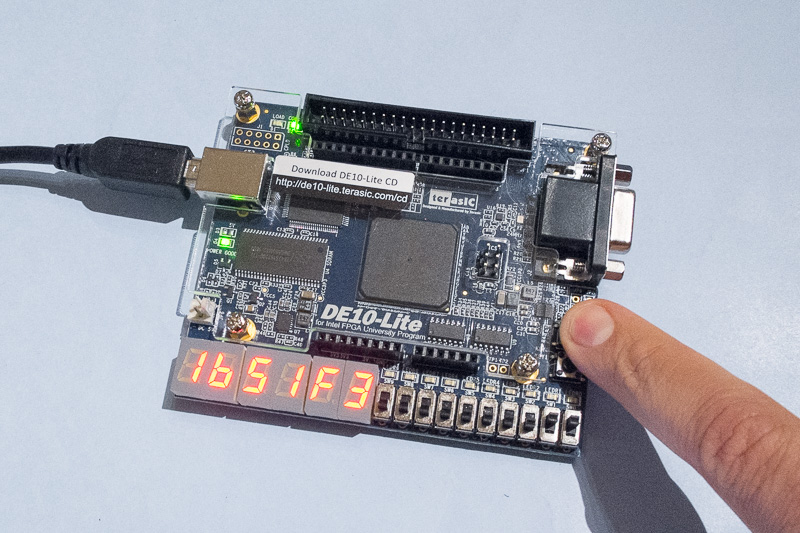

Vous pouvez synthétiser et exécuter le processeur MIPS microAptiv UP sur une carte peu coûteuse pour 85 $ (prix académique 55 $):

Pour travailler avec le package MIPSfpga / MIPSfpga +, vous devez connaître le langage de description du matériel Verilog, les principes de conception au niveau du transfert de registre et la capacité d'écrire dans l'assembleur MIPS.

L'assembleur MIPS est le plus facile à apprendre. Pour ce faire, vous pouvez

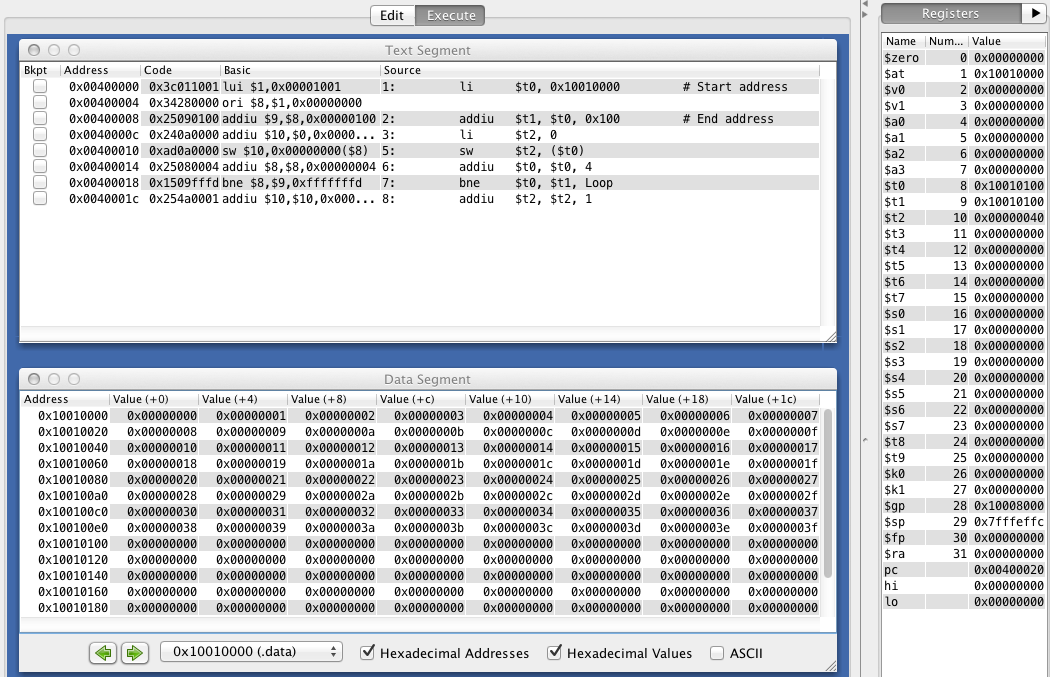

télécharger le simulateur MARS (MIPS Assembler et Runtime Simulator) . Vous pouvez apprendre à l'utiliser en 5 minutes, en fait, il contient trois boutons: assembler, exécuter, exécuter étape par étape:

Ensuite, vous pouvez passer la journée à pratiquer l'écriture en langage assembleur pour les livres

Harris & Harris et

See MIPS Run Linux .

Si vous ne savez rien du tout sur le développement des circuits numériques en général et dans la langue pour décrire l'équipement en particulier, vous pouvez commencer par le cours en ligne Rosnanov pour les écoliers, en trois parties:

«Du transistor au microcircuit» ,

«Le côté logique des circuits numériques» ,

«Le côté physique circuits numériques " ). Ensuite, vous pouvez étudier Verilog sur X&X et comprendre qu'il existe un processeur sur le processeur

schoolMIPS simplifié.

Si vous êtes intéressé par ce sujet et souhaitez participer aux travaux sur

MIPS Open (dans le cadre duquel le noyau MIPS microAptiv UP a été ouvert), écrivez dans les commentaires. Rosnanovtsy organise également un

séminaire pour les écoliers sur la conception numérique les 17 et

19 avril , qui comprendra, entre autres, ce processeur d'espace. Hayabusa-2 a bombardé Ryuga pas en vain - c'est aussi une occasion pour les écoliers et les étudiants russes de découvrir ce qui est en elle.