Le chapitre suivant de la documentation officielle de Cypress sur la gestion du chronométrage et de la réinitialisation. Comme déjà mentionné dans le premier article de cette série, ce module offre une sélection et une résolution de synchronisation, ainsi qu'une réinitialisation de la sélection dans UDB. Plus de détails - sous la coupe.

Le contenu général du cycle «UDB. Qu'est-ce que c'est? "

Partie 1. Introduction. Pld.Partie 2. Chemin de données.Partie 3. Datapath FIFO.Partie 4. Datapath ALU.Partie 5. Chemin de données. Petites choses utiles.Partie 6. Module de gestion et d'état.Partie 7. Module de commande de temporisation et de réinitialisation. (Article actuel)

Partie 8. Adressage UDB21.3.4 Module de réinitialisation et de contrôle de l'horloge

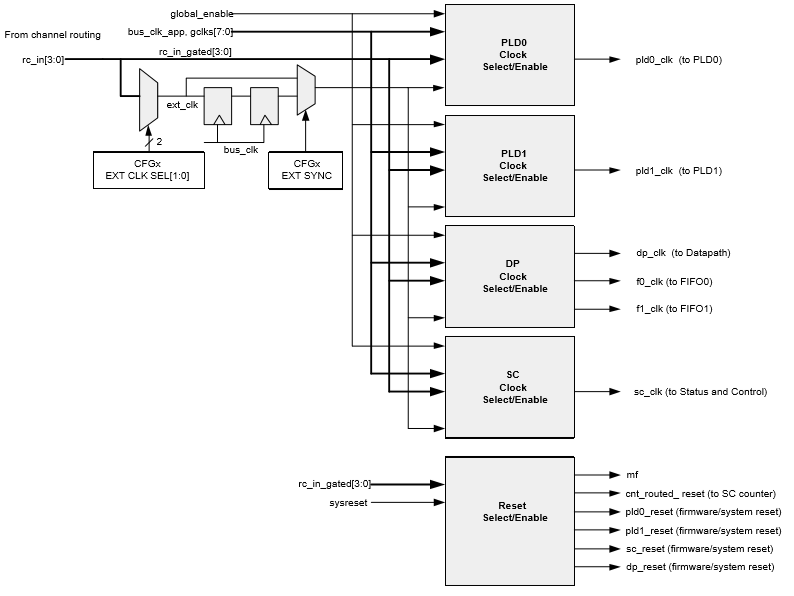

La fonction principale de ce module est de sélectionner les horloges parmi les horloges globales disponibles ou l'horloge de bus pour chaque PLD, Datapath et module de contrôle et d'état. Le module prend également en charge les réinitialisations de bloc UDB dynamiques et logicielles. Comme le montre la figure 21-38, il existe quatre unités de commande d'horloge et une unité de commande de réinitialisation. Quatre entrées (RC_IN [3: 0]) sont disponibles pour le transfert à partir de la matrice de trace globale. Chaque unité de contrôle d'horloge peut sélectionner une source pour l'entrée d'activation d'horloge à partir de ces entrées de trace, et il existe également un multiplexeur qui vous permet de sélectionner l'une des entrées de trace à utiliser comme source d'horloge externe. Comme vous pouvez le voir sur la figure, le choix d'une source d'horloge externe peut être synchronisé. Pour chaque composant UDB, vous avez le choix entre 10 horloges: 8 horloges numériques globales, une horloge de bus et une horloge externe sélectionnée (ext clk). N'importe lequel des signaux d'entrée tracés (rc_in) peut être utilisé soit comme activateur sensible au niveau, soit comme activateur sensible aux bords. La fonction de réinitialisation de ce bloc fournit une réinitialisation tracée des blocs PLD et du compteur SC, ainsi que la possibilité de réinitialiser par programmation chaque bloc pour prendre en charge la reconfiguration.

L'horloge de bus appliquée au module de commande d'horloge et de réinitialisation est différente de l'horloge de bus système. Ce signal est appelé "bus_clk_app" et est verrouillé de la même manière que les autres signaux d'horloge numérique. L'horloge du bus système est utilisée uniquement pour les opérations d'entrée-sortie et est automatiquement déverrouillée pour chaque accès. Le générateur d'horloge Datapath génère trois horloges: une pour Datapath et un signal pour chaque FIFO.

Figure 21-38. Module de commande d'horloge et de réinitialisation.

21.3.4.1 Contrôle d'horloge

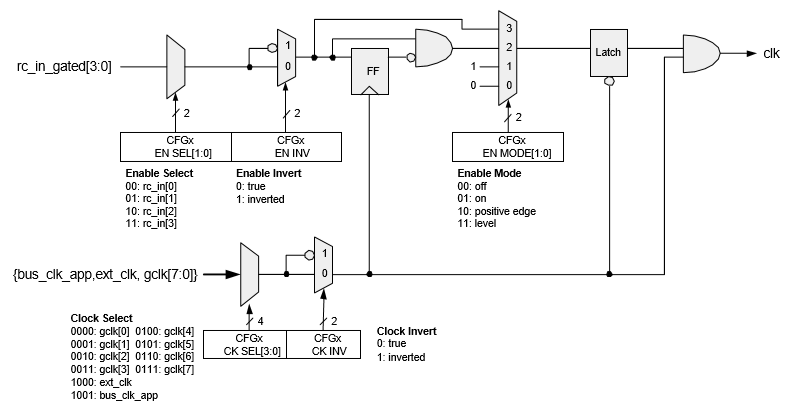

La figure 21-39 montre un exemple de schéma de sélection et de résolution de synchronisation. Chaque UDB a quatre schémas de ce type: un pour chaque bloc PLD, un pour Datapath et un pour le bloc de contrôle et d'état. Les principaux composants de ce circuit sont le multiplexeur de sélection d'horloge globale, l'inverseur d'horloge, le multiplexeur de signal d'activation d'horloge, l'inverseur de signal d'activation d'horloge et la logique de détection différentielle.

Figure 21-39. Gérer la sélection / activation du chronométrage.

Sélection d'horlogeIl y a huit horloges numériques mondiales transmises à tous les UDB. N'importe lequel d'entre eux peut être sélectionné. Les horloges numériques globales sont des sorties de diviseurs de fréquence sélectionnés par l'utilisateur. Voir «Système de synchronisation» à la page 109 de l'original. Une autre option est l'horloge de bus, qui a la fréquence la plus élevée du système. Ce signal est appelé "bus_clk_app" et est tracé séparément de l'horloge du bus système. De plus, pour prendre en charge les fonctions avec un signal d'horloge direct (par exemple, SPI), une ligne de trace externe peut être sélectionnée comme signal d'horloge d'entrée. Étant donné que les fonctions d'application sont liées à des limites arbitraires au sein de l'UDB, la sélection d'un signal d'horloge individuel pour chaque sous-composant UDB contribue à une granularité précise dans la programmation.

Inversion d'horlogeLe signal d'horloge sélectionné peut être inversé. Cela limitera la fréquence maximale de travail du fait de l'existence de tronçons à demi-cycle. L'enregistrement de bus simultané et les enregistrements internes (par exemple, l'enregistrement programmé d'une nouvelle valeur de compteur pendant son fonctionnement) ne sont pas pris en charge lorsque l'horloge interne est inversée et a la même fréquence que l'horloge de bus. Cette limitation affecte A0, A1, D0, D1, ainsi que le registre de contrôle en mode compteur.

Sélection de l'activation de l'horlogeLe signal de validation d'horloge peut être transmis à n'importe quel signal synchrone et sélectionné à l'une des quatre entrées de la matrice de trace disponibles pour ce bloc.

Inversion d'activation de l'horlogeLe signal de validation d'horloge peut être inversé. Pour cette raison, ce signal peut être généré dans n'importe quelle polarité.

Mode d'activation de l'horlogePar défaut, le mode de résolution d'horloge est désactivé. Après avoir réglé le fonctionnement de l'unité cible, le logiciel peut définir l'un des modes de fonctionnement décrits ci-dessous à l'aide du registre CFGxEN MODE [1: 0], illustré à la figure 21-39.

Tableau 21-23. Modes de résolution de synchronisation.

Utilisation de l'autorisation d'horlogeIl existe deux cas d'utilisation courants pour les autorisations de synchronisation.

Activation du logiciel (activation du micrologiciel) : il est supposé que la plupart des fonctions nécessitent une activation de l'horloge logicielle pour démarrer et arrêter la fonction. Étant donné que la limite de la fonction liée au tableau UDB est conditionnelle, la fonction peut s'étendre sur plusieurs UDB et / ou parties des UDB. Par conséquent, un moyen est nécessaire pour inclure chaque fonction atomiquement. Ceci est généralement implémenté en utilisant un bit dans le registre de contrôle transmis à une ou plusieurs entrées de validation d'horloge. Ce scénario prend également en charge le cas où les applications doivent exécuter plusieurs blocs non liés en même temps.

Génération d'horloge locale émulée: cette fonctionnalité permet aux UDB de générer des horloges locales et de les distribuer aux autres UDB de la matrice à l'aide du modèle de mise en œuvre d'activation de l'horloge de synchronisation, plutôt que d'horloge directe séparément pour chaque UDB. L'utilisation de la fonction Front positif pour activer la résolution supprime les restrictions sur le rapport cyclique du signal de résolution.

Synchronisation FIFO spécialeLes blocs FIFO Datapath ont des fonctions de synchronisation. Par défaut, la synchronisation FIFO a la même configuration que la synchronisation Datapath. Cependant, les blocs FIFO ont des bits de contrôle spéciaux qui modifient la configuration de l'horloge:

- chaque horloge FIFO peut être inversée par rapport à la polarité de l'horloge de chemin de données sélectionnée;

- lorsque le mode FIFO FAST est sélectionné, l'horloge de bus remplace le choix de l'horloge Datapath qui utilise généralement FIFO.

21.3.4.2 Gestion de réinitialisation

Il existe deux modes de gestion de réinitialisation: hérité et standard. Le mode est défini à l'aide du bit

ALT RES dans chaque registre de configuration de l'UDB CFG31. Par défaut, la valeur du bit est 0 (mode hérité); il est recommandé de lui attribuer une valeur de 1 (mode standard). Le mode standard a un degré de granularité plus élevé - les blocs individuels à l'intérieur de l'UDB peuvent utiliser des vidages tracés. Pour plus d'informations sur le mode hérité, contactez Cypress.

PLD Reset ControlLa figure 21-40 montre le système de réinitialisation PLD.

Figure 21-40. Réinitialiser la structure PLD.Contrôle de réinitialisation du chemin de données

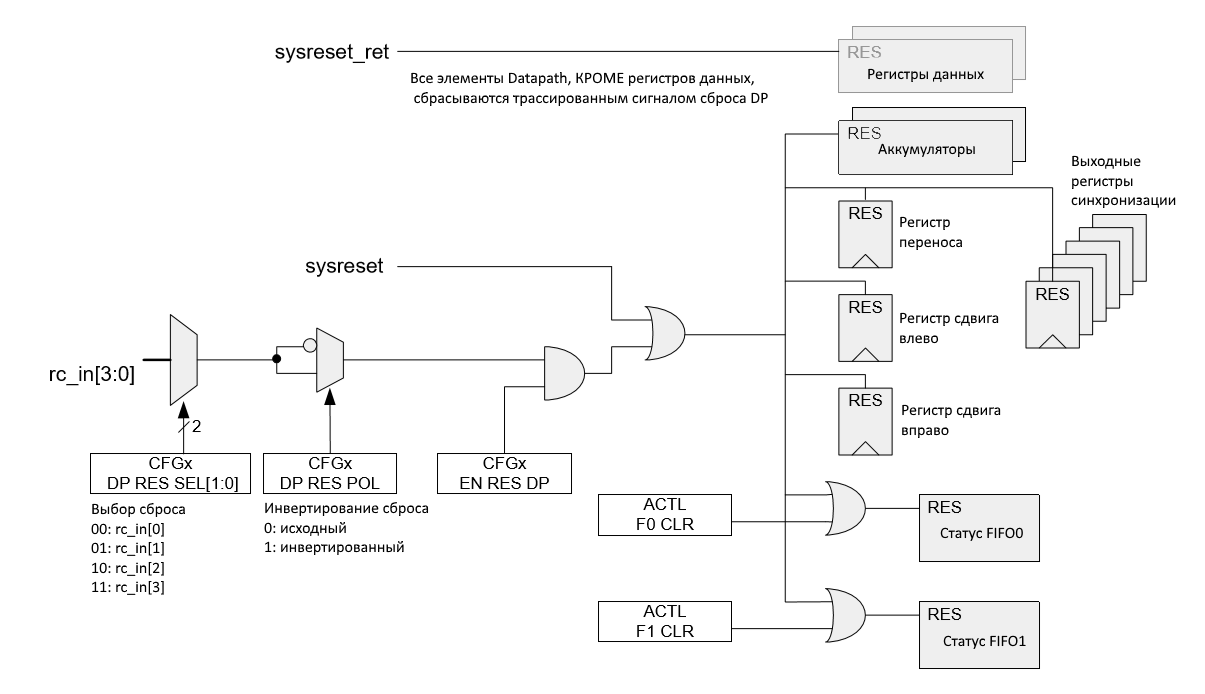

Figure 21-40. Réinitialiser la structure PLD.Contrôle de réinitialisation du chemin de donnéesLa figure 21-41 montre le système de réinitialisation de Datapath. Le vidage tracé s'applique à tous les registres et états Datapath à l'exception des registres de données D0 et D1. Les registres de données sont des registres persistants. Le contenu du FIFO n'est pas défini après la réinitialisation, car il se trouve dans la RAM.

Figure 21-41. Structure de réinitialisation du chemin de données.Contrôle de réinitialisation de l'état et du contrôle

Figure 21-41. Structure de réinitialisation du chemin de données.Contrôle de réinitialisation de l'état et du contrôleLa figure 21-42 montre le système de contrôle et de réinitialisation de l'état. Les registres de contrôle / compteur et d'état ont une réinitialisation de trace commune, mais ils sont activés séparément. Les registres de chevauchement masque / période et les commandes auxiliaires sont des registres de sauvegarde.

Figure 21-42. Réinitialiser la gestion et la gestion des statuts.

Figure 21-42. Réinitialiser la gestion et la gestion des statuts.21.3.4.3 Initialisation UDB à la mise sous tension (POR)

Registre et initialisation d'étatTableau 21-24. Initialisation des états UDB lorsqu'elle est activée

Initialisation de traceLorsqu'il est activé, l'état des entrées et sorties de trace présente les caractéristiques suivantes:

- toutes les sorties UDB qui dirigent les données vers la matrice de trace sont maintenues à «0»;

- tous les pilotes sortant de la trace et entrant dans les entrées UDB sont initialement remis à zéro.

Cette initialisation évite les états conflictuels lors du traçage et la configuration initiale se produit dans une séquence dans laquelle l'ordre n'a pas d'importance.

La fin suit. Nous préparons la

dernière traduction de la section restante de la documentation propriétaire de Cypress sur UDB, à savoir l'adressage UDB.