La carte d'extension RAM proposée pour l'ordinateur Apple IIgs est basée sur des puces NEC uPD424400-70 provenant de plusieurs modules SIMM de 1 mégaoctet. Chacune de ces micropuces stocke 1 M de grignotages et est logée dans un boîtier de type SOJ à 26 broches.

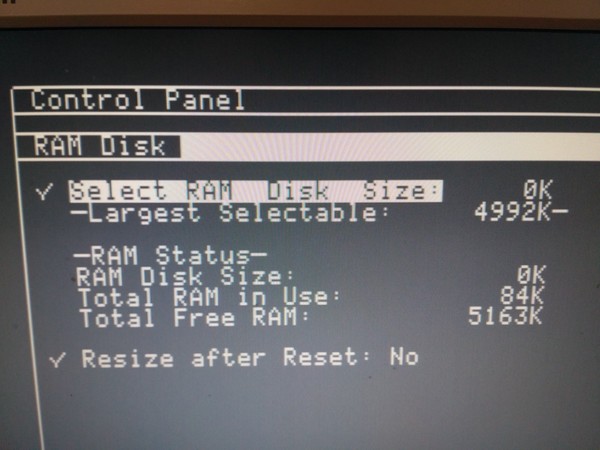

L'ordinateur Apple IIgs est alimenté par un processeur 65C816 - 16 bits, mais avec un bus de données 8 bits. La carte d'extension contient 4 Mo de RAM. La mémoire est divisée en quatre lignes de 1 Mo chacune. La ligne se compose de deux jetons de 1 m de grignotages, donc un total de huit jetons était nécessaire.

L'ordinateur dispose déjà d'un emplacement pour la carte d'extension RAM. Il affiche tous les signaux nécessaires, l'ordinateur s'occupe également de la régénération de la RAM dynamique. Par conséquent, la carte d'extension est assez simple. L'auteur a décidé de rendre la carte de petite taille, car le coût de sa fabrication en dépend, et a également mis toute la logique dans le FPGA GAL22V10.

Les signaux suivants sont présents sur l'emplacement d'extension RAM:

FRA0-FRA9 - Adresse de cellule multiplexée 10 bits, servie directement aux entrées d'adresse des puces RAM dynamiques

CROW0, 1 - deux bits pour sélectionner l'une des quatre lignes

/ CRAS - ligne d'adresse de signal stroboscopique de RAM dynamique

/ CCAS - Adresse de la colonne de déclenchement du signal de la RAM dynamique

FR / W - autorisation d'écriture en RAM, ce signal nécessite un traitement supplémentaire, voir ci-dessous

D0-D7 - bus de données, connecté directement aux lignes d'entrée / sortie des puces RAM

/ CSEL - une unité logique apparaît sur cette ligne lors de la lecture depuis la RAM, elle doit être inversée et alimentée aux entrées / OE des puces RAM

MSIZE - indique à l'ordinateur le volume de la ligne: un - 256 ko, zéro - 1 Mo, ici cette ligne est connectée à un fil commun

14M, PH2CLK, A10-A15 - ne sont pas impliqués dans la carte proposée

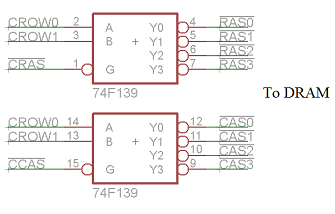

Les signaux / CRAS et / CCAS doivent être démultiplexés pour obtenir des signaux / RAS et / CAS séparés pour chaque ligne. Pour cela, la puce 74F139 convient (ci-après, il est entendu qu'il n'y aura pas de puces séparées sur la carte, au lieu de cela, il y aura un FPGA commun).

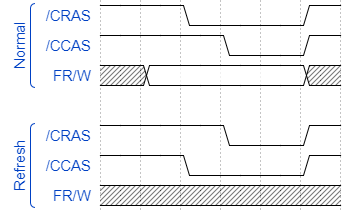

Le signal FR / W ne peut pas être envoyé directement à l'entrée / WE des puces RAM dynamiques, et c'est pourquoi. Dans une opération de lecture-écriture normale, la ligne / RAS devient d'abord active (ce qui correspond à un zéro logique), puis la ligne / CAS. Au cours d'un cycle de régénération dynamique de RAM, au contraire, la ligne / CAS devient d'abord active, puis / RAS devient active. Mais les puces utilisées nécessitent qu'une unité apparaisse sur la ligne / WE avant que la ligne / RAS ne devienne active. Et le signal FR / W provenant d'Apple IIgs ne répond pas à cette exigence. L'état de FR / W pendant le cycle de régénération n'est pas défini. Par conséquent, un circuit est nécessaire qui détecte un cycle de régénération et alimente une unité vers / WE.

La première étape consiste à identifier le cycle de régénération. Voici le chronogramme:

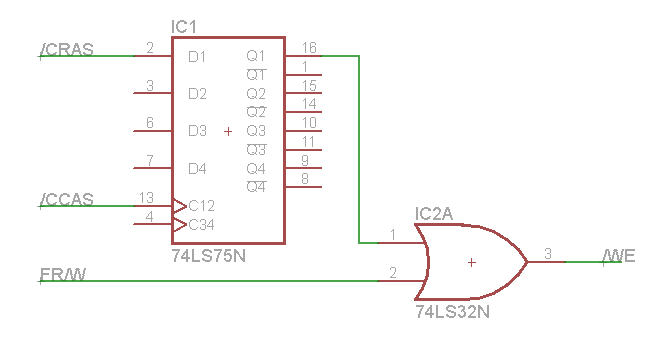

L’idée de l’auteur est d’utiliser un verrou «transparent». Le signal / CRAS pour lui est le signal d'entrée, / CCAS est le signal de verrouillage. Lorsque l'unité est allumée / CCAS, l'appareil passe le signal d'entrée à travers lui-même: l'état de la sortie change après l'état de l'entrée. Lorsque / CCAS passe de un à zéro, le verrou mémorise le signal à l'entrée et maintenant il ne change pas à la sortie. Dans une opération de lecture / écriture normale sur / CRAS, zéro est présent au moment de la commutation / CCAS de un à zéro. Et pendant le cycle de régénération sur / CRAS, il y en a également un au moment de la mise à zéro / CCAS. Ensuite, lorsque / CCAS repasse à un, le verrou redevient transparent. Il rappelle une fleur fantastique de "Secrets de la troisième planète", qui peut être à la fois un "miroir" et une "caméra".

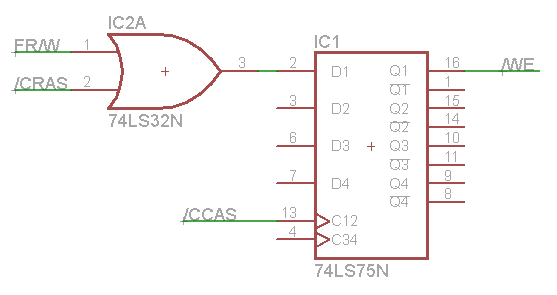

Dans un premier temps, l'auteur a élaboré le schéma suivant:

Mais pour son transfert vers le FPGA GAL22V10, deux broches de sortie sont nécessaires. Par conséquent, le régime a dû être simplifié. En fonctionnement normal, le signal FR / W prend la valeur souhaitée jusqu'au déclic, c'est donc également possible.

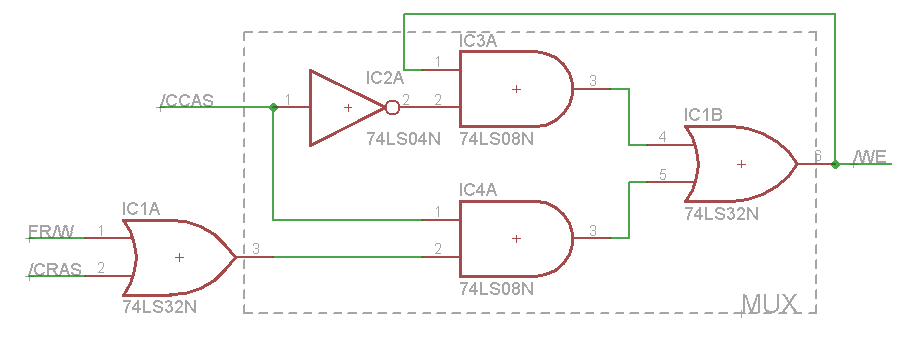

Un verrou «transparent» peut être réalisé à partir d'un multiplexeur, et à son tour, d'éléments logiques. Le schéma devient comme ceci:

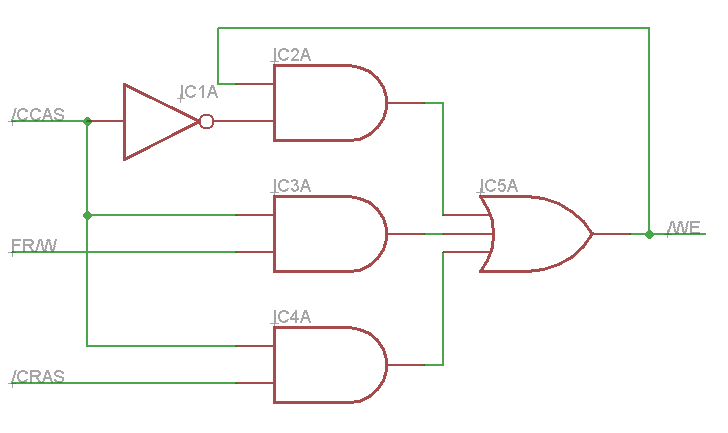

Et après la simplification - comme ceci:

Cette option est transférée au FPGA. Pour la compilation, l'auteur a utilisé WinCUPL. Ce programme est disponible sur le site Web d'Atmel. Il est brut et vole constamment, mais il a parfaitement fait face à la tâche. Programmeur - Genius G540.

Le cavalier SJ1 de la carte agit comme ceci. Si les broches 1 et 2 sont connectées, le signal / OE passe par le FPGA. Si les broches 2 et 3 sont connectées, elle est connectée à un fil commun. L'auteur n'était pas sûr que le schéma d'identification du cycle de régénération fonctionnerait. Par conséquent, il a ajouté ce cavalier au cas où la configuration FPGA devait être refaite.

Comme il s'est avéré que tout fonctionne, vous n'avez pas besoin de souder les broches, connectez simplement les bornes 1 et 2 avec une goutte de soudure.

Pour réduire la taille de la carte, l'auteur a appliqué un condensateur de puissance pour quatre puces RAM et a placé les puces elles-mêmes des deux côtés de la carte.

Les puces électroniques dans les boîtiers SOJ sont difficiles à souder, et en particulier à souder, avec un fer à souder. L'auteur recommande d'utiliser un sèche-cheveux.

Développez les puces correctement. En fin de compte, ils sont inversés. La broche 1 regarde vers le bas.

Certains trous traversants sont trop proches des coussinets. Ne les court-circuitez pas avec de la soudure.

Et les plates-formes 1 et 2 pour le cavalier, au contraire, se ferment.

Les condensateurs C1 - C3 ont une capacité de 0,1 μF, C4 - 10 μF.

L'auteur a commandé les planches à OSH Park. Le revêtement ENIG est appliqué - or, mais très mince. Pour les cartouches de jeu ne convient pas - il sera rapidement effacé. Et ici, la planche a été placée une fois de plus dans la fente.

L'auteur remercie

GGLabs pour le circuit d'une carte similaire, cela a beaucoup aidé, merci!

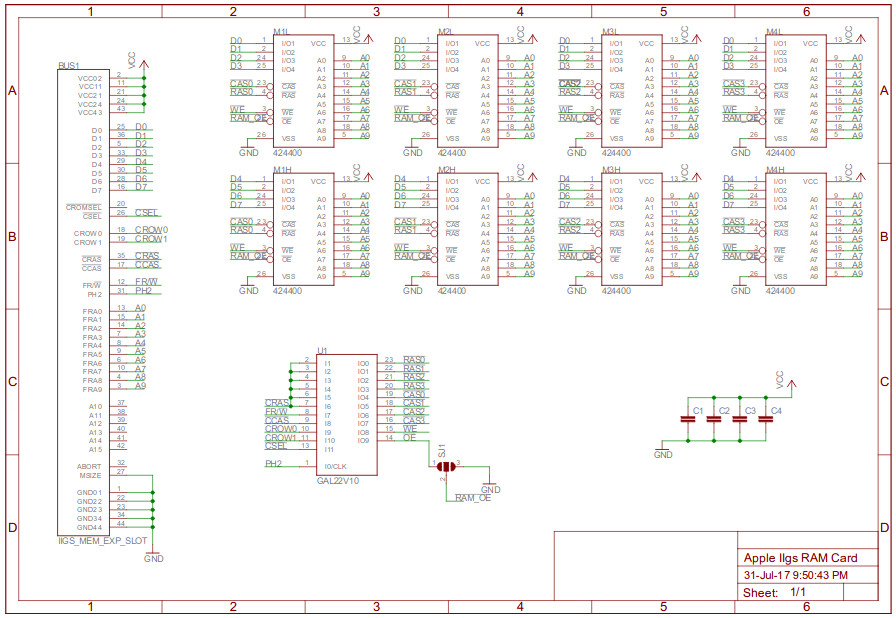

Le circuit fini s'est avéré comme ceci:

Fichiers:

Micrologiciel FPGA GAL22V10 , version du programme WinCUPL 5.30.4 appliquée

Carte , logiciel Eagle version 7.1 appliqué

Plan PDFGagné!