Traduction de la première partie de la présentation de la Tesla Autonomy Investor Day sur le développement d'un ordinateur entièrement autonome pour le pilote automatique Tesla. Nous comblons l'écart entre les critiques de thèse pour la présentation et son contenu.Le texte de la présentation est traduit proche de l'original. Questions à l'orateur - sélectivement avec des abréviations.Animateur: Bonjour à tous. Désolé d'être en retard. Bienvenue à notre première journée de conduite autonome. J'espère que nous pourrons le faire plus régulièrement pour vous tenir au courant de nos développements.

Il y a environ trois mois, nous préparions le rapport sur les résultats du quatrième trimestre avec Ilon et d'autres dirigeants. J'ai ensuite dit que le plus grand écart dans les conversations avec les investisseurs, entre ce que je vois à l'intérieur de l'entreprise et sa perception externe, est notre progrès dans la conduite autonome. Et cela est compréhensible, au cours des deux dernières années, nous avons parlé d'augmenter la production du modèle 3, autour duquel il y avait beaucoup de controverse. En fait, beaucoup de choses se sont passées en arrière-plan.

Nous avons travaillé sur une nouvelle puce pour le pilote automatique, complètement repensé le réseau neuronal de vision industrielle et finalement commencé à lancer le Full Self-Driving Computer (FSDC). Nous avons pensé que c'était une bonne idée d'ouvrir le voile, d'inviter tout le monde et de raconter tout ce que nous avons fait au cours des deux dernières années.

Il y a environ trois ans, nous voulions utiliser, nous voulions trouver la meilleure puce pour la conduite autonome. Nous avons constaté qu'aucune puce n'avait été conçue à partir de zéro pour les réseaux de neurones. C'est pourquoi nous avons invité mon collègue Pete Bannon, vice-président de la conception de circuits intégrés, à développer une telle puce pour nous. Il a environ 35 ans d'expérience dans le développement de puces. Dont 12 ans chez PASemi, racheté par la suite par Apple. Il a travaillé sur des dizaines d'architectures et d'implémentations différentes et était le concepteur en chef de l'iPhone 5 d'Apple, peu de temps avant de rejoindre Tesla. Nous rejoint également sur Elon Musk. Je vous remercie

Ilon: En fait, j'allais présenter Pete, mais comme ils l'ont déjà fait, j'ajouterai qu'il est tout simplement le meilleur architecte de systèmes et de circuits intégrés au monde que je connaisse. C'est un honneur pour vous et votre équipe chez Tesla. Veuillez simplement nous parler du travail incroyable que vous avez accompli.

Pete: Merci Ilon. Je suis heureux d'être ici ce matin et c'est vraiment agréable de vous parler de tout le travail que mes collègues et moi avons fait ici à Tesla au cours des trois dernières années. Je vais vous expliquer un peu comment tout a commencé, puis je vais vous présenter l'ordinateur FSDC et vous expliquer un peu comment cela fonctionne. Nous allons nous plonger dans la puce elle-même et considérer certains détails. Je vais décrire le fonctionnement de l'accélérateur de réseau neuronal spécialisé que nous avons conçu, puis montrer quelques résultats, et j'espère qu'à ce moment-là, vous ne vous endormirez pas encore.

J'ai été embauché en février 2016. J’ai demandé à Ilon s’il était prêt à dépenser autant que nécessaire pour créer ce système spécialisé, il a demandé: «Allons-nous gagner?», J’ai répondu: «Eh bien, oui, bien sûr», puis il a répondu «Je suis en affaires» et tout a commencé . Nous avons embauché un groupe de personnes et commencé à penser à quoi ressemblerait une puce conçue spécifiquement pour la conduite entièrement autonome. Nous avons passé dix-huit mois à développer la première version et, en août 2017, nous l'avons mise en production. Nous avons obtenu la puce en décembre, cela a fonctionné et a très bien fonctionné du premier coup. En avril 2018, nous avons apporté plusieurs modifications et publié la version B zero Rev. En juillet 2018, la puce a été certifiée et nous avons commencé la production à grande échelle. En décembre 2018, la pile de conduite autonome a été lancée sur de nouveaux équipements, et nous avons pu procéder à la conversion des voitures de société et aux tests dans le monde réel. En mars 2019 nous avons commencé à installer un nouvel ordinateur dans les modèles S et X, et en avril - dans le modèle 3.

Ainsi, tout le programme, de l'embauche des premiers employés au lancement complet dans les trois modèles de nos voitures, a pris un peu plus de trois ans. C'est peut-être le programme de développement de systèmes le plus rapide auquel j'ai jamais participé. Et cela parle vraiment des avantages d'une intégration verticale élevée, vous permettant de faire une conception parallèle et d'accélérer le déploiement.

En termes d'objectifs, nous nous sommes complètement concentrés uniquement sur les exigences de Tesla, ce qui simplifie considérablement la vie. Si vous avez un seul client, vous n'avez pas à vous soucier des autres. L'un des objectifs était de maintenir la puissance en dessous de 100 watts afin de pouvoir convertir les machines existantes. Nous voulions également réduire les coûts pour fournir une redondance pour une plus grande sécurité.

Au moment où nous passions nos doigts vers le ciel, j'ai soutenu que conduire une voiture nécessiterait une performance du réseau neuronal d'au moins 50 billions d'opérations par seconde. Par conséquent, nous voulions obtenir au moins autant, et mieux, plus. Les tailles de lot déterminent le nombre d'éléments avec lesquels vous travaillez en même temps. Par exemple, les TPU Google ont une taille de paquet de 256 et vous devez attendre que vous ayez 256 éléments à traiter avant de commencer. Nous ne voulions pas attendre et avons développé notre moteur avec une taille de package d'un. Dès que l'image apparaît, nous la traitons immédiatement pour minimiser les retards et augmenter la sécurité.

Nous avions besoin d'un processeur graphique pour effectuer un post-traitement. Au début, cela occupait beaucoup, mais nous avons supposé qu'avec le temps, il deviendrait plus petit, car les réseaux de neurones s'améliorent de mieux en mieux. Et c'est vraiment arrivé. Nous avons pris des risques en mettant un processeur graphique assez modeste dans la conception, et cela s'est avéré être une bonne idée.

La sécurité est très importante, si vous n'avez pas de voiture protégée, vous ne pouvez pas avoir de voiture sûre. Par conséquent, une grande attention est accordée à la sécurité et, bien sûr, à la sécurité.

En termes d'architecture de puce, comme Ilon l'a mentionné plus tôt, en 2016, il n'y avait pas d'accélérateur créé à l'origine pour les réseaux de neurones. Tout le monde a simplement ajouté des instructions à son CPU, GPU ou DSP. Personne n'a fait de développement avec 0. Par conséquent, nous avons décidé de le faire nous-mêmes. Pour les autres composants, nous avons acheté des CPU et GPU industriels IP standard, ce qui nous a permis de réduire le temps de développement et les risques.

Une autre chose un peu inattendue pour moi était la possibilité d'utiliser les commandes existantes dans Tesla. Tesla avait d'excellentes équipes de développeurs d'alimentations, d'analyse d'intégrité du signal, de conception de boîtier, de firmware, de logiciel système, de développement de circuits imprimés et un très bon programme de validation de système. Nous avons pu utiliser tout cela pour accélérer le programme.

Voilà à quoi ça ressemble. Sur la droite, vous voyez les connecteurs pour la vidéo provenant des caméras de la voiture. Deux ordinateurs de conduite autonomes au centre de la carte, à gauche - les connecteurs d'alimentation et de contrôle. J'adore quand une solution se résume à ses éléments de base. Vous avez une vidéo, un ordinateur et une alimentation simple et claire. Voici la précédente solution Hardware 2.5, qui incluait l'ordinateur, et que nous avons installée au cours des deux dernières années. Voici une nouvelle conception pour un ordinateur FSD. Ils sont très similaires. Ceci, bien sûr, est dû aux limites du programme de modernisation des voitures. Je voudrais souligner qu'il s'agit en fait d'un ordinateur plutôt petit. Il est placé derrière la boîte à gants et n'occupe pas la moitié du coffre.

Comme je l'ai dit plus tôt, il y a deux ordinateurs complètement indépendants sur la carte. Ils sont surlignés en bleu et vert. Sur les côtés de chaque SoC, vous pouvez voir des puces DRAM. En bas à gauche, vous voyez des puces FLASH qui représentent le système de fichiers. Il existe deux ordinateurs indépendants qui démarrent et s'exécutent sous leur propre système d'exploitation.

Ilon: Le principe général est que si une pièce tombe en panne, la machine peut continuer à se déplacer. La caméra, le circuit d'alimentation, l'une des puces informatiques Tesla tombe en panne - la machine continue de bouger. La probabilité de panne de cet ordinateur est nettement inférieure à la probabilité que le conducteur perde connaissance. Il s'agit d'un indicateur clé, au moins d'un ordre de grandeur.

Pete: Oui, donc l'une des choses que nous faisons pour maintenir l'ordinateur en marche est des blocs d'alimentation redondants. La première puce fonctionne sur une source d'alimentation et la seconde sur une autre. Il en va de même pour les caméras, la moitié des caméras sur l'alimentation sont marquées en bleu, l'autre moitié en vert. Les deux puces reçoivent toute la vidéo et la traitent indépendamment.

Du point de vue de la conduite, la séquence consiste à collecter beaucoup d'informations sur le monde qui vous entoure, nous avons non seulement des caméras, mais aussi des radars, GPS, des cartes, un stabilisateur gyroscopique (IMU), des capteurs à ultrasons autour de la voiture. Nous avons un angle de braquage, nous savons à quoi devrait ressembler l'accélération d'une voiture. Tout cela se réunit pour former un plan. Lorsque le plan est prêt, les deux ordinateurs échangent leurs versions du plan pour s'assurer qu'elles correspondent.

En supposant que le plan est le même, nous émettons des signaux de commande et conduisons. Maintenant que vous vous déplacez avec les nouveaux contrôles, vous voulez certainement le tester. Nous vérifions que les signaux de commande transmis coïncident avec ce que nous avions l'intention de transmettre aux actionneurs de la voiture. Des capteurs sont utilisés pour vérifier que le contrôle a bien lieu. Si vous demandez à la voiture d'accélérer, de ralentir ou de tourner à droite ou à gauche, vous pouvez regarder les accéléromètres et vous assurer que cela se produit réellement. Il existe une redondance et une duplication importantes de nos données et de nos capacités de surveillance des données.

Parlons de la puce. Il est emballé dans un BGA de 37,5 mm avec 1600 broches, dont la plupart sont alimentées et mises à la terre. Si vous retirez le couvercle, vous pouvez voir le substrat et le cristal au centre. Si vous séparez le cristal et le retournez, vous verrez 13 000 bosses C4 dispersées à travers la surface. Voici les douze couches métalliques du circuit intégré. Il s'agit d'un processus CMOS FinFET de 14 nanomètres mesurant 260 mm², un petit circuit. A titre de comparaison, une puce de téléphone portable classique mesure environ 100 mm2. Un processeur graphique hautes performances mesurera environ 600 à 800 mm.kv. Nous sommes donc au milieu. Je dirais que c'est le moyen d'or, c'est une taille pratique pour l'assemblage. Il y a 250 millions d'éléments logiques et 6 milliards de transistors qui, bien que j'y travaille depuis tout ce temps, m'étonnent. La puce est fabriquée et testée conformément à la norme automobile AEC Q100.

Je voudrais juste faire le tour de la puce et expliquer toutes ses parties. J'irai dans le même ordre que le pixel provenant de la caméra. Dans le coin supérieur gauche, vous pouvez voir l'interface de la caméra. Nous pouvons prendre 2,5 milliards de pixels par seconde, ce qui est plus que suffisant pour tous les capteurs disponibles. Un réseau qui distribue les données d'un système de mémoire aux contrôleurs de mémoire sur les bords droit et gauche de la puce. Nous utilisons le LPDDR4 standard fonctionnant à une vitesse de 4266 gigabits par seconde. Cela nous donne un débit maximum de 68 gigaoctets par seconde. Il s'agit d'une bande passante assez bonne, mais pas excessive, nous essayons de rester au milieu. Le processeur de traitement d'image dispose d'un pipeline interne de 24 bits, ce qui nous permet d'utiliser pleinement les capteurs HDR qui se trouvent dans la voiture. Il effectue une cartographie avancée des tons, ce qui permet de mieux mettre en évidence les détails et les ombres, et effectue également une réduction avancée du bruit, ce qui améliore simplement la qualité globale des images que nous utilisons dans un réseau de neurones.

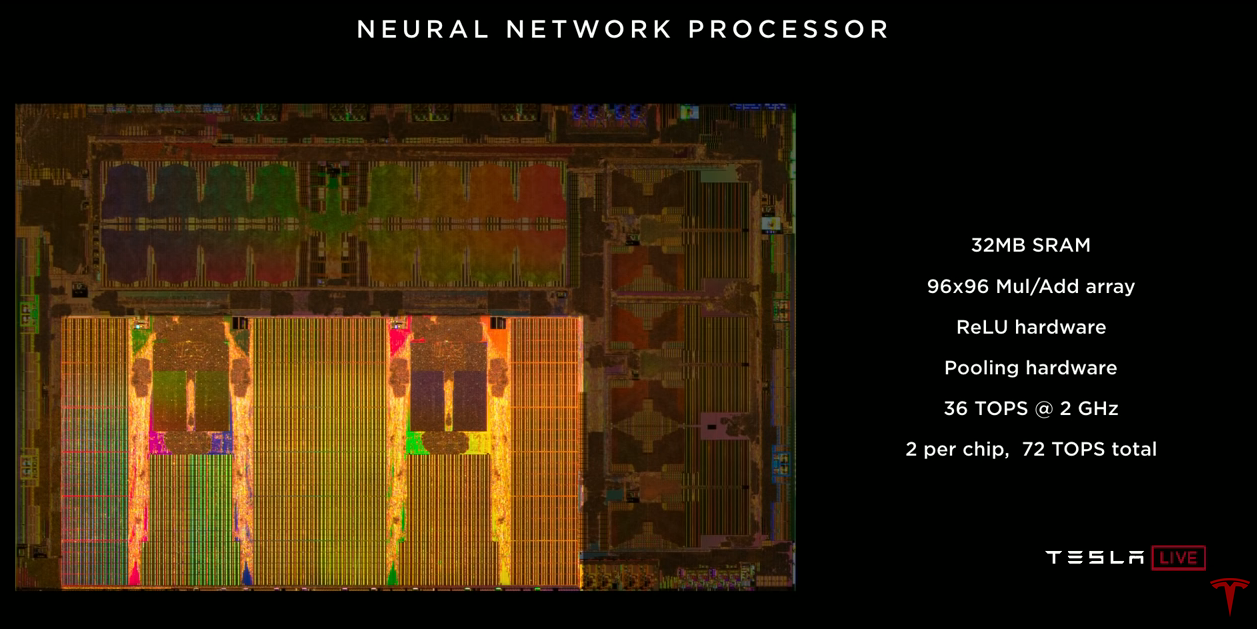

L'accélérateur de réseau neuronal lui-même. Il y en a deux sur la puce. Chacun d'eux dispose de 32 mégaoctets de mémoire SRAM pour stocker les résultats temporaires. Cela minimise la quantité de données que nous devons transférer sur la puce et vice versa, ce qui contribue à réduire la consommation d'énergie. Chacun contient un tableau de multiplicateurs 96x96 avec accumulation, ce qui nous permet de faire près de 10 000 opérations MUL / ADD par cycle. Il existe un accélérateur ReLU dédié, un accélérateur de pooling. Chacun d'eux fournit 36 billions d'opérations par seconde fonctionnant à une fréquence de 2 GHz. Deux accélérateurs sur une puce donnent 72 000 milliards d'opérations par seconde, ce qui est nettement supérieur à l'objectif de 50 000 milliards.

L'encodeur vidéo, la vidéo à partir de laquelle nous utilisons dans la voiture pour de nombreuses tâches, y compris la sortie d'images de la caméra de recul, l'enregistrement vidéo et également pour l'enregistrement de données dans le cloud, Stuart et Andrew en parleront plus tard. Un processeur graphique assez modeste est situé sur la puce. Il prend en charge les nombres à virgule flottante 32 et 16 bits. Également 12 processeurs A72 polyvalents 64 bits. Ils fonctionnent à une fréquence de 2,2 GHz, soit environ 2,5 fois plus que les performances de la solution précédente. Le système de sécurité contient deux processeurs qui fonctionnent en mode verrouillage. Ce système prend la décision finale de savoir s’il est sûr de transmettre des signaux de commande aux entraînements du véhicule. C'est là que les deux avions se rencontrent et nous décidons s'il est sûr d'avancer. Et enfin, un système de sécurité dont la tâche est de s'assurer que seule la puce du logiciel Tesla signé cryptographiquement est utilisée sur cette puce.

Je vous ai parlé de nombreux indicateurs de performance différents, et je pense qu'il serait utile d'envisager l'avenir. Nous considérerons un réseau neuronal de notre caméra (étroite). Il faut 35 milliards d'opérations. Si nous utilisons les 12 CPU pour traiter ce réseau, nous pouvons faire 1,5 images par seconde, c'est très lent. Absolument pas assez pour conduire une voiture. Si nous utilisions des GPU avec 600 GFLOP pour le même réseau, nous obtiendrions 17 images par seconde, ce qui n'est pas encore suffisant pour conduire une voiture avec 8 caméras. Notre accélérateur de réseau neuronal peut produire 2100 images par seconde. Vous pouvez voir que la quantité de calcul dans le CPU et le GPU est négligeable par rapport à l'accélérateur de réseau neuronal.

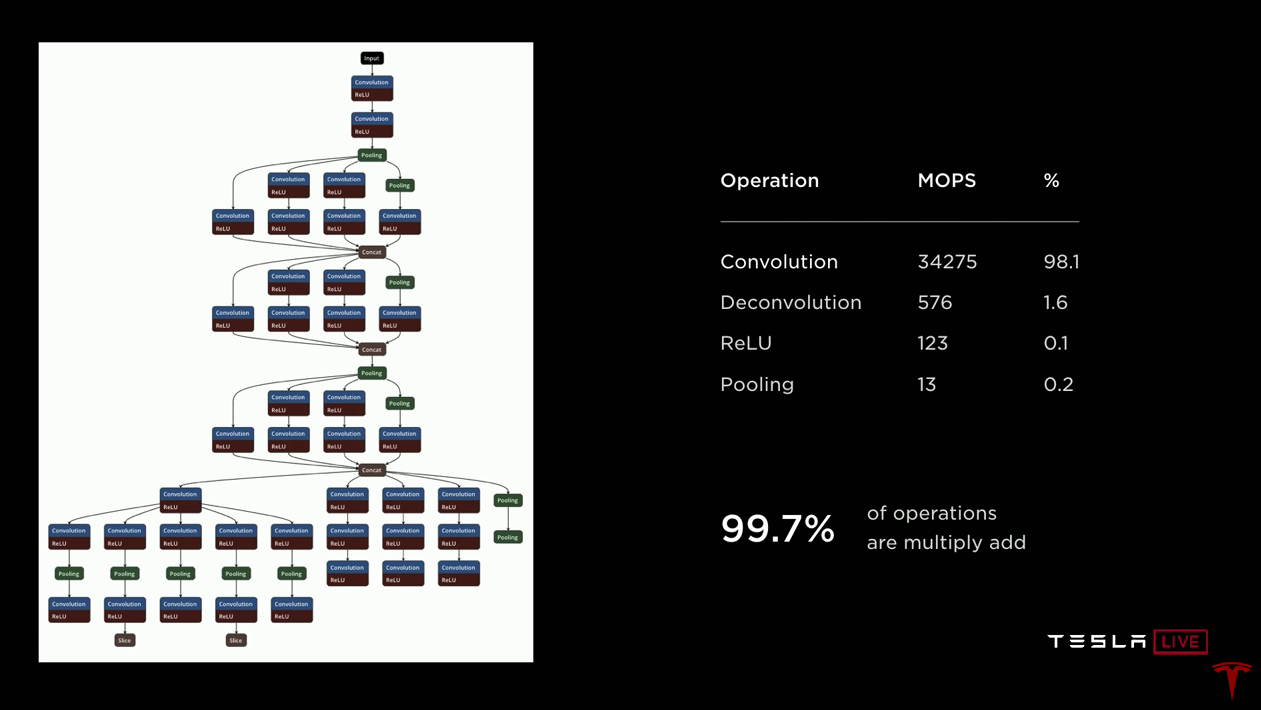

Passons maintenant à un accélérateur de réseau neuronal. Je ne bois que de l'eau. Sur la gauche, voici un dessin d'un réseau de neurones pour vous donner une idée de ce qui se passe. Les données arrivent en haut et traversent chacun des blocs. Les données sont transmises le long des flèches vers différents blocs, qui sont généralement des convolutions ou des convolutions inverses avec des fonctions d'activation (ReLU). Les blocs verts combinent des couches. Il est important que les données reçues par un bloc soient ensuite utilisées par le bloc suivant, et que vous n'en ayez plus besoin - vous pouvez les jeter. Ainsi, toutes ces données temporaires sont créées et détruites lors du passage sur le réseau. Il n'est pas nécessaire de les stocker en dehors de la puce dans la DRAM. Par conséquent, nous ne les stockons que dans SRAM, et dans quelques minutes, je vais expliquer pourquoi cela est très important.

Si vous regardez du côté droit, vous verrez que dans ce réseau de 35 milliards d'opérations, presque toutes sont des convolutions, essentiellement des produits scalaires, le reste est une déconvolution (convolutions inverses), également basée sur le produit scalaire, puis ReLU et la mise en commun sont relativement simples opérations. Par conséquent, si vous développez un accélérateur, vous vous concentrez sur la mise en œuvre de produits scalaires basés sur l'addition avec accumulation et les optimisez. Mais imaginez que vous accélérez cette opération de 10 000 fois et que 100% se transforment en 0,1%. Du coup, les opérations de ReLU et de mise en commun deviennent très importantes. Par conséquent, notre implémentation comprend des accélérateurs dédiés pour le traitement et la mise en commun ReLU.

La puce fonctionne avec un budget thermique limité. Nous devions être très prudents sur la façon dont nous consommons de l'énergie. Nous voulons maximiser la quantité d'arithmétique que nous pouvons faire. Par conséquent, nous avons choisi l'ajout d'entiers 32 bits, il consomme 9 fois moins d'énergie que l'addition en virgule flottante. Et nous avons choisi la multiplication entière sur 8 bits, qui consomme également beaucoup moins d'énergie que les autres opérations de multiplication, et a probablement suffisamment de précision pour obtenir de bons résultats. Quant à la mémoire. L'accès à la DRAM externe est environ cent fois plus cher en termes de consommation d'énergie que l'utilisation de la SRAM locale. Il est clair que nous voulons tirer le meilleur parti de la SRAM locale.

Du point de vue de la gestion, voici les données qui ont été publiées dans un article de Mark Horowitz, où il a examiné de manière critique la quantité d'énergie nécessaire pour exécuter une seule instruction sur un processeur entier normal. Et vous voyez que l'opération d'addition ne consomme que 0,15% de la puissance totale. Tout le reste est des frais généraux pour la gestion et plus encore. Par conséquent, dans notre conception, nous nous efforçons de nous débarrasser de tout cela autant que possible. Ce qui nous intéresse vraiment, c'est l'arithmétique.

Voici donc le design que nous avons terminé. Vous pouvez voir que la place principale est occupée par 32 mégaoctets de SRAM, ils sont à gauche, à droite, au centre et en bas. Tous les calculs sont effectués dans la partie centrale supérieure. Chaque cycle, nous lisons 256 octets de données d'activation de la matrice SRAM, 128 octets de poids de la matrice SRAM et les combinons dans une matrice 96x96, qui effectue 9000 ajouts avec une accumulation par cycle à 2 GHz. Ce n'est que 36,8 billions. opérations. Maintenant que nous avons terminé avec le produit scalaire, nous téléchargeons les données, les transmettons à travers la ReLU dédiée, éventuellement en tirant, et enfin les mettons dans le tampon d'écriture, où tous les résultats sont agrégés. Et puis nous réécrivons 128 octets par horloge dans SRAM. Et tout cela se produit en continu. Nous travaillons avec des produits scalaires, pendant que nous déchargeons les résultats précédents, effectuons l'extraction et réécrivons les résultats en mémoire.

Si vous empilez le tout à 2 GHz, vous aurez besoin de 1 téraoctet par seconde de bande passante SRAM pour prendre en charge le fonctionnement. Et le fer fournit cela. Un téraoctet par seconde de bande passante par accélérateur, deux accélérateurs par puce - deux téraoctets par seconde.L'accélérateur a un ensemble de commandes relativement petit. Il existe une opération de lecture DMA pour charger les données de la mémoire, une opération d'écriture DMA pour télécharger les résultats en mémoire. Trois instructions de convolution (convolution, déconvolution, produit intérieur). Deux opérations relativement simples sont le décalage et le fonctionnement élément par élément (eltwise). Et bien sûr, l'arrêt de l'opération lorsque les calculs sont terminés.Nous avons dû développer un compilateur de réseau neuronal. Nous avons pris un réseau de neurones formé par notre équipe de développement, sous la forme sous laquelle il était utilisé dans l'ancien matériel. Lorsque vous le compilez pour une utilisation sur un nouvel accélérateur, le compilateur effectue la fusion des couches, ce qui nous permet d'augmenter le nombre de calculs pour chaque appel à SRAM. Il effectue également le lissage des accès mémoire. Nous effectuons un remplissage de canal pour réduire les conflits entre les banques de mémoire. L'allocation de mémoire prend également en compte les banques SRAM. C'est le cas lorsque le traitement des conflits peut être implémenté dans le matériel. Mais avec l'implémentation logicielle, nous économisons sur le matériel en raison d'une certaine complexité logicielle. Nous insérons également automatiquement les opérations DMA afin que les données arrivent pour les calculs à temps, sans arrêter le traitement. À la fin, nous générons le code,pondère les données, compresse et ajoute une somme de contrôle CRC pour plus de fiabilité. Le réseau de neurones est chargé dans SRAM au démarrage et est là tout le temps.Ainsi, pour démarrer le réseau, vous spécifiez l'adresse du tampon d'entrée, qui contient une nouvelle image qui vient d'arriver de la caméra; définir l'adresse du tampon de sortie; réglez le pointeur sur le poids du réseau; allons-y. L'accélérateur «entre en lui-même» et traversera séquentiellement l'ensemble du réseau neuronal, généralement pendant un ou deux millions de cycles d'horloge. À la fin, vous recevez une interruption et pouvez post-traiter les résultats.Passons aux résultats. Notre objectif était d'atteindre 100 watts. Les mesures sur les voitures qui conduisent avec une pile complète de pilote automatique ont montré que nous dissipons 72 watts. C'est légèrement plus grand que dans le projet précédent, mais une amélioration significative des performances est une bonne excuse. Sur ces 72 watts, environ 15 watts sont consommés dans les réseaux de neurones. Le coût de cette solution représente environ 80% de ce que nous avons payé auparavant. En termes de performances, nous avons pris le réseau neuronal (étroit) de la caméra, que j'ai déjà mentionné, avec 35 milliards d'opérations, nous l'avons lancé sur du vieux matériel et reçu 110 images par seconde. Nous avons pris les mêmes données et le même réseau, les avons compilées pour le nouvel ordinateur FSD et, en utilisant les quatre accélérateurs, nous pouvons traiter 2300 images par seconde.Ilon:Je pense que c'est peut-êtrela diapositive la plus importante de Pete: je n'ai jamais travaillé sur un projet où l'amélioration de la productivité était supérieure à 3. Donc, c'était assez amusant. Par rapport à la solution nvidia Drive Xavier, la puce fournit 21 billions de dollars. opérations, tandis que notre FSDC avec deux puces - 144 billions. opérations.Donc, en conclusion, je pense que nous avons créé une solution qui offre des performances exceptionnelles de 144 billions. opérations de traitement d'un réseau neuronal. Il a des caractéristiques de puissance exceptionnelles. Nous avons réussi à intégrer toute cette productivité dans le budget de chaleur que nous avions. Cela vous permet de mettre en œuvre une solution de duplication. L'ordinateur a un coût modéré, et ce qui est vraiment important, le FSDC fournira un nouveau niveau de sécurité et d'autonomie dans les voitures Tesla, sans affecter leur coût et leur kilométrage. Nous l'attendons tous avec impatience.Ilon: Si vous avez des questions sur l'équipement, posez-les dès maintenant.La raison pour laquelle j'ai demandé à Pete de faire une analyse détaillée, beaucoup plus détaillée que la plupart des gens auraient peut-être apprécié de plonger dans un ordinateur Tesla FSD, est la suivante. À première vue, il semble incroyable de voir comment Tesla, qui n'avait jamais conçu de telles puces auparavant, a créé la meilleure puce du monde. Mais c'est exactement ce qui s'est passé. Et pas seulement le meilleur par une petite marge, mais le meilleur par une énorme marge. Tous les Tesla fabriqués actuellement ont cet ordinateur. Nous sommes passés de la solution Nvidia pour S et X il y a environ un mois et avons changé de modèle 3 il y a une dizaine de jours. Toutes les voitures produites ont tout le matériel nécessaire et tout le nécessaire pour une conduite entièrement autonome. Je le répète: toutes les voitures Tesla produites maintenant,avoir tout ce dont vous avez besoin pour une conduite entièrement autonome. Tout ce que vous avez à faire est d'améliorer le logiciel. Plus tard dans la journée, vous pourrez conduire des voitures avec une version destinée aux développeurs de logiciels de conduite autonome améliorés. Vous verrez par vous-même. Des questions.Q: avez-vous la possibilité d'utiliser des fonctions d'activation autres que ReLU?Pete: oui, nous avons un sigmoïde, par exempleQ: cela valait peut - être la peine de passer à un processus de fabrication plus compact, peut-être 10 nm ou 7 nm?Pete: au moment où nous avons commencé à concevoir, toutes les IP que nous voulions obtenir n'étaient pas disponibles enIlon 10 nm : il convient de noter que nous avons terminé cette conception il y a environ un an et demi et commencé la génération suivante. Aujourd'hui, nous ne parlons pas de la prochaine génération, mais nous sommes déjà à mi-chemin. Tout cela est évident pour la puce de prochaine génération, nous le faisons.Q: L' ordinateur est conçu pour fonctionner avec des caméras. Puis-je l'utiliser avec du lidar?Ilon:Lidar est une décision désastreuse, et toute personne qui dépend du lidar est condamnée. Doomed. Cher Chers capteurs qui ne sont pas nécessaires. C'est comme avoir un tas d'applications inutiles coûteuses. Un petit n'est rien, mais un groupe est déjà un cauchemar. C'est stupide, tu verras.Q: Pouvez-vous évaluer l'impact de la consommation d'énergie sur le kilométrage?Pete: Pour le modèle 3, la consommation cible est de 250 watts par mile.Ilon:Dépend de la nature de la conduite. En ville, l'effet sera beaucoup plus important que sur l'autoroute. Vous conduisez en ville pendant une heure et vous avez une solution hypothétique qui consomme 1 kW. Vous perdrez 6 km sur le modèle 3. Si la vitesse moyenne est de 25 km / h, vous perdez 25%. La consommation du système a un impact énorme sur le kilométrage dans une ville où nous pensons qu'il y aura une grande partie du marché de robotax, donc la puissance est extrêmement importante.Q: Quelle est la fiabilité de votre technologie en termes d'IP, n'allez-vous pas donner gratuitement l'IP?Pete: Nous avons déposé une douzaine de brevets pour cette technologie. Il s'agit essentiellement d'algèbre linéaire, que je ne pense pas que vous puissiez breveter. (Ilon rit)Q:votre microcircuit peut faire quelque chose, peut-être crypter tous les poids pour que votre propriété intellectuelle reste à l'intérieur, et personne ne peut simplement le voler.Ilon: Oh, j'aimerais rencontrer quelqu'un qui peut le faire. Je l'embaucherais en un instant. C'est un problème très difficile. Même si vous pouvez extraire les données, vous aurez besoin d'une énorme quantité de ressources pour les utiliser d'une manière ou d'une autre.Le gros avantage durable pour nous est la flotte. Personne n'a de flotte. Les poids sont constamment mis à jour et améliorés en fonction des milliards de kilomètres parcourus. Tesla possède cent fois plus de voitures avec le matériel nécessaire à la formation que toutes les autres combinées. D'ici la fin de ce trimestre, nous aurons 500 000 véhicules avec 8 caméras et 12 capteurs à ultrasons. Dans un an, nous aurons plus d'un million de voitures avec FSDC. C'est juste un énorme avantage de données. Cela est similaire à la façon dont le moteur de recherche Google a un énorme avantage, car les gens l'utilisent et les gens forment réellement Google avec leurs requêtes.Hôte:Une chose à retenir à propos de notre FSD est qu'il peut fonctionner avec des réseaux de neurones beaucoup plus complexes pour une reconnaissance d'image beaucoup plus précise. Il est temps de parler de la façon dont nous obtenons réellement ces images et de la façon dont nous les analysons. Ici, nous avons un directeur principal de l'IA - Andrey Karpaty, qui vous expliquera tout cela. Andrei est titulaire d'un doctorat de l'Université de Stanford, où il a étudié l'informatique en mettant l'accent sur la reconnaissance et l'apprentissage profond.Ilon: Andrey, pourquoi ne commencez-vous pas, allez. Beaucoup de médecins sont sortis de Stanford, peu importe. Andrey enseigne un cours de vision par ordinateur à Stanford, ce qui est beaucoup plus important. Veuillez parler de vous.

(La traduction ne s'est pas avérée assez rapide, je ne sais pas si j'en ai assez pour la deuxième partie sur le système d'entraînement du réseau neuronal, bien que cela me semble le plus intéressant.)