Une petite introduction:

L'idée d'écrire votre propre noyau est venue après avoir passé un séminaire-école sur les circuits numériques dans la ville de Tomsk . Lors de cet événement, familiarisation avec les langages de description du matériel actuels (Verilog HDL et VHDL), ainsi qu'avec un petit processeur core schoolMIPS . Pour comprendre la structure des noyaux, il a été décidé d'inventer leur propre vélo, en suivant le chemin du développement de schoolMIPS, mais en prenant un autre système de commande comme base. En raison de la popularité croissante de RISC-V et de l'ouverture de son système de commande (MIPS n'avait pas de système de commande ouvert au moment de l'écriture du noyau), un ensemble d'instructions RISC-V, à savoir RV32I, a été choisi pour le développement du futur noyau. RV32I possède un petit ensemble d'instructions de base (37 à l'exception des instructions spéciales) et, si vous le souhaitez, il peut être étendu, par exemple, en ajoutant des instructions de multiplication et de division entières (RV32M) ou la prise en charge des instructions compressées (RV32C). De plus, ce projet a été conçu comme éducatif, il a donc été décidé de maximiser la visibilité du noyau pour démontrer efficacement son travail.

Par analogie avec schoolMIPS, les versions de noyau suivantes ont été implémentées:

- Version à cycle unique (00_simple_risc_v_cpu).

- Une version à cycle unique avec prise en charge des instructions lw / sw (mot de chargement / mot de stockage) (01_simple_risc_v_cpu_lwsw).

- Version pipeline (convoyeur à 5 étages) (02_pipe_risc_v_cpu).

Actuellement, la prochaine version du noyau est décrite (03_pipe_risc_v_cpu_fc) avec un ensemble complet de commandes RV32I (sans prendre en compte certaines spéciales).

Au cours de la description du noyau, des moyens d'améliorer la visibilité du travail, le débogage et la vérification ont été pensés. Actuellement mis en œuvre les méthodes suivantes:

Ajout d'un module VGA de texte de débogage (pour deux branches de noyau à cycle unique). L'inclusion de ce module vous permet de suivre simultanément la valeur de 32 registres sur l'écran du moniteur, ce qui n'est pas possible lorsque vous utilisez la sortie d'informations sur des indicateurs à sept segments. Dans les figures présentées ci-dessous, le noyau calcule les nombres Leonardo et affiche des informations sur le module de débogage correspondant;

hex_display et DebugScreenCoreProduction d'informations sur les indicateurs à sept segments:

Sortie d'informations sur l'écran VGA:

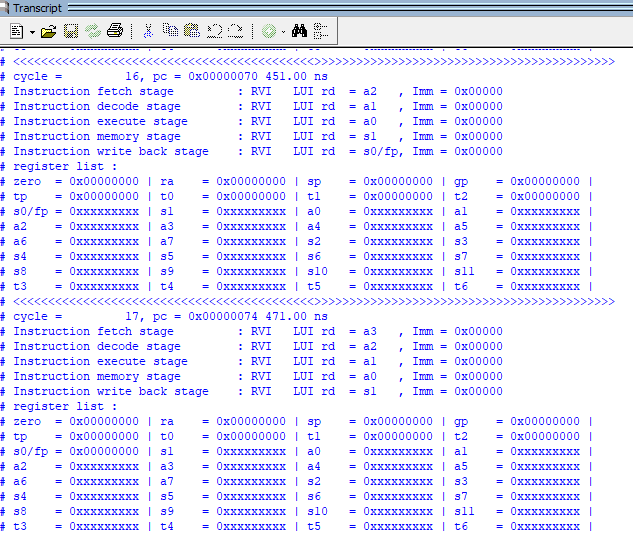

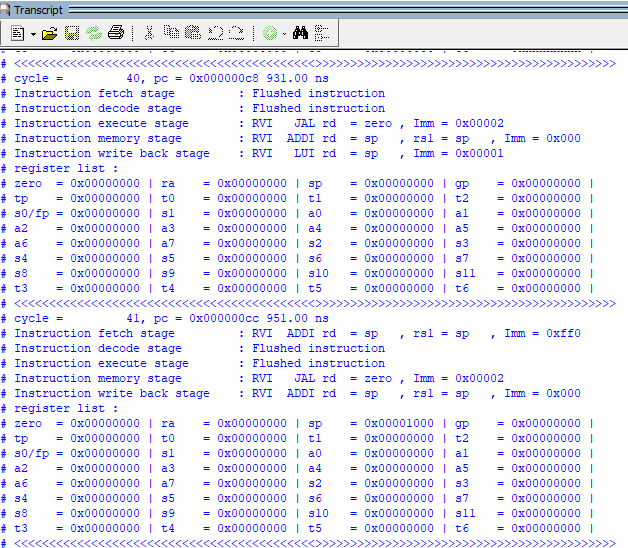

Ajout de messages au terminal de simulation sur l'état du fichier de registre et l'exécution actuelle des instructions. Cette méthode vous permet de mieux analyser le fonctionnement du noyau dans les premiers stades de développement, mais n'est pas toujours pratique;

TerminalInitialisation du fichier de registre:

Modifier la valeur sp:

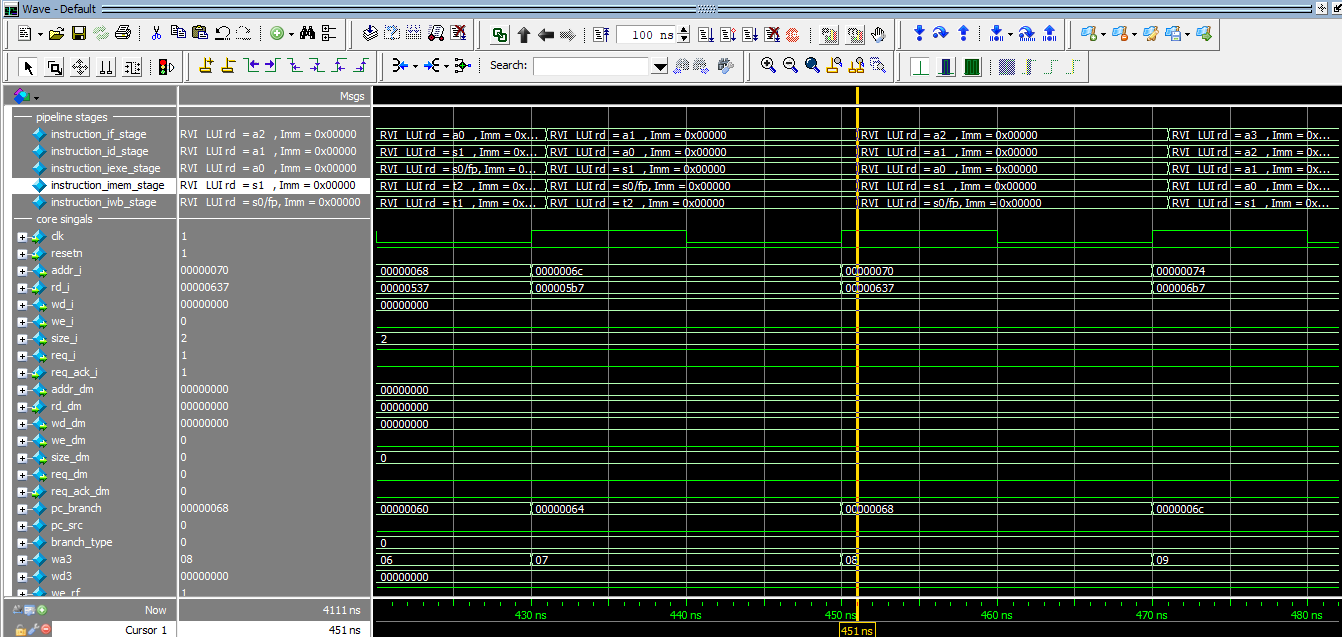

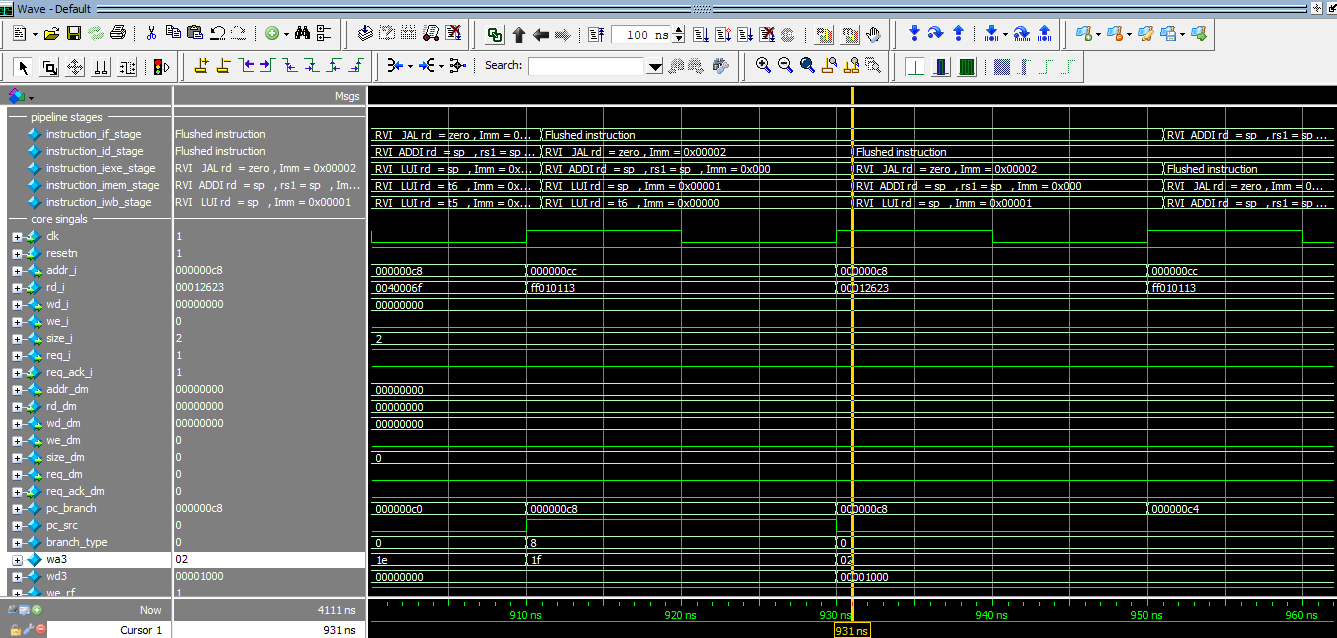

Ajout de variables de chaîne à la forme d'onde avec l'affichage d'instructions exécutables. En utilisant ces variables de chaîne, le développeur peut suivre le réglage correct des signaux de contrôle à toutes les étapes du pipeline;

Forme d'ondeInitialisation du fichier de registre:

Modifier la valeur sp:

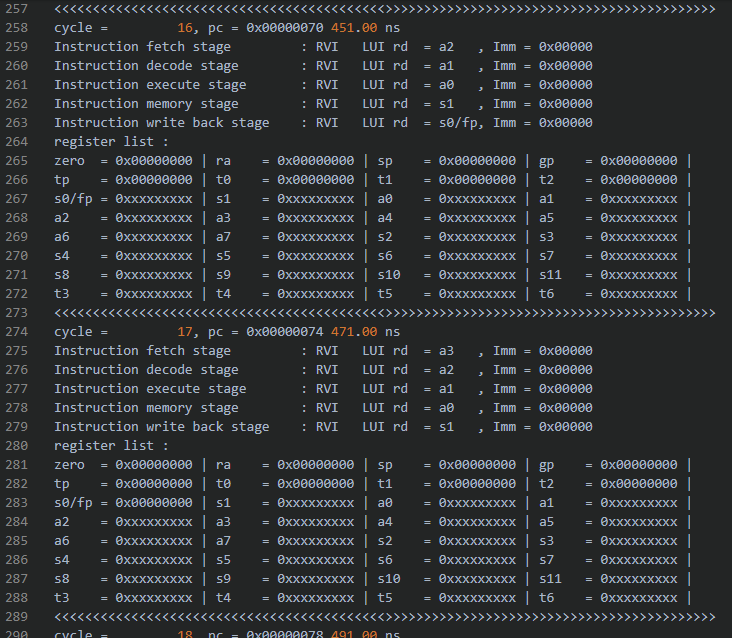

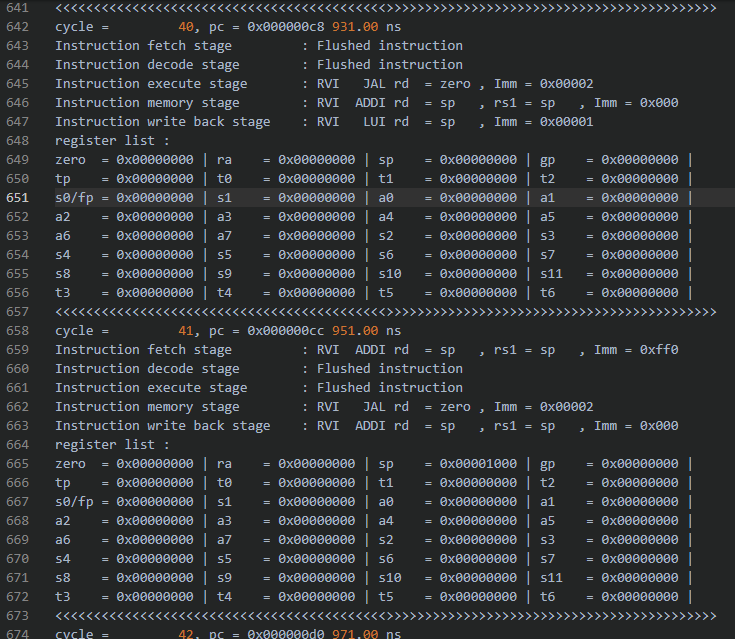

Ajout de la possibilité d'écrire des informations de débogage sur l'état du noyau dans un fichier texte. L'état du fichier de registre est présenté sous forme de tableau, et les instructions actuellement exécutées par le noyau sont également indiquées. C'est un analogue de 2 points, mais permet plus de manipulations avec les informations reçues;

Fichier texteInitialisation du fichier de registre:

Modifier la valeur sp:

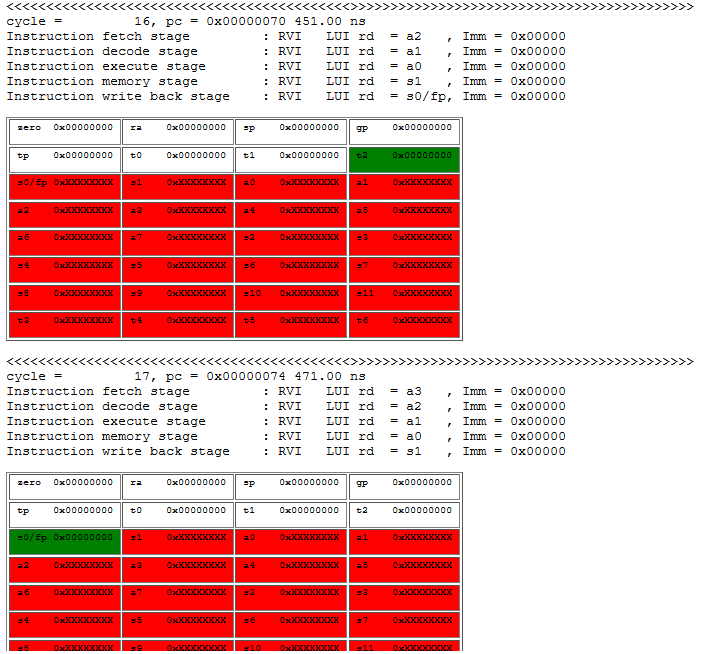

Ajout de la possibilité d'écrire des informations de débogage sur l'état du noyau dans un fichier HTML. L'état du fichier de registre est présenté sous forme de tableau avec des notes sur la modification des valeurs des cellules, ainsi que les instructions en cours d'exécution par le noyau sont affichées. Il s'agit d'un analogue des paragraphes 2 et 4, mais en plus de cela, il vous permet d'indiquer facilement une modification des données. Comme on peut le voir sur les images ci-dessous, si la valeur du registre n'a pas été définie, les registres sont surlignés en rouge (registres s0 / fp - t6). Au cycle 17, la valeur du registre s0 / fp change et la cellule est surlignée en vert.

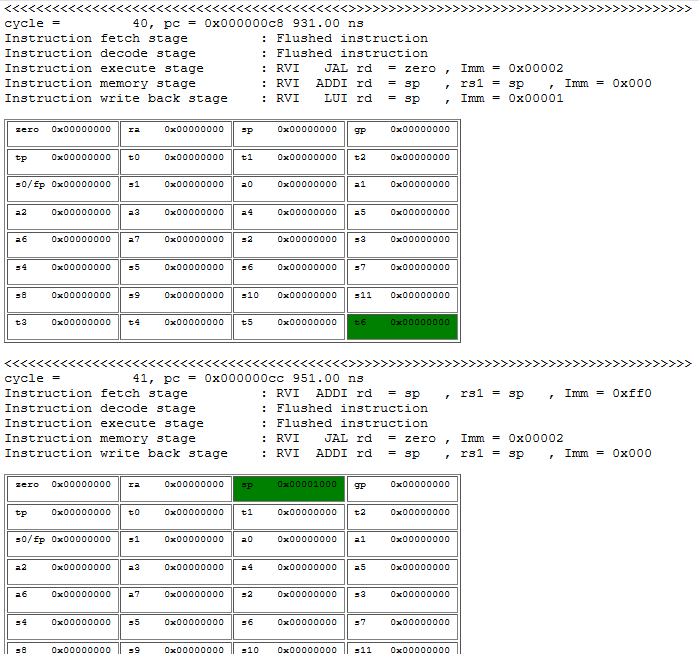

Au cycle 41, la valeur 0x00010000 est chargée dans le registre sp.

Fichier HTMLInitialisation du fichier de registre:

Modifier la valeur sp:

Comparaison des branches du noyau:Instructions du noyau actuellement prises en charge pour différentes branches:

Périphériques pris en charge:

Langues prises en charge pour l'écriture de programmes:

Ressources FPGA requises pour le noyau (nf_cpu):

EP4CE22F17C6 (de0_nano):

10M50DAF484C7G (de10_lite):

Développement de projet.

Ce qui devrait être fait à l'avenir:

- ajouter toutes les instructions RV32I (au stade de la description);

- implémenter le débogage;

- ajouter un contrôleur DMA (DMA);

- ajouter le support pour d'autres pneus AXI, Avalon, Wishbone;

- ajouter de la mémoire cache (cache);

- intégrer divers périphériques (SPI, TWI (I2C), Ethernet (10 base-t));

- ajouter un contrôleur d'interruption;

- porter différentes versions sur d'autres cartes de débogage;

- ajouter d'autres méthodes pour augmenter la visibilité du noyau;

- exécutant RTOS, par exemple zephyr .

Les recommandations et suggestions pour le développement du noyau sont également acceptées.

Lien vers le référentiel: nanoFOX .