Je souhaite la bienvenue à tous.

Suite aux traces des précédents articles sur les analyseurs logiques sur Habré, j'ai décidé de terminer mon travail "fondamental".

Je vais commencer un peu de loin.

Tout a commencé au début des années 10, lorsque j'ai découvert Saleae Logic (ci-après dénommé Saleae, je veux dire un analyseur à 8 canaux sans curseur) sur un forum de radio amateur.

A pris note. Mais déjà à 13 ans dans le processus de mise en œuvre d'un autre projet, je suis tombé sur le fait que j'avais vraiment besoin d'un analyseur logique avec un grand tampon. L'oscilloscope et le hanteck la-5034 disponibles à l'époque ne résolvaient pas le problème.

La principale caractéristique de Saleae et de ses clones est le manque de tampon intégré - le flux entier est immédiatement poursuivi sur le PC et y est enregistré. Il peut ensuite être analysé, décodé et exporté. D'une part, nous sommes pratiquement illimités en profondeur de visualisation (les données peuvent être stockées pendant des heures), d'autre part, la fréquence d'échantillonnage maximale est de 24 MHz. Dans la plupart des cas, cependant, en raison de la nature programmatique de l'échantillonnage, les échantillons ont une "gigue" notable.

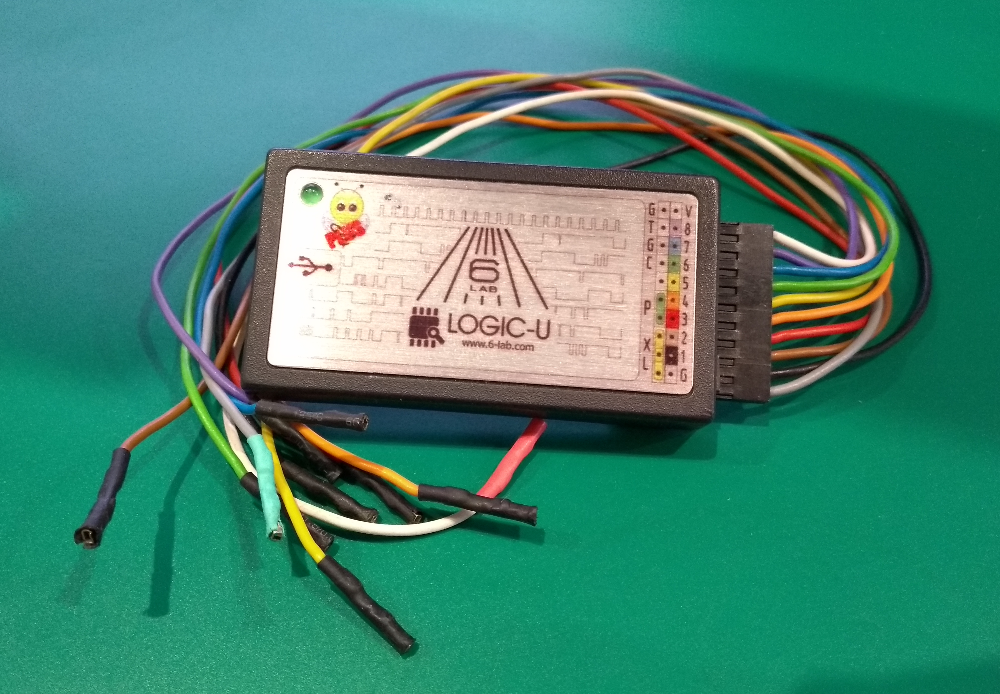

En conséquence, très rapidement, en une journée environ, depuis Kharkov, du 6-lab (maintenant décédé), ils m'ont envoyé via des clones leur clone de saleae avec deux eeproms déjà intégrés pour changer les types de saleae et xbee (le matériel de ces appareils est le même, seule la vidéo diffère: pid qui sont flashés en eeprom).

En conséquence, vous pouvez utiliser des logiciels des deux fabricants.

C'est alors que je me suis intéressé à une chose telle que Y7C68013A, enfin, ou plus courte que FX2 (bien qu'elle soit plus correcte que FX2LP).

Il s'agit d'un microcontrôleur compatible 8051 avec un port matériel USB 2.0 et honnête 480 Mb / s.

Les fonctionnalités incluent: 16 Ko de RAM et la possibilité de télécharger le firmware à la fois à partir d'une EEPROM I2C connectée et via USB (il n'y a pas de flash intégré).

Et ce MK peut prétendre être n'importe quel appareil sur le bus USB (dans le sens de répondre à n'importe quel VID: PID).

Quelques détails de la fiche technique sur la procédure de chargement

Considérez le cas où une EEPROM I2C est connectée au MK.

Dans ce cas, les 8 premiers octets en sont analysés:

Si le premier octet est 0xC0 (comme dans le firmware du clone Saleae), le MK configure le port USB avec le VID: PID spécifié dans 1-4 octets et attend que le firmware soit téléchargé via USB. Selon le VID flashé: PID MK peut "être" un autre appareil, au moins Saleae au moins Xbee au moins par quelqu'un. Très confortable. Vous pouvez souder les EEPROM dans une pile et sélectionner avec un cavalier.

Mais si le premier octet est 0xC2, à partir de 9 octets, le firmware pour MK doit être stocké dans l'EEPROM, qu'il chargera dans la RAM et commencera à s'exécuter.

Le format de stockage est similaire à HEX d'Intel:

Autrement dit, le micrologiciel est divisé en blocs qui sont chargés individuellement dans différentes sections de la mémoire. Et en conséquence, cela n'a aucun sens de stocker des zones vides.

Et maintenant, nous approchons en douceur du personnage principal de notre article DreamSourseLab.

Je ne raconterai pas toute l'histoire (je ne le sais pas vraiment et je ne vois pas de sens plus profond). Ce sont trois ingénieurs qui, grâce au crowdfunding, ont vu (presque) le projet de l'analyseur de rêve logique.

Qu'ont-ils fait?

Ils ont ajouté au FX2 une plisina bon marché - Spartan 6 (peut-être espionné sur Saleae).

Et c'est 16 canaux à la fois, ce sont des points d'échantillonnage clairs, c'est la possibilité de compresser des bits individuels (deux lignes peuvent être échantillonnées 4 fois plus souvent que 8, l'essentiel est de rester dans la bande passante USB). C'est l'occasion d'enregistrer dans le tampon à haute fréquence (400 MHz / 4 canaux, 200 MHz / 8 canaux, 100 MHz / 16 canaux), puis de le transférer lentement vers un PC. Et si vous vissez sigrok avec sa base la plus puissante de protocoles décodés. En général, le projet a démarré - tout le monde est content. Et compte tenu du fait que les auteurs ont enregistré le mode de flux (sans enregistrer dans le tampon interne), nous avons obtenu un analyseur de rêve logique (enfin, presque parce que je voulais immédiatement 32 canaux et FX3).

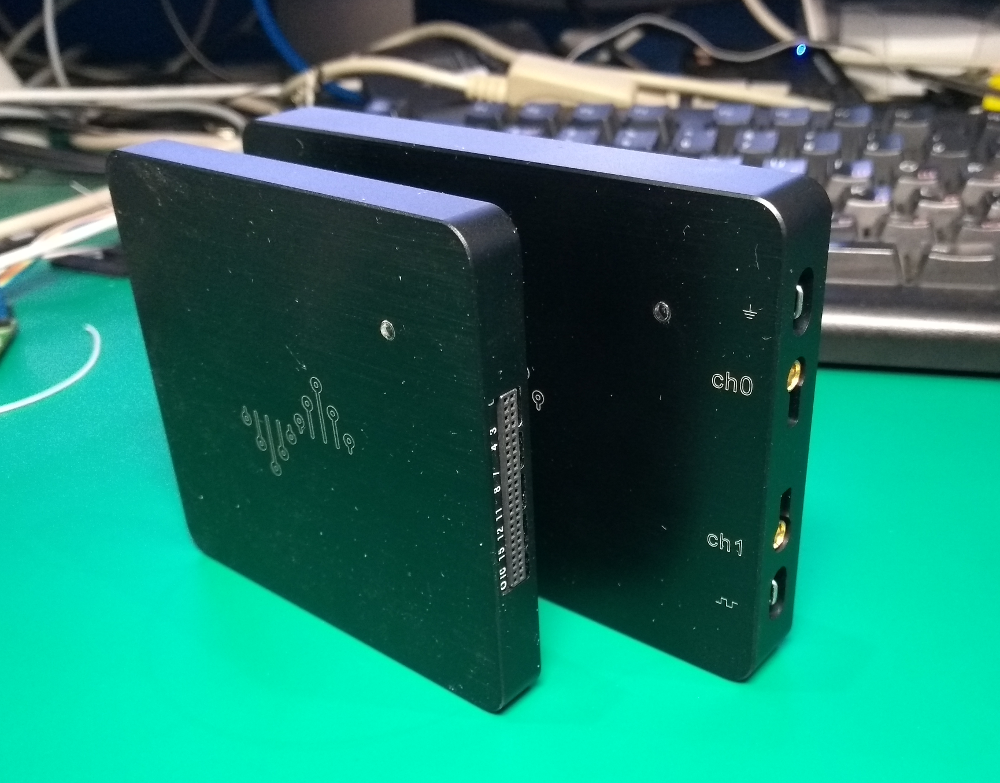

Ainsi est apparu DSLogicPro. Boîtier en aluminium noir strict avec connecteur USB-C.

Et puis les ingénieurs ont frappé l'entreprise. Et ils ont sorti des boîtes avec le nom DSLogicBase et DSLogicPlus (si je comprends bien pour conquérir le monde via des sites chinois), ainsi que DSCope (nous suspendons quelques ADC 8 bits et nous avons maintenant un oscilloscope à deux canaux).

Eh bien, pour garder ce processus sous contrôle strict, nous avons légèrement modifié la disposition de la carte. Autrement dit, le DSLogicPlus et le DSLogicPro sont identiques sur le plan électrique et fonctionnel, mais la SRAM se bloque sur la fiche des autres broches (cela se voit clairement dans l'image des pistes). Je soupçonne que des améliorations ont été apportées ailleurs.

Soit dit en passant, une révision très utile a été faite en termes de câble pour connecter les signaux étudiés. Si dans Pro, les 16 lignes sont connectées simultanément avec un connecteur large, alors dans Plus, tous les câbles ont été divisés en groupes de 4 canaux qui peuvent être connectés séparément. Eh bien, les câbles eux-mêmes sont courts, coaxiaux et au lieu de couper (où le coaxial est divisé en un signal séparé et des fils communs), il y a une petite écharpe avec un filtre.

Et donc, au printemps 17, j'ai commandé DSLogicBase en Chine (malheureusement, je ne savais pas tout ce que j'avais écrit à l'époque). Ils m'ont envoyé tout, mais avec impatience le tampon de 64 méga-échantillons, j'ai détordu la carte et j'ai vu un endroit vide. Augmenter rapidement le butchu a rapporté 50% du coût. Et puis il a commencé à étudier la question de transformer ma Base en Plus. C'est précisément la différence entre Base et Plus - la présence d'un tampon séparé. La base utilise la mémoire intégrée au FPGA.

Au cours de l'été 17, sur le chemin du travail et du retour pendant une demi-heure dans le train du MCC, j'ai étudié cette question. Et assez rapidement, il est devenu clair que les différences ne concernaient que la SRAM scellée et une paire d'octets de firmware EEPROM.

Un peu sur ce qui se trouve dans le répertoire DSView / res

Nous avons là un ensemble de fichiers avec des extensions bin et fw.

bin - ce sont des firmware pour plisina. Ils sont chargés au moment du démarrage du programme via fx2.

fw sont des fichiers de firmware binaires pour FX2.

Si vous comparez tous les fichiers fw, il s'avère qu'ils ne diffèrent que par l'octet PID à l'adresse près de la fin.

Autrement dit, les différences entre tous les appareils ne sont que cela et le firmware de la prise (qui, comme je l'ai dit, est chargé au moment de l'initialisation).

La comparaison de fw avec ce qui est écrit dans l'EEPROM (bien sûr, j'ai immédiatement vidé le vidage de mon analyseur) a montré que le firmware déployé est ici.

Si vous déployez le firmware depuis l'EEPROM, alors (pour autant que je m'en souvienne), ils correspondront (pour la version 0.96 du logiciel).

Ainsi, comme déjà écrit sur le hub, il vous suffit de souder la mémoire et de changer 2 octets dans le firmware (dans l'en-tête puis plus loin dans le firmware).

De la même manière, DSCope est finalisé, on double la mémoire et change le PID dans l'EEPROM.

Il y a encore une nuance.

Au fur et à mesure de la sortie de nouvelles versions logicielles (0.96-0.99), les modèles matériels pris en charge ont été ajoutés et le PID de ces modèles a été modifié.

J'ai donc eu une telle tablette:

De plus, une indication est apparue dans le firmware à l'adresse 0x20 pour la version Pro il y en a 5, pour Base et Plus il y en a 6. Il s'agit très probablement de la version de la carte de circuit imprimé.

Soit dit en passant, il existe une autre façon de raffiner. Aucune reprogrammation EEPROM requise. Il suffit de souder SRAM, puis, lors de la compilation de libsigrok4DSL, d'apporter une correction au fichier libsigrok4DSL / hardware / DSL / dsl.h:

Dans la structure décrivant la structure de const statique de l'équipement DSL_profile supported_DSLogic [],

à l'endroit où DSLogic PLus et Base sont décrits, modifiez les champs PID afin que le programme pense qu'il a Base PID 20 et Plus PID 21.

319 {0x2A0E, 0x0020, "DreamSourceLab", "DSLogic PLus", NULL, 320 "DSLogicPlus.fw", 321 "DSLogicPlus.bin", 322 "DSLogicPlus.bin", 323 {CAPS_MODE_LOGIC, 324 CAPS_FEATURE_VTH | CAPS_FEATURE_BUF, 325 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 326 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 327 SR_MB(256), 328 0, 329 DSL_BUFFER100x16, 330 0, 331 0, 332 DSL_STREAM20x16, 333 SR_MHZ(1), 334 SR_Mn(1), 335 0, 336 0} 337 }, 338 339 {0x2A0E, 0x0021, "DreamSourceLab", "DSLogic Basic", NULL, 340 "DSLogicBasic.fw", 341 "DSLogicBasic.bin", 342 "DSLogicBasic.bin", 343 {CAPS_MODE_LOGIC, 344 CAPS_FEATURE_VTH, 345 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 346 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 347 SR_KB(256), 348 0, 349 DSL_STREAM20x16, 350 0, 351 0, 352 DSL_STREAM20x16, 353 SR_MHZ(1), 354 SR_Mn(1), 355 0, 356 0} 357 },

Et votre version d'analyseur avec cette version de DSView fonctionnera comme si vous aviez un vrai Plus.

En attendant, je rêverai d'un tas de Spartan6 + FX3 + DSView.