Vous avez un tel rêve: vous vous retrouvez à un examen ou parlez devant un certain public, et soudain vous vous rendez compte que vous ne vous prépariez pas du tout et maintenant vous allez devoir improviser. C'est dans cette situation, mais pas dans un rêve, mais dans la vraie vie, que j'ai affronté les vacances de mai à Moscou, où j'ai pris l'avion de Californie pour diriger un séminaire de trois jours pour des étudiants soigneusement sélectionnés des principales écoles de physique de Moscou. Sous les auspices de RUSNANO, au gymnase RUT (MIIT) et en présence d'enseignants du MIET, MIREA, MEPhI, MPEI et HSE MIEM.

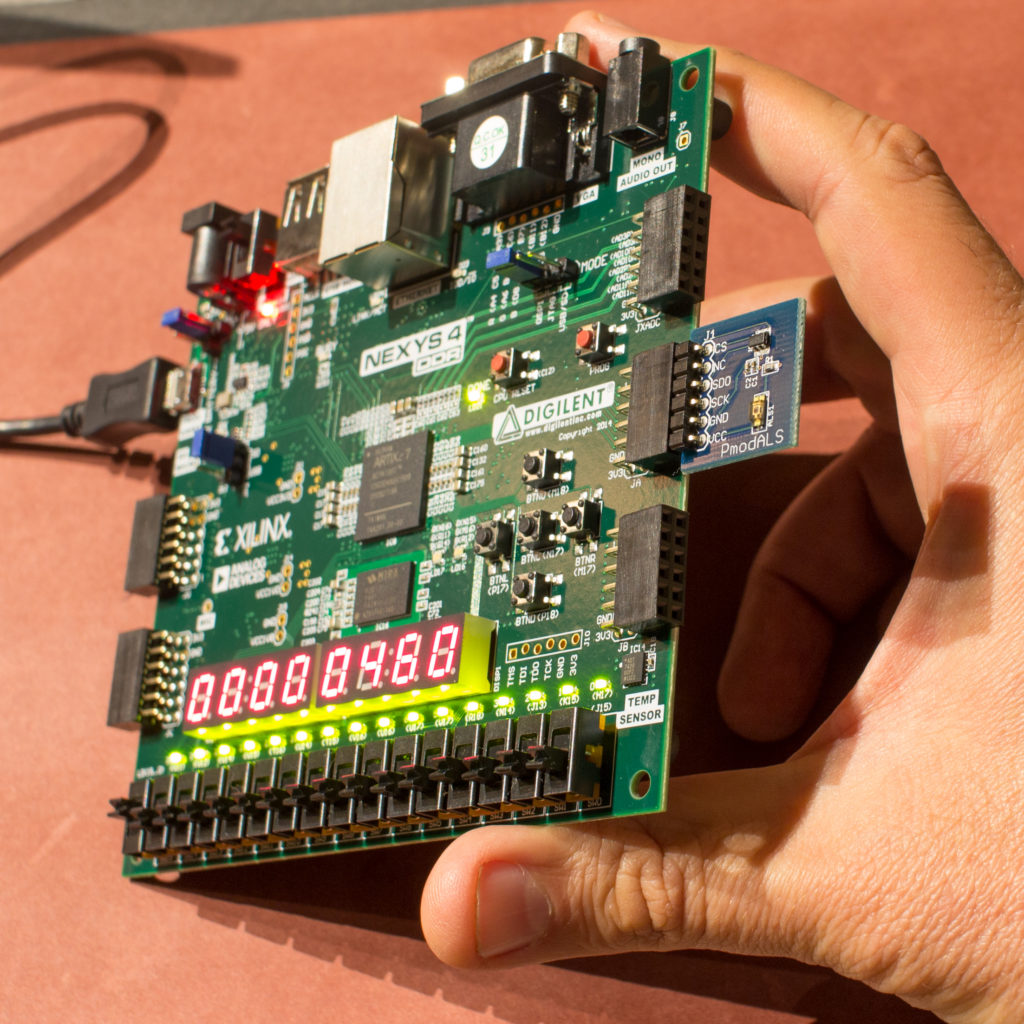

Mes collègues de Moscou espéraient pour moi, et théoriquement j'aurais dû apporter des instructions pas à pas et des exemples de divers exercices sur une carte de circuit imprimé avec un microcircuit logique reconfigurable. En fait, j'avais un tas d'exemples pour d'autres planches, dont je n'ai rien construit dans l'encombrement des vols et autres événements.

Par conséquent, j'ai pris un exemple universel, que j'ai écrit il y a un an et demi, assis dans un avion Alma-Ata-Astana, jeté tous les intérieurs de l'exemple et commencé à le remplir d'écoliers sans plan dur. Et curieusement - cela a fonctionné. Au cours du remplissage, des moments instructifs des circuits numériques et du langage de description du matériel Verilog sont apparus, qui ne se seraient pas produits lors de la planification.

Le 4 juin, mes collègues de Wave Computing et moi-même organiserons un séminaire similaire à Las Vegas, mais uniquement pour les adultes, et du 8 au 19 juillet, j'aiderai MIET à organiser une école d'été à Zelenograd. Plans de ces événements (non définitifs, mais à discuter dans un groupe d'enseignants et d'ingénieurs, y compris ici sur Habré) - à la fin du post.

Pourquoi avons-nous besoin d'un séminaire FPGA pour les écoliers? Les circuits intégrés logiques programmables (FPGA ou FPGA - Field Programmable Gate Arrays) sont un moyen traditionnel de consolider les connaissances dans la pratique lors de l'étude de la conception de circuits numériques au niveau des transferts de registres à l'aide de langages de description matérielle. En d'autres termes, la technologie clé pour développer des iPhones - les micropuces à l'intérieur des iPhones sont conçues de cette façon. Le retard de la Russie derrière les iPhones est également dû au fait que les FPGA, la microarchitecture et les langages de description du matériel ont été introduits à Berkeley et au MIT au début des années 1990, et en Russie en raison de l'effondrement de l'URSS beaucoup plus tard.

Le dernier séminaire de Rosnanov s'est étonnamment bien déroulé, principalement parce que les étudiants qui y ont participé avaient auparavant suivi un cours théorique en ligne avec une enquête axée sur la carrière des méthodes modernes de conception de microcircuits. Le cours en ligne est destiné aux écoliers avancés du type olympiade et se compose de trois modules:

«Du transistor au microcircuit» ,

«Le côté logique des circuits numériques» et

«Le côté physique des circuits numériques» . Dans ce cours, les étudiants se familiarisent avec la soi-disant route RTL2GDSII - un groupe de technologies que les ingénieurs utilisent dans les entreprises électroniques pour concevoir des puces en vrac, des circuits intégrés spécifiques à l'application - ASIC. Les FPGA / FPGA sont utilisés pour prototyper les ASIC, y compris des sociétés comme Intel, Apple et NVidia.

Depuis que les étudiants ont suivi le cours en ligne, ils ont déjà appris ce que sont le déclencheur D, la machine d'état, la synthèse logique et le traçage. Ils ont également vu le langage de description du matériel dans le cours en ligne. Or, cette connaissance, qui restait passivement dans leur mémoire, n'avait qu'à être ravivée.

Maintenant, je vais toujours pour tout séminaire dans les pays de la CEI (en plus des séminaires déjà prévus, j'ai des propositions pour le tenir à Minsk, Sotchi et Yakutsk) pour fixer les conditions pour que la partie hôte pré-admette les écoliers ou les étudiants à travers trois modules du cours en ligne, car après il ne reste que des gens motivés qui ont déjà traversé tous les aspects fastidieux, et la créativité pure reste pour le renforcement, le dernier moment, comme la chute d'une pomme qui a frappé la tête de Newton. De plus, le cours en ligne relie toute cette activité aux professions pour adultes, l'étape suivante, dessine un objectif lointain.

Au total, avant de prendre l'avion pour Moscou, j'ai lancé un exemple universel chez moi à Sunnyvale, en Californie.

Exemple de code :

Le premier jour de l'atelier, nous avons pratiqué avec des microcircuits avec un faible degré d'intégration sur une planche à pain. Cette technologie a 50 ans, mais personne n'a trouvé une meilleure idée, dans la vie réelle, que dans la simulation, de montrer comment les déclencheurs D fonctionnent, par exemple. Bien qu'il semble à de nombreux enseignants de technologie moderne dans les écoles qu'elle est dépassée et inutile, mais maintenant dans le cours 6.111 du Massachusetts Institute of Technology, maintenant, au cours de l'année académique 2018/2019, le premier laboratoire sur les circuits numériques va exactement de cette façon avec des microcircuits avec un faible degré d'intégration - voir

http: //web.mit.edu/6.111/volume2/www/f2018/index.html .

De plus, en utilisant l'exemple de la connexion de microcircuits avec un faible degré d'intégration avec des boutons, il est pratique d'expliquer de quoi il s'agit, pourquoi il est nécessaire et comment fonctionnent les résistances de rappel. Et pourquoi ils donnent un potentiel de 0 lorsque le bouton n'est pas enfoncé, et comment cela est-il lié au diviseur de tension.

Même lorsque, avec l'exemple d'un microcircuit à faible degré d'intégration, la LED s'éteint, les étudiants acquièrent l'expérience de la vie qu'il est nécessaire d'y mettre une résistance. S'ils voient cela sur un écran d'ordinateur dans un simulateur logiciel d'une planche à pain, ils n'obtiendront pas une telle expérience de vie, car vous pouvez dessiner n'importe quoi sur l'écran et les écoliers ne seront pas sûrs que l'épuisement professionnel est vrai.

Voici comment la fonction de la bascule D est clairement visible sur les microcircuits d'un faible degré d'intégration:

Le deuxième jour a commencé par un croquis historique: comment les micropuces ont été conçues il y a 50 ans et comment elles ont changé deux fois depuis. L'une des révolutions s'est superposée à l'effondrement de l'URSS et c'est la principale raison technique pour laquelle la Russie n'a pas d'iPhone.

À 8 h 45, l'histoire de la façon dont l'espion de la bouée soviétique, qui surveillait le mouvement des navires américains, a été pris dans les océans, et à quoi cela a conduit.

Le 13 mars, l'histoire de la façon dont la publication d'un blogueur, John Cooley, a déplacé l'ensemble de l'industrie mondiale de VHDL à Verilog.

Le 16.10, l'histoire de la perte de Microsoft Windows par Linux en tant que plate-forme pour le travail des concepteurs de puces.

Dans cette partie - une démonstration de la façon d'exécuter un programme pour la synthèse de la logique numérique et la configuration du firmware dans le FPGA. De deux manières - en exécutant un script sous Linux et dans un shell graphique intégré. Également une brève description du contenu de la démo. Après ce galop à travers l'Europe, les élèves s'assoient devant la coque graphique et font des exercices simples, en commençant par les éléments logiques AND-OR-NOT, dont les entrées sont connectées aux boutons et les sorties aux LED. Quelque chose comme ça:

module top (input [2:0] key, output [7:0] led); wire a = ~ key [0]; // 0, , wire b = ~ key [1]; wire c = a & b; assign led [0] = ~ c; // , 0 endmodule

Ce faisant, deux questions intéressantes se sont posées immédiatement. Tout d'abord, j'ai moi-même d'abord oublié que les boutons et les LED sont inversés sur cette carte. Autrement dit, lorsque le bouton est enfoncé, puis 0 sur le fil, et lorsqu'il n'est pas enfoncé, puis 1. Et lorsque 0 est appliqué à la LED, il est allumé et lorsque 1 n'est pas allumé. Si vous ne connaissez pas l'inversion, l'élément logique AND (led [0] = key [0] & key [1]) commence à se comporter comme OR, et OR - comme I. Lois de Morgan en action! ~ (a & b) == ~ a | ~ b, ainsi que ~ (a | b) == ~ a & ~ b.

Mais même après la correction de certains écoliers, cette entreprise fonctionnait toujours dans l'autre sens. Ensuite, j'ai examiné leur code et j'ai découvert que lorsqu'ils réécrivaient le code que j'ai écrit au tableau, ils pensaient que «~» (tilde) est «-» (moins). Cela m'a donné une excellente raison de parler de la différence entre

le code

direct et le code

supplémentaire , et aussi pourquoi pour les nombres à un bit (- 0) == 0 et (- 1) == 1, tandis que (~ 0) == 1 et (~ 1) == 0. Et aussi, pour calculer sa négation pour des nombres multi-bits dans un code supplémentaire, il suffit de l'inverser au niveau du bit et d'en ajouter un: - a == ((~ a) + 1).

Suite - parties

2.3 ,

2.4 ,

2.5 .

Toute la leçon s'est déroulée sous Linux, plus précisément sous Lubuntu 18.04 avec Intel FPGA Quartus II installé dessus. Lubuntu était chargé de SSD sur lesquels Intel FPGA Quartus II Lite Edition 18.1 était également installé. Pour démarrer à partir du SSD, il vous suffit de le brancher sur le port USB 3.0, d'allumer l'ordinateur et d'appuyer sur F12. Entrez ensuite dans le menu et dites «charger depuis USB».

Bien que le logiciel de synthèse pour FPGA soit également disponible sous Windows, Linux est bon pour deux raisons:

1. Linux peut fonctionner sur des ordinateurs plus faibles que Windows. Par exemple, j'ai un ordinateur portable avec 2 gigaoctets de mémoire, donc Intel FPGA / Altera Quartus II pour Windows le fixe et fonctionne bien sous Linux.

2. Tous les développeurs adultes de puces en vrac chez Apple, NVidia et d'autres sociétés électroniques utilisent Linux, qui exécute les programmes Synopsys Design Compiler, Synopsys IC Compiler, Synopsys VCS, Cadence IES, etc.

Pourquoi est-il préférable de tout faire sur des SSD amorçables et de ne pas les mettre sur des ordinateurs en classe? Parce que l'installation de logiciels de sociétés FPGA est un processus assez ennuyeux, et autour d'Altera Quartus ou Xilinx Vivado, vous devez exécuter avec un tambourin, modifier des fichiers dans / etc et installer d'anciennes bibliothèques 32 bits pour certains composants, en particulier, pour la version gratuite de Mentor ModelSim. Certaines bibliothèques doivent être compilées à partir de codes sources. Il y a des

scripts de Stanislav Zhelnio qui font tout cela automatiquement, mais même avec ce script, tout installer sur un ordinateur prendra quelques heures.

Pourquoi ne pas tout faire sur des machines virtuelles? Par exemple avec VirtualBox? Nous avons essayé cela à l'Université d'État de Moscou et ailleurs, mais des problèmes avec la traction USB peuvent y survenir. Un SSD amorçable avec Lubuntu ressemble à la meilleure option.

Pour préparer l'ensemble SSD pour l'atelier, vous devez tout mettre sur un SSD, puis le cloner avec une telle commande qui vous permet d'écrire immédiatement sur trois SSD à partir d'un seul:

time sudo dcfldd if=/dev/sdb bs=1M of=/dev/sdc of=/dev/sdd of=/dev/sde

Ici, vous devez savoir que tous les boîtiers SSD ne prennent pas en charge Linux, par exemple, les disques Kingwin Data Star gâchent les disques. Les boîtiers corrects sont Orico et Eluteng.

De plus, je ne recommande pas d'essayer de remplacer les SSD par des lecteurs flash USB simples et téléchargeables. Bien qu'il fonctionne également sur les clés USB, certaines opérations sont incroyablement lentes, provoquant une gêne et une irritation. Mais sur les disques SSD chargés avec USB 3.0, tout vole plus vite que Linux sur un disque dur interne.

J'ai également essayé de coller un disque SSD amorçable dans l'Apple Mac en appuyant sur la touche Option au démarrage, mais cela n'a pas fonctionné. Ni via le port USB 3.1, ni via 3.0. Il semble que le Mac au démarrage ne veuille comprendre ni le système de fichiers Ext4, ni la table de partition. Y a-t-il des pilotes de pavot et des linuxoids parmi mes lecteurs? Il serait intéressant de savoir quoi faire (outre la possibilité d'utiliser VirtualBox ou d'autres machines virtuelles).

Fait intéressant, seuls 2 étudiants de l'ensemble du groupe ont utilisé Linux avant le séminaire. C'est très étrange pour moi, car à la place du ministère russe de l'Éducation, je transfèrerais toutes les écoles russes à Linux il y a 10 ans, quand Ubuntu est devenu convivial. En plus d'Ubuntu, on pourrait faire une version russe spéciale de Linux pour l'éducation. Windows est obstrué par des virus, vous devez payer des redevances pour cela, pourquoi Windows est-il meilleur que Linux pour les cours d'école de programmation Python, par exemple? Ou les documents Google ne suffiront-ils pas aux écoliers, mais Microsoft Word est nécessaire? Je ne comprends tout simplement pas.

Même le gouvernement sud-coréen a décidé en 2020 de passer à Linux .

En tout cas, lors de mon séminaire, les écoliers n'ont eu aucun problème avec Linux, même si, comme je l'ai dit, la plupart des écoliers l'ont utilisé pour la première fois.

Au début du troisième jour, j'étais en retard car j'ai été invité à donner une conférence à la branche russe de Samsung et l'événement a duré 3 heures (vous pouvez télécharger les diapositives de la conférence:

1 ,

2 ,

3 et

un article sur une partie du contenu ), après quoi j'ai eu faim et seulement pendant manger du sarrasin et de l'olivier à Mumu (ce qui me manque vraiment en Californie) a constaté que ma leçon au gymnase commencerait dans 5 minutes.

Ensuite, j'ai appelé Alexander Silantiev de MIET et demandé de commencer la leçon sans moi. La veille, les élèves ont commencé à faire de l'exercice avec un indicateur à sept segments affichant une lettre. Maintenant, si vous croisez la sortie d'une lettre avec un registre à décalage, vous pouvez implémenter la sortie sur un indicateur dynamique à sept segments multi-bits, et en même temps, les étudiants apprendront à coder la logique séquentielle sur le veril.

Le plan a été un succès - lorsque je suis entré en classe, certains écoliers exécutaient déjà des lettres lentement sur un indicateur dynamique, et pour qu'ils fusionnent en mots, tout ce qui était nécessaire était d'augmenter la fréquence de génération du signal d'activation (enable) pour le registre à décalage:

J'ai ensuite donné la parole à Stanislav Zhelnio

sparf d'IVA Technologies, et il a brièvement expliqué comment passer de simples blocs logiques à un processeur minuscule mais complètement réel (voir les

articles de Stanislav sur Habr et

schoolMIPS sur GitHub ):

Suite de la conférence de Stanislav ZhelnioLe séminaire a eu lieu au lycée de l'université russe des transports (MIIT). Au séminaire et avant celui-ci, Irina Grunicheva et Gleb Romanov (eNano) ont aidé; Alexey Pereverzev, Alexander Silantiev et Yevgeny Primakov de MIET, Alexander Romanov de HSE MIEM et ses étudiants, Alexei Kochnov de NIIIS, League of Robots (obraz.pro), Pavel Kirichenko (ICST, Intel, auteur de livres

bhv.ru/books/book. php? id = 201192 ), Yegor Kuzmin de l'

Institute of Applied Mathematics , Russian Academy of Sciences, Daria Krivoruchko, une écolière de SUNTs, était au LYuP, Timofey Cherkasov (Academy of Digital Technologies of St.Petersburg, School of Engineering Thinking LNMO), Alexander Bakerenkov et Julia ShaltaevP de la PreI University of Vladimir Vorontsov de MPEI, Evgeny Pevtsov de MIREA, Vitaliy Kravchenko de Nautekh, Arkady Poe Yakov et Sergey Pevchenko de MEI.

Ruslan Tikhonov d'Amperka a apporté des composants pour des exercices avec des microcircuits d'un faible degré d'intégration.

L'éditeur Dmitry Movchan, de DMK Press, a présenté à chaque participant des livres utiles - un manuel complet et épais de David Harris et Sarah Harris, Circuit numérique et architecture informatique, et une lecture facile par A. Hideharu, Entertaining electronics. Circuits numériques. Manga

Maxim Maslov, affilié à l'Institut de physique et de technologie de Moscou, est venu au séminaire et a fait don de cartes FPGA à des écoles d'été (ils disaient qu'en Russie, il y a peu de charité pour l'éducation).

Que se passera-t-il ensuite? Et puis il y aura deux événements qui élargiront et approfondiront ce que nous avons fait à la RTH Grammar School. Du 8 au 26 juillet, l'école d'été du MIET à Zelenograd. Voici une suggestion pour son programme. Ses deux premières semaines se composent de cinq parties:

- Les bases des circuits numériques sur microcircuits d'un faible degré d'intégration.

- Exercices simples avec logique combinatoire et séquentielle sur la carte FPGA.

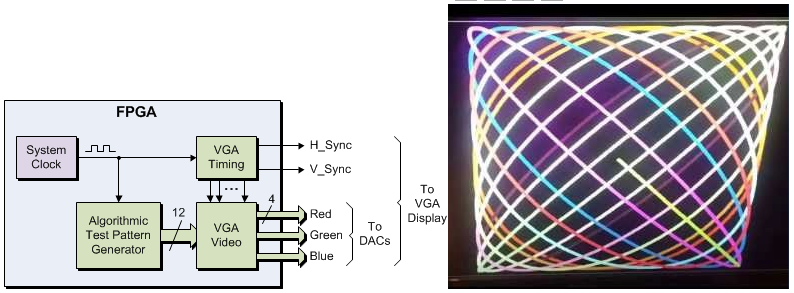

- Utilisation de FPGA pour contrôler l'affichage graphique.

- L'appareil et l'implémentation du microprocesseur le plus simple du FPGA.

- Projets individuels pour créer des jeux à la Angry Birds simplifiés, à la fois basés sur la machine d'état purement dans le matériel FPGA, et avec un contrôle de programme à partir du processeur le plus simple synthétisé dans le FPGA.

Mais avant l'école du 4 juin, il y aura un séminaire à Las Vegas, au cours duquel nous ne traiterons pas du processeur de l'école, mais du processeur industriel.

Programme plus détaillé à Zelenograd:

Semaine 1. Bases de la logique numérique.

Jour 1. Circuits intégrés à petite échelle, exercices de logique combinatoire

Jour 2. Microcircuits à faible degré d'intégration, exercices à logique séquentielle

Jour 3. FPGA, exercices avec boutons, interrupteurs, LED, indicateur à sept segments

Jour 4. FPGA, sortie de formes géométriques en VGA

Jour 5. FPGA, machine d'état pour Angry Birds

Semaine 2. Processeur

Jour 1. Programmation en langage assembleur.

Jour 2. Processeur scolaire MIPS en un cycle.

Jour 3. Interaction du processeur avec la conclusion des formes géométriques sur VGA.

Jour 4. Conférence sur les interruptions et le multitâche. Projet individuel - un jeu vidéo programmé sur le processeur avec sortie en VGA.

Jour 5. Conférence sur le convoyeur. Concours de projets individuels.

Semaine 1. Jour 1. Circuits intégrés à petite échelle.

1.1. Exercices avec logique combinatoire.

1.1.1. Élément logique XOR sur CD4070, sans boutons ni registres de rappel - répétez la démonstration.

1.1.2. Élément logique XOR, boutons d'ajout et registres de tirage - répétez la démonstration.

1.1.3. Tâche individuelle - par datashit pour construire une démonstration de l'un des éléments logiques AND / OR / NOT / XOR / NOR / NAND / XNOR, avec deux, trois, quatre ou huit entrées:

1.1.3.1. CD4081, Quad 2 entrées ET

1.1.3.2. CD4071, Quad 2 entrées OU

1.1.3.3. CD4011, Quad NAND à 2 entrées

1.1.3.4. CD4001, Quad 2 entrées NOR

1.1.3.5. CD4073, triple 3 entrées ET

1.1.3.6. CD4025, Triple 3 entrées NOR

1.1.3.7. CD4082, double 4 entrées ET

1.1.3.8. CD4072, double 4 entrées OU

1.1.3.9. CD4012, double NAND à 4 entrées

1.1.3.10. CD4002, 4 entrées NOR

1.1.3.11. CD4068, 8 entrées ET NAND

1.1.3.12. CD4078, 8 entrées NOR

1.2. Indicateur à 7 segments avec une cathode commune.

1.2.1. Assemblez sur une planche à pain avec des résistances, essayez des segments individuels.

1.2.2. Combinaison avec pilote d'indicateur à 7 segments, CD4511, décodeur de verrouillage BCD à 7 segments.

1.2.3. Option - indicateur avec une anode commune. À combiner avec l'onduleur CD4069, Inverter.

1.2.4. Option - ajoutez 4 boutons avec des résistances de pull-up à l'entrée CD4511.

1.3. Blocs logiques multinationaux - une tâche individuelle en fin de journée ou sous forme de devoirs:

1.3.1. CD4532, codeur prioritaire 8 bits

1.3.2. CD4051, commutateur analogique à 8 canaux, utilisé comme décodeur numérique

1.3.3. CD4051, commutateur analogique unique à 8 canaux, utilisé comme multiplexeur numérique

1.3.4. CD4052, commutateur analogique double à 4 canaux, utilisé comme multiplexeur numérique

1.3.5. CD4053, triple commutateur analogique à 2 canaux, utilisé comme multiplexeur numérique

1.3.6. CD4008, additionneur combiné 4 bits

1.3.7. CD4063, comparateur numérique 4 bits

1.3.8. CD4585, comparateur numérique 4 bits

À la fin de la journée, tout le monde montre qui a fait quoi.

Semaine 1. Jour 2. Exercices avec logique séquentielle.

1.2.1. Assemblez un générateur d'horloge basé sur une puce 555. Essayez différents condensateurs et résistances.

1.2.2. D-trigger sur la puce CD4013, double D-Flip-Flop avec Set-Reset.

1.2.3. Projet individuel:

1.2.3.1. Registre à décalage basé sur CD4015, registre à décalage statique double 4 bits, entrée série, sortie parallèle.

1.2.3.2. Registre à décalage basé sur CD4035, registre à décalage à 4 niveaux, entrée parallèle, sortie parallèle.

1.2.3.3. Registre à décalage basé sur CD4014, registre à décalage à 8 niveaux, entrée parallèle, sortie série.

1.2.3.4. Compteur avec sortie LED CD4029, décompteur décimal binaire décroissant.

1.2.3.5. Compteur avec sortie vers un indicateur à 7 segments via le pilote.

1.2.3.6. Plus complexe est une combinaison de registres à décalage CD4035 (entrée parallèle, sortie série) avec additionneur série CD4038. Il a besoin d'un onduleur CD4069. Avant cela, je vais démontrer l'additionneur série CD4032 sans onduleur.

1.2.3.7. Plus complexe est une combinaison de registres à décalage CD4014 (entrée parallèle, sortie série) avec additionneur série CD4038. Il a besoin d'un onduleur CD4069.

Semaine 1. Jour 3. FPGA, exercices avec boutons, interrupteurs, LED, indicateur à sept segments

1.3.1. Un élément logique de la logique combinatoire est l'entrée des boutons, la sortie des LED.

1.3.2. La sortie d'une lettre sur un indicateur à sept segments.

1.3.3. Le multiplexeur le plus simple est la sortie de la lettre en fonction de la touche enfoncée. Implémentation utilisant les constructions "?", "If", "case".

1.3.4. Registre à décalage.

1.3.5. Le mot est affiché sur un indicateur dynamique à sept segments à huit bits à l'aide d'un registre à décalage.

1.3.6. Projet individuel, peut-être devoirs pour le week-end:

1.3.6.1. Formes sur la matrice LED.

1.3.6.2. Serpent fonctionnant sur un indicateur à sept segments.

1.3.6.3. Génération de signaux de fréquence sonore, orgue sonore.

1.3.6.4. Entrée à partir d'un clavier à 16 boutons.

1.3.6.5. Verrouillage de code - reconnaissance d'une séquence de touches par une machine d'état.

1.3.6.6. Intégration avec un capteur télémétrique.

1.3.6.7. Intégration avec codeur angulaire.

Jour 4. FPGA, sortie de formes géométriques en VGA

Jour 5. FPGA, machine d'état pour Angry Birds

Semaine 2. Processeur

Jour 1. Programmation en langage assembleur.

Jour 2. Processeur scolaire MIPS en un cycle.

Jour 3. Interaction du processeur avec la conclusion des formes géométriques sur VGA.

Jour 4. Conférence sur les interruptions et le multitâche. Projet individuel - un jeu vidéo programmé sur le processeur avec sortie en VGA.

Jour 5. Conférence sur le convoyeur. Concours de projets individuels.

Semaine 3. Radio programmable. Le programme de blocs se compose de trois parties principales:

- Les bases de l'électrodynamique et de la propagation des ondes radio (partie théorique);

- Le principe de fonctionnement du trajet émetteur-récepteur (théorie et pratique);

- Les bases du traitement numérique du signal - filtrage, analyse spectrale (théorie et pratique).

Jour 1. Fondements théoriques de l'électrodynamique et de la propagation des ondes radio. Le schéma structurel du chemin de transmission, les fonctions des composants. Signaux (harmoniques, rectangulaires). Pratique du signal avec NI Elvis.

Jour 2. Transfert de signaux vers une haute fréquence. Justification mathématique du transfert de fréquence à l'aide de Matlab. Exercice pratique de transfert de fréquence avec NI Datex.

Jour 3. Amplification et émission de signaux. Entraînez-vous à utiliser NI Datex. Démonstration de la directivité des antennes.

Jour 4. Filtrage du signal. Entraînez-vous à utiliser NI Datex. Filtrage des signaux numériques dans Matlab

Jour 5. Transfert de signaux vers une basse fréquence. Entraînez-vous à utiliser NI Datex. Résumer le matériel couvert, résumer.

À propos du reste des jours de l'école, plus de détails seront dans un article séparé, après en avoir discuté au sein du comité d'organisation de l'école d'été. Si vous souhaitez participer à l'école d'été au MIET à Zelenograd en tant qu'étudiant ou instructeur, les

organisateurs viennent de poster les contacts et l'inscription . Si vous êtes étudiant, il est important que d'ici juillet, vous terminiez complètement les trois modules du cours en ligne Rosnanov (

«Du transistor au microcircuit» ,

«Le côté logique des circuits numériques» et

«Le côté physique des circuits numériques» ). La pratique sera difficile, et nous ne pourrons pas nous arrêter pour déterminer à quel cycle la valeur se trouve à l'entrée ou à la sortie du déclencheur D. Cela ne rentre pas immédiatement dans votre tête, mais si vous suivez un cours en ligne, ce sera plus facile pour vous.

Quelques détails

sur le séminaire à Las Vegas le 4 juin :

Il n’arrive pas souvent qu’un séminaire d’ingénierie, développé à l’origine pour la Russie et testé en Russie (y compris le MIPT), en Ukraine et au Kazakhstan, commence alors à Las Vegas, lors d’une conférence sur l’automatisation de la conception électronique. En Russie et en Ukraine, il a été appelé l'atelier MIPSfpga et lors de la conférence sur l'automatisation de la conception, il a été appelé la journée MIPS Open Developer. Venez le 4 juin à l'Embassy Suites by Hilton Convention Center au 3600 Paradise Road, Las Vegas, et vous participerez à un spectacle que les étudiants et les enseignants de l'Université d'État de Moscou, l'Institut de physique et de technologie de Moscou, l'Institut d'ingénierie physique de Moscou, Zelenograd MIET, Saint-Pétersbourg ITMO, Tomsk TSU, Kiev KPI, Almaty AlmaU et partiellement Nazarbayev University à Astana.

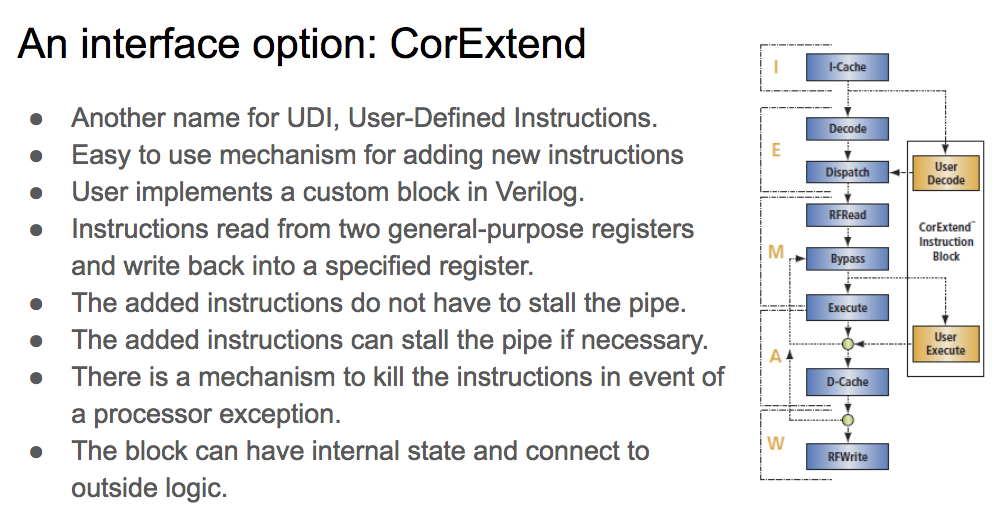

MIPSfpga est un package qui contient le cœur du processeur dans le code source Verilog, que vous pouvez modifier, ajouter de nouvelles instructions, observer le fonctionnement du cache et du pipeline, créer des systèmes multiprocesseurs, changer de logiciel et de matériel en même temps, etc. Dans la nouvelle version du séminaire, vous ajouterez un coprocesseur au processeur pour accélérer les algorithmes d'intelligence artificielle.

De plus, dans la nouvelle version du séminaire, nous montrerons comment configurer le noyau à partir du package MIPS microAptiv UP et l'insérer dans la liaison MIPSfpga. Une fois configuré, vous pouvez créer des options de processeur exotiques, par exemple un processeur avec 16 ensembles de 32 registres. Vous pouvez changer automatiquement ces ensembles lorsque vous entrez une interruption et ainsi changer rapidement le contexte sans enregistrer / restaurer le contexte de la mémoire, ce qui en RTOS ordinaire prend environ mille cycles.

MIPSfpga n'est pas destiné à être injecté dans un objet à partir du zéro absolu. Pour son utilisation fructueuse, il est nécessaire que l'étudiant connaisse déjà les bases des circuits numériques, soit capable de programmer en C et en assembleur, mais aussi de présenter les concepts de microarchitecture - convoyeur, conflits de pipelines, etc. C'est ce qui est étudié à schoolMIPS, que nous utilisons à Zelenograd.

Voici une diapositive sur le mécanisme d'ajout d'instructions au processeur MIPS microAptiv UP:

Lors d'un séminaire à Las Vegas le 4 juin, et probablement dans une école d'été pour jeunes ingénieurs électroniques, qui se tiendra du 8 au 26 juillet au MIET à Zelenograd, ma fille Elizabeth Panchul m'aidera (si elle reçoit un visa à temps). Étant donné qu'Elizabeth est semi-russe-semi-russe / ukrainienne, elle ne parle que l'anglais. Par conséquent, les instructeurs russes (étudiants ou étudiants diplômés de l'Institut de physique et de technologie de Moscou, Université d'État de Moscou, etc. qui sont prêts à nous aider avec Elizabeth et le MIET dans la conduite de l'école) peuvent apprendre l'accent correct de l'anglais d'elle et elle d'elle - les bases du russe. En plus d'étudier Verilog, MIPS, l'architecture, la microarchitecture et l'organisation du DMA en mémoire lorsqu'il est affiché sur un écran graphique:

Nous vous attendons à tous les séminaires, ainsi qu'en comités pour la création de leurs programmes!