Photo possible de IceLake à 10 nm. Source

Photo possible de IceLake à 10 nm. SourceDes choses étranges se produisent sur le marché des processeurs. Le leader mondial en la personne d'Intel a du mal pour la cinquième année à tenter de passer au processus de fabrication à 10 nm. Dans un premier temps, ils ont annoncé le passage au 10 nm en 2015, puis en 2016, 2017 ... Dans la cour de 2019, et à 10 nm d'Intel dans la série n'est toujours pas là. Eh bien, non, il existe des échantillons expérimentaux / techniques, mais un rendement élevé est un problème. Une véritable transition est déjà attendue au

plus tôt en 2022 .

En fait, c'était la raison de la pénurie de processeurs Intel sur le marché. Pour y remédier, l'entreprise étend la production de processeurs 14 nm modifiés (le même lac que de profil) et revient même à 22 nm. Il semblerait que la régression soit évidente. À l'heure actuelle, le coréen Samsung, le taïwanais TSMC et AMD, qui les ont joints à la plate-forme ZEN 2, font état de l'introduction de jusqu'à 7 nm et sont sur le point de passer à 5 nm. Ils ont sorti la «loi de Moore» du cabinet poussiéreux et l'ont déclarée plus vivante que tous les vivants. Bientôt, il y aura 3 nm, 2 nm, et même 1 nm (

sic! ) - pourquoi pas?!

Que s'est-il passé? Des

Asiatiques vraiment

rusés ont battu les

damnés pendos dans une industrie clé?

Puis-je ouvrir du champagne?Avis de non-responsabilité: j'ai trouvé

cet article par accident et j'ai été extrêmement étonné de voir avec compétence et en détail comment il révèle les problèmes de la microélectronique moderne, en particulier, la mort de la loi et du marketing de Moore. Il était une fois j'ai moi-même essayé d'écrire des articles sur

la fabrication de puces , et

dans la série d'articles "Inside Look", j'ai même regardé à l'intérieur, c'est-à-dire, Le sujet est extrêmement intéressant pour moi. Naturellement, j'aimerais que

l' auteur de l'article original le publie sur Habré, mais en ce qui concerne l'emploi, il m'a permis de le transférer ici. Malheureusement, les règles Habr ne permettent pas le copier-coller direct, j'ai donc ajouté des liens vers des sources, des images et un petit gag et j'ai essayé de redresser un peu le texte. Oui, et je connais et respecte les articles (

1 et

2 ) sur ce sujet de l'

amartologie .

Alors, réglons le problème ensemble. Nous essaierons autant que possible de nous plonger dans la physique et la technologie, et non dans les nuances (dont le nom est légion!). La description ci-dessous est simplifiée et parfois schématique. Écrivez des commentaires, nous allons essayer de discuter de manière constructive.

Préface

"Tout n'est pas si simple ...", disait la fille d'un officier. Si vous regardez la densité des transistors, c'est presque la même chose dans la technologie 14 nm d'Intel et la technologie 7 nm de TSMC (

ooops !!! ). Et même le retour d'Intel à 22 nm n'a pas eu un grand impact sur les performances. Que diable? Selon toutes les règles, le passage de la technologie de 14 nm à 7 nm devrait augmenter la densité des transistors jusqu'à 4 fois. Et c'est selon les préceptes de Gordon Moore, dont le

50e anniversaire de la loi a été célébré récemment, et sur le nez est le 55e anniversaire!

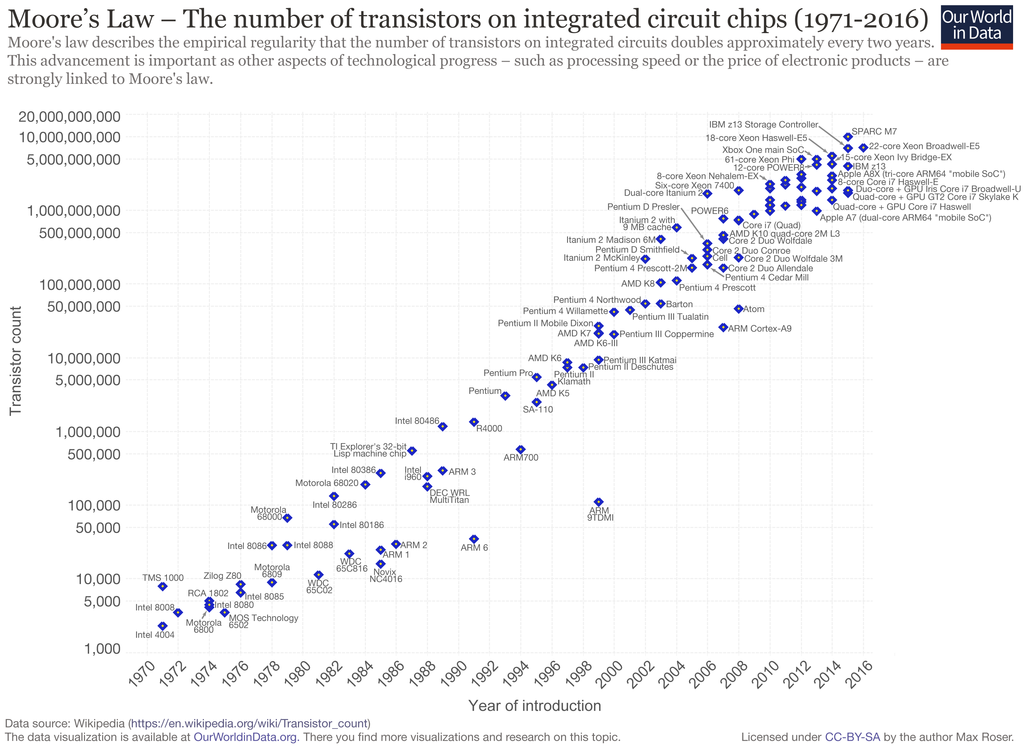

La loi de Moore coulée dans le fer. Comme vous pouvez le voir, nous «marquons» sur place depuis environ 5 ans.

La loi de Moore coulée dans le fer. Comme vous pouvez le voir, nous «marquons» sur place depuis environ 5 ans.Dans le même temps, des déclarations mitigées sont faites. Certains soutiennent que la «loi de Moore» est plus pertinente que jamais, et la microélectronique se développera comme avant. Des scientifiques, des concepteurs et des ingénieurs brillants surmonteront toutes les limitations, même les lois de la physique. Les gens ont besoin de nouvelles réalisations et cela ne prendra pas longtemps.

D'autres disent que tous les gars ont atteint les limites physiques, nous allons lécher ce qui est, mais c'est normal. Cela a longtemps été mis en garde. Ainsi, le chef de NVIDIA a

déclaré lors du CES 2019 que la loi de Moore est morte et que maintenant le vecteur (Huang ne devrait pas être un vecteur, mais un tenseur) doit être changé. Le spécialiste de la lithographie d'AMD et de GlobalFoundries

est d'

accord avec lui.

En fait, toutes ces normes technologiques d'unités et de dizaines de nanomètres ont longtemps été dissociées des dimensions physiques et sont devenues davantage des éléments de marketing. Au moins les 15 dernières années: après la transition de 130 nm à 90 nm. C'est alors que pour la première fois face à des limitations non pas technologiques, mais physiques de base. D'ailleurs, des experts en ont parlé, mais leur voix calme a été étouffée par les émissions de bravoure des spécialistes du marketing qui ont prétendu que rien ne s'était passé, que tout se passait à sa façon, selon les préceptes de

Leni ... Dr Moore.

Malheureusement, pour les spécialistes du marketing, et peut-être heureusement pour nous, la loi de Moore n'est pas une loi de la nature, mais une observation empirique formulée en 1965 par l'un des fondateurs d'Intel, Gordon Moore. Selon ses observations, une nouvelle série de microcircuits est sortie avec un intervalle d'un an, tandis que le nombre de transistors en eux a augmenté d'environ 2 fois. En 1975, la loi a été modifiée; selon elle, le doublement devrait avoir lieu tous les 24 mois. Depuis lors, pendant près de 40 ans, la loi de Moore a été élevée au rang d'icône et de bannière pour les fabricants de microélectronique numérique, qui sont parfois tordus (24 mois transformés en 36, maintenant stagnation - voir l'image ci-dessus).

En cours de route, diverses limitations technologiques sont apparues qui ont ralenti le processus (même transition à travers la limite de diffraction). Ou des percées qui ont donné une forte augmentation de la miniaturisation. Pour un observateur extérieur, tout ressemblait à une croissance stable dans le plein respect de la loi de Moore, et notamment des efforts des marketeurs.

Physique de "Sa Majesté le Silicium"

Je vais commencer par l'ode de silicium.

Le silicium n'est que le cadeau du paradis pour les fabricants de microélectronique. Non seulement, littéralement, sous le pied, le silicium est également un bon semi-conducteur avec des paramètres très appropriés (en termes de combinaison des caractéristiques électriques, énergétiques et physiques). Le silicium pur est presque un diélectrique; la conductivité est entièrement déterminée par la concentration d'impuretés. Il a une conductivité thermique élevée, est technologiquement avancé et résiste aux environnements agressifs.

Likbez pour les débutantsLe silicium à des températures ordinaires est un semi-conducteur à réseau cristallin cubique. 4 électrons externes d'atomes de silicium sont "socialisés", c'est-à-dire appartiennent à tous les atomes du réseau cristallin. Ils ne sont pas libres, mais pas attachés de manière rigide à leur atome. C'est une caractéristique des semi-conducteurs. Pendant un certain temps, ces électrons tournent autour de leur atome, puis sont transférés vers celui voisin, et les voisins viennent à leur place. Ainsi, les électrons externes (valence) se déplacent aléatoirement d'un atome à l'autre à travers le cristal (

remarque: pas tout à fait ainsi, les électrons eux-mêmes ne voyagent pas, ils ne transfèrent de l'énergie que par interaction les uns avec les autres ). Parfois, une sorte d'électron est complètement détaché de l'atome et commence (quasi) à se déplacer librement entre le réseau cristallin. À sa place reste un ion silicium positif avec une vacance d'électrons non remplie - un «trou». La prochaine fois que les électrons sont transmis d'un voisin, la vacance est remplie, mais elle apparaît chez le voisin, puis chez son voisin, etc. Le trou commence également à voyager au hasard à travers le cristal.

Si nous appliquons maintenant un champ électrique, alors un électron libre volera de moins en plus. Les électrons de Valence sont également soumis à l'action du champ et commencent à remplir rapidement les espaces vides vers le côté positif, et les espaces vides des trous s'écouleront vers le côté moins. Ce comportement ressemble à un trou est un porteur de charge gratuit, un tel électron libre, uniquement avec une charge positive. Le comportement du trou est décrit par les mêmes formules que l'électron, corrigé pour

une «

masse effective » plus importante. Par conséquent, ils ne sont souvent pas à la vapeur et, pour simplifier, considèrent les trous comme des particules élémentaires ordinaires avec une charge positive.

À température ambiante, une paire électron-trou par billion d'atomes de silicium (concentration 10

-12 ), le silicium pur à température ambiante est un isolant (conditionnellement: les électrons et les trous s'annihilent trop rapidement, sans avoir le temps d'atteindre la fin du cristal).

Si maintenant un atome avec 5 électrons externes, par exemple du phosphore, est introduit dans le réseau de silicium, alors il est inclus dans l'échange à 4 électrons et le cinquième électron devient libre. Nous obtenons des ions positifs de phosphore et un «gaz d'électrons» intégré dans le silicium à partir d'électrons libres. La conductivité du silicium avec une telle impureté augmente linéairement; les concentrations d'un atome de phosphore par million d'atomes de silicium (

ppm ) modifient déjà considérablement les propriétés électriques. Un mélange de phosphore est appelé donneur, et le semi-conducteur lui-même est appelé

conductivité de type N. En plus du phosphore, il peut s'agir d'arsenic ou d'antimoine.

Maintenant, nous ajoutons aux atomes de silicium pur avec 3 électrons externes, par exemple, le bore. Il est également inclus dans l'échange à 4 électrons, mais ne peut donner que 3 électrons. Aux atomes de silicium voisins, un "trou" apparaît et part pour un voyage à travers le cristal. Nous obtenons des ions de bore négatifs et un gaz de trou chargé positivement. Une telle impureté est appelée accepteur et le semi-conducteur est

de type P. En plus du bore, les accepteurs sont l'aluminium, le gallium et l'indium.

Soit dit en passant, le silicium extrêmement pur (de sorte qu'il est un isolant) est incroyablement difficile à obtenir. La présence de bore fait

toujours du silicium un semi-conducteur de type p.

Un bonus au silicium est son oxyde - dioxyde de silicium SiO

2 . C'est un diélectrique presque parfait, avec une résistance et une dureté élevées, résistant à tous les acides à l'exception du fluorhydrique (HF). Dans le même temps, l'acide fluorhydrique ne dissout pas le silicium lui-même, vous ne pouvez pas avoir peur de décaper l'excès. Un mince film d'oxyde se forme à la surface du silicium même à température ambiante (naturellement, dans l'air). Pour obtenir des films d'oxyde épais, le silicium est chauffé ou un dépôt à basse température à partir d'un gaz contenant du silicium est utilisé. La précipitation est utilisée lorsque des couches sont déjà déposées dans le cristal, et le chauffage entraînera un «maculage» de la topologie.

Lassitude d'un chimiste, une fois par an du système périodique: un pas à droite - P, phosphore, oxyde forme acide phosphorique, à gauche - Al, aluminium, métal, haut - C, carbone, oxyde - gaz, bas - Ge avec une faible prévalence dans la croûte terrestre (kilo coûte maintenant ~ 1k $).

Malgré des discussions constantes sur la fin imminente de l'ère du silicium et la transition vers d'autres semi-conducteurs, par exemple, les structures A

3 B

5 (aréséniure de gallium, phosphure de gallium ou nitrure de gallium), carbure de silicium, diamant,

graphène et autres, car ils ont une mobilité électronique plus élevée et des trous, une dépendance à la température plus faible, une conductivité thermique plus élevée, le silicium règne en microélectronique de masse.

Oui, pour A

3 B

5, il est possible de créer des

hétérojonctions . C'est alors que les zones à l'intérieur du transistor diffèrent non seulement par le type de conductivité, mais également par la structure physique, ce qui donne des opportunités supplémentaires. Toutes choses étant égales par ailleurs, les microcircuits de nitrure de gallium peuvent fonctionner à une fréquence plus élevée, sont résistants aux températures élevées et offrent une meilleure dissipation thermique. Mais alors que ces matériaux ne sont utilisés que pour des éléments discrets et de petits microcircuits. Pour les grands microcircuits, la complexité de la technologie rend ses ordres de grandeur plus élevés que le silicium. Oui, et "autre égal" n'est pas obtenu. Par conséquent, les microcircuits alternatifs sans silicium ont une spécialisation étroite.

MOSFET

Considérez la brique principale des microcircuits numériques - un transistor à champ plan (plat) avec un canal induit. Il est

MOS (métal-oxyde-semi-conducteur), il est MIS (métal-diélectrique-semi-conducteur), il est MOS (métal-oxyde-semi-conducteur), il est

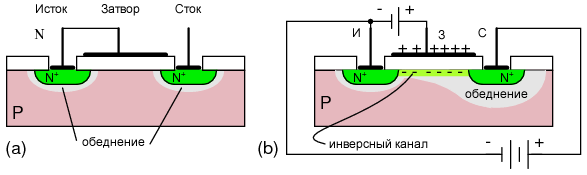

MOSFET .

Vue schématique en coupe d'un transistor à canal n

Vue schématique en coupe d'un transistor à canal nDescription des principes de travailNous avons un substrat de silicium de conductivité de type p. Il a créé 2 couches de type n - source et drain. Analogues de l'émetteur et du collecteur dans les

transistors bipolaires . Entre eux, une électrode séparée du silicium par une couche diélectrique (généralement de l'oxyde de silicium) est une grille. La zone sous le volet est appelée la base. Si nous appliquons une tension entre la source et le drain, il n'y aura pas de courant, car il y aura une

jonction pn polarisée en inverse entre eux - le transistor est fermé. Schématiquement, il s'agit d'un analogue d'une diode de verrouillage. Lorsqu'il est correctement connecté, il s'agit d'une transition entre la base et le drain.

Appliquez maintenant une tension positive à la grille. Un champ électrique traverse l'oxyde, pénètre dans le silicium, repousse les trous (+) de la couche superficielle du trou et attire les électrons libres (-). Ces derniers dans le substrat de type p, bien que peu nombreux, sont présents. À une certaine tension à la grille, dans la couche d'électrons de surface, il devient plus que des trous. L'inversion se produit et un canal de type n apparaît sous la couche d'oxyde. Un courant le traversera de la source au drain - le transistor est ouvert. Un transistor ouvert est une unité logique, un fermé est un 0 logique. Eh bien, ou vice versa, selon la mise en œuvre.

Pour les transistors à canal p, les régions n et p sont interchangées et le transistor s'ouvre à une tension de grille négative.

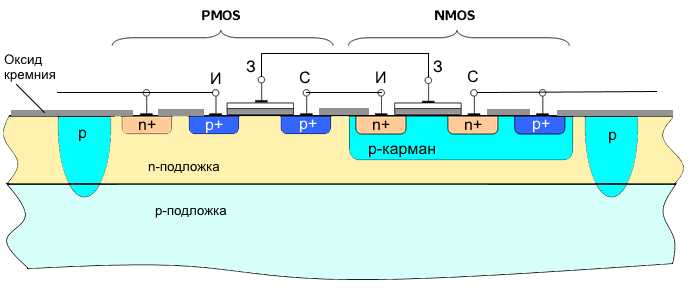

Les avantages des transistors MOS sont leur compacité. Mais il y a aussi un sérieux inconvénient - une consommation d'énergie élevée, car à l'état ouvert, un courant traversant traverse le transistor. Ainsi, depuis les années 1970, les

transistors CMOS (

MOS complémentaires ) dominent la technologie numérique. Ce sont des transistors à canal p et à canal n connectés en série, avec des grilles combinées. Habituellement fait dans une cellule.

Si nous alimentons les portes plus - le transistor à canal n est ouvert, le canal p est fermé. Il n'y a pas de courant traversant, moins à la sortie. Si nous alimentons la porte avec un moins - le transistor à canal n est fermé, le canal p est ouvert. Il n'y a plus de courant traversant, plus une sortie. C'est-à-dire L'élément fonctionne également comme un onduleur.

Il s'agit de la technologie la plus économe en énergie. Dans un état statique, l'élément ne consomme rien (à l'exception du courant de fuite parasite), seul le courant de commutation est consommé. La consommation électrique est presque directement proportionnelle à la fréquence de la puce (le nombre de cycles de recharge). La faible consommation d'énergie et la compacité ont déterminé la domination de la technologie CMOS dans l'électronique numérique.

Les circuits à transistors bipolaires fournissaient initialement des performances supérieures, mais étaient plus complexes, occupaient plus d'espace et consommaient un ordre de grandeur plus d'énergie. Je dois dire que le choix en faveur de CMOS a porté ses fruits. Il serait presque impossible d'obtenir des caractéristiques telles que les processeurs d'aujourd'hui sur d'autres technologies. Et tandis que les alternatives ne sont pas visibles à l'horizon.

Caractéristiques de la topologie

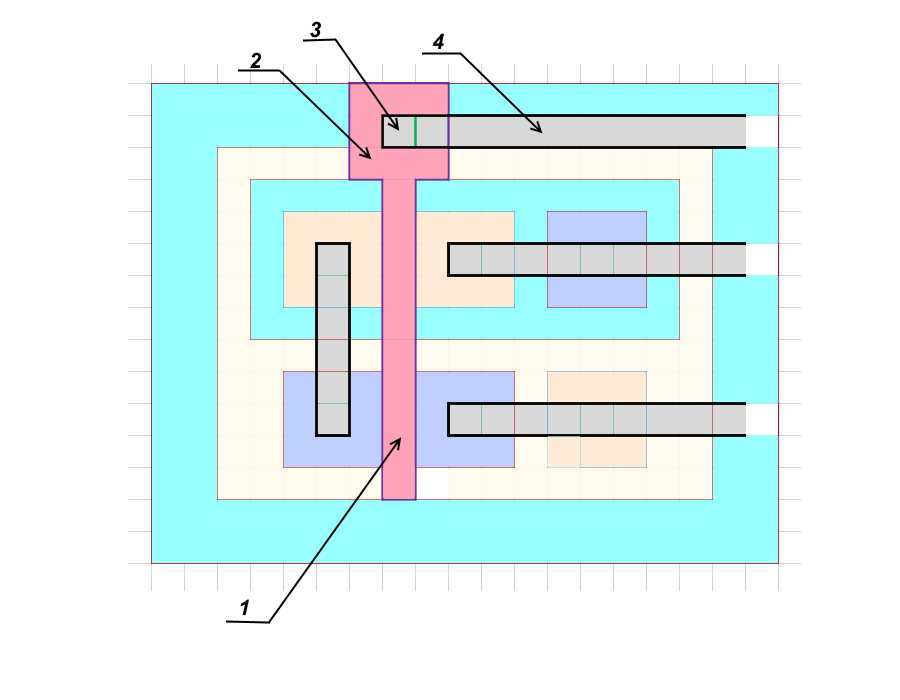

La topologie de la puce de la puce peut être représentée de manière conventionnelle comme une grande feuille de papier dans une cellule, où les limites des régions sont dessinées le long des lignes, et la taille technologique est la taille de la cellule. En fait, pour les éléments non critiques, vous pouvez également mettre en retrait une demi-cellule (la règle des deux lambdas), mais ce sont des nuances.

Conception détaillée de la topologieRevenons mentalement à la fin des années 80, lorsque les technologies étaient encore simples et compréhensibles. Prenons une vraie paire de transistors CMOS. Les fenêtres n + et p + sont fortement dopées (1 atome d'impureté pour plusieurs centaines voire plusieurs dizaines d'atomes de silicium), soit le niveau d'impuretés est de plusieurs ordres de grandeur supérieur à seulement n et p.

Supposons que l'on nous ait donné des savoirs traditionnels pour dessiner la topologie d'une telle paire de transistors dans une poche isolée. Puisqu'il n'y aura pas de grands courants à travers les transistors, nous calculerons sur la base de la plus petite taille technologique possible, le soi-disant jeu technique. Appelez cela d.

Le profil

Le profil Vue de dessus

Vue de dessusCommençons par la fenêtre de contact pour la source du transistor à canal n

(1) . Nous en faisons le plus petit

d * d possible.

La source

(2) aura alors la taille

3d * 3d (vous devez prendre du recul au moins depuis les bords de la fenêtre).

La base

(3) est faite de la largeur minimale

d .

De plus, le stock

(4) avec sa fenêtre de contact, également

3d * 3d .

Le dernier élément est la zone fortement alliée

(5) pour le contact avec la base p, ainsi que

3d * 3d . Il est nécessaire d'égaliser la tension de la source et de la base, afin que l'apparition spontanée du canal ne se produise pas.

Dessinez les bords de la poche P elle-même

(6) , un autre

d des fenêtres dessinées. La taille de la fenêtre p est de

5d * 13d .

Ci-dessous, nous dessinons un transistor à canal p. Nous faisons cet arrangement pour rapprocher l'élément entier à une forme carrée - il est plus facile à assembler.

Nous changeons l'emplacement de la source et du drain. Cette disposition minimise la longueur des pistes métalliques de contact. Commençons par la fenêtre de contact pour le drain

(7) , la taille est minimale -

d * d .

Le drain

(8) sera

3d * 3d , la base

(9) est de largeur

d et en ligne avec la base du transistor à canal n. La source

(10) et la zone de contact fortement alliée à la base

(11) seront également

3d * 3d .

La dernière taille est le retrait minimum du chemin de division

(12) , un autre

d .

Total a reçu la taille de la paire de transistors

11d * 15d . La piste séparée dans notre cas est une autre région de type p, qui avec un substrat n forme une jonction pn polarisée en inverse.

Il existe une autre option pour l'isolation avec un diélectrique - dioxyde de silicium SiO

2 ou saphir Al

2 O

3 . Cette dernière option est préférable, mais sensiblement plus chère. Dans ce cas, les zones peuvent être formées à proximité du chemin de division et le courant de fuite entre les cellules sera nul. En règle générale, la largeur de la piste de séparation est légèrement supérieure à l'épaisseur de la couche épitaxiale (voir ci-dessous) et est égale à

2d .

La taille totale effective des cellules au milieu des chemins de division est de

13d * 17d .

Ensuite, au-dessus de l'oxyde, dessinez un obturateur

(1) , retirez la zone de contact

(2) de l' obturateur plus près du chemin de division et formez une fenêtre de contact

(3) .

L'étape finale est la métallisation et les chemins de contact

(4) . L'aluminium était à l'origine utilisé comme matériau de la grille et des chemins de contact (bien que l'aluminium soit toujours utilisé

dans certains appareils ), plus tard, la grille était en silicium polycristallin hautement allié et les chemins de contact en cuivre.

Supposons que nous vivons dans une technologie de processus de

3 microns . Ensuite, nos deux cellules à transistors

11d * 15d , comme indiqué ci-dessus, auront une taille de

33 * 45 microns . Mais alors nous avons eu des ennuis, passés à une nouvelle technologie de procédé de

1,5 microns . La taille de notre cellule est devenue

16,5 * 22,5 microns . , , . , ( ). , . . .

, . .

( )? .

(

). , (

.: , () , , , , .

CorneliusAgrippa :

, , (, ). , ). (boule) 200 300 , (

aka wafers ) 0,5-0,7 . . 450 , . ( , ).

, — . : , (SiCl

4 ). . , . p- n-. n- p-. .

, , p-, . , , , .

.

, 700 .

, , . . , , . , . , .

. , , . , . , , . .

, . , , . . , . , , .

, , ,

.

tnenergy .

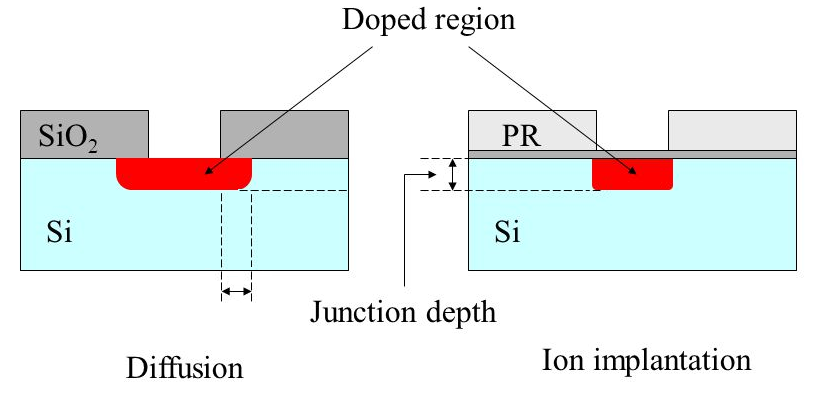

– . . ().

:

- .

- – . , .

- . – . , , p- . ( .: -) .

- . . , ( ) ( ). .

- – .

- . . , , ( shadowing effect).

- .

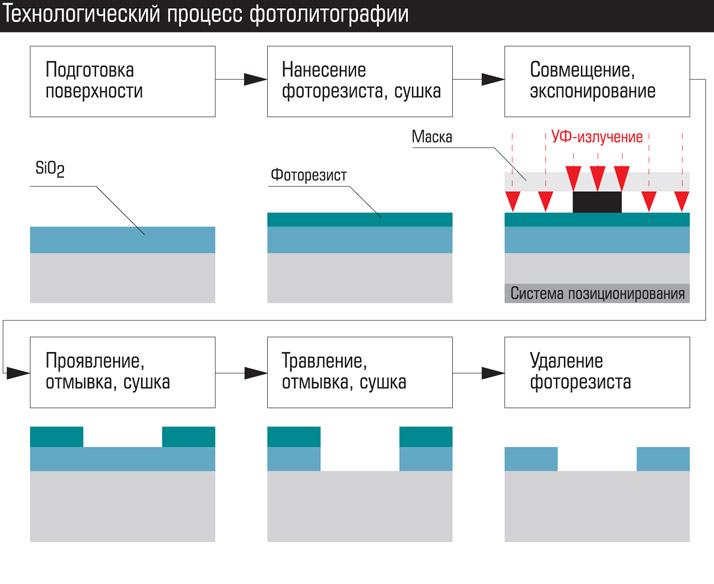

À la fin de l'opération, nous obtenons une plaque avec les sections d'oxyde enlevées, qui peuvent être envoyées pour diffusion, implantation ionique ou dépôt de métal (

note: ou électrodéposition). Après avoir créé la couche, l'oxyde est généralement gravé dans toute la zone de la plaque et une nouvelle est déposée.

Les fenêtres créent de large à étroit. Dans notre cas, la séquence sera la suivante: zones de séparation, poches P, couches p +, couches n +, fenêtres de contact avec métallisation, application de l'obturateur, zones de contact de l'obturateur, première couche de pistes métalliques avec zones de contact sous la deuxième couche, deuxième couche de métallisation, etc. . Dans les processeurs modernes, la métallisation peut atteindre 10 à 15 couches.

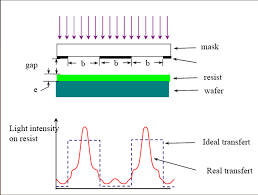

La photolithographie de contact a été utilisée à l'aube de la microélectronique. Maintenant, l'essentiel est la photolithographie par projection. C'est à ce moment qu'une lentille et des systèmes de miroirs sont placés entre la source de rayonnement et le photomasque pour créer un faisceau de photons rétréci. Des méthodes schématiques de photolithographie sont illustrées dans la figure ci-dessous: photolithographie de contact, avec un espace, projection à travers des lentilles, miroir de projection.

Les avantages de la photolithographie sont la vitesse élevée et le faible coût. L'ensemble de la zone de la plaque avec tous ses microcircuits est exposé à la fois et le processus prend plusieurs minutes. Ou un carré de plusieurs microcircuits suivi d'un décalage de plaque.

En plus de la photolithographie, il existe d'autres types - électronique, radiographique et ionique. Le plus intéressant est la lithographie électronique (par exemple, le projet Mapper, sur lequel

BarsMonster a écrit ).

Avec la lithographie électronique, l'exposition de la réserve n'est pas effectuée par la lumière, mais par un faisceau d'électrons. Dans sa forme la plus simple, il ressemble à la formation d'images sur des tubes

cathodiques CRT . De tous les types de lithographie, c'est la lithographie électronique qui fournit l'image la plus claire et la plus haute résolution. L'inconvénient est le long temps d'exposition. Dans les technologies modernes, le faisceau d'électrons a une épaisseur de quelques nanomètres et même des fractions de nanomètre, et le diamètre de la plaque est de 300 mm. Naturellement, pas un seul paquet n'est utilisé, mais des dizaines de milliers contrôlés par un ordinateur. Mais un flux d'électrons total très puissant est nécessaire. A titre de comparaison, l'énergie du rayonnement UV quantique est de plusieurs

eV , l'énergie électronique dans le faisceau est de plusieurs milliers d'électrons volts.

De plus, les électrons sont électriquement chargés et se repoussent, ce qui entraîne une divergence de faisceau. Bien sûr, il est possible d'augmenter la vitesse des électrons, mais ils perceront ensuite la réserve ou se refléteront à une vitesse élevée dans des directions arbitraires, provoquant un rayonnement secondaire (

électrons secondaires ) et, par conséquent, une exposition. Tout cela limite l'utilisation de la technologie.

La lithographie électronique est utilisée pour créer des photomasques. Le temps d'exposition pour un masque photo est de plusieurs jours. Par conséquent, la photolithographie domine dans la production de microcircuits.

Un ensemble moderne de masques photo pour un processeur coûte des dizaines de millions de dollars. Sans surprise, étant donné que les processeurs modernes contiennent des milliards de transistors et qu'il y a des centaines de processeurs sur la plaque. De plus, les fenêtres du masque photographique moderne ne sont pas seulement des trous dans le matériau, mais souvent d'autres matériaux ayant des propriétés optiques spécifiques. Un véritable ensemble de masques photo se compose de dizaines de masques. Aux derniers procédés de fabrication, plus de 50 (

sic! ).

Mais ils vous permettent d'estampiller des micropuces comme des petits pains. Au cours de sa durée de vie, un ensemble de modèles de photos vous permet d'obtenir des centaines de milliers voire des millions de micropuces en sortie.

Qu'est-ce qui limite donc la taille de la technologie de processus?

4 groupes de facteurs peuvent être distingués conditionnellement:

- Matériel et technologie. Associé à la résolution matérielle.

- Physique des processus technologiques. Elle est déterminée par les limites physiques d'un processus particulier, qui peuvent être contournées par un changement de technologie ou de matériaux.

- Physique. Ce sont des limitations qui ne peuvent être contournées, mais leur impact peut être minimisé.

- Physique extrême.

Limitations matérielles et technologiques

Ce type de limitation a été décisif dans les premiers stades de la microélectronique. Se réfère principalement à la production de "salles blanches", d'équipements sophistiqués pour les processus techniques, d'instrumentation (ce qui est important pour le contrôle qualité des produits). Par exemple, la photolithographie nécessite une optique ultra-précise, des microscopes puissants, des mécanismes de combinaison de masques et de plaques avec une précision de fractions de nanomètres, une atmosphère ultra pure ou un vide lors de l'exposition, etc. Il est nécessaire de résister très précisément aux paramètres des processus technologiques - température, durée, composition de l'atmosphère, puissance de rayonnement, préparation de la surface.

Maintenant, la précision de l'équipement n'est pas un facteur limitant. Pas parce que c'est un problème simple. Il suffit de regarder un schéma d'une projection moderne ou d'une photolithographie miroir pour comprendre le niveau de complexité. Mais c'est vraiment le cas lorsqu'il n'y a pas d'obstacles pour les designers et ingénieurs talentueux.

Les problèmes de technologie sont généralement pertinents dans la première série. Avec un changement dans la norme du processus technique, non seulement les dimensions horizontales, mais aussi verticales, et la concentration d'impuretés, et les proportions des zones actives changent. Et maintenant, à chaque nouvelle étape, la physique des processus évolue également. Naturellement, tous les paramètres sont préalablement calculés et modélisés, mais la réalité fait toujours des ajustements. Par conséquent, pour la première série, un rendement de 3% de circuits appropriés (97% défectueux) est considéré comme la norme. Progressivement, les processus technologiques sont optimisés et le pourcentage de rendement adapté à la dernière série dépasse les 90%.

Physique des processus technologiques

Pendant plus de 30 ans, jusqu'à récemment, ce sont ces facteurs qui ont été limitatifs. J'ai déjà énuméré certaines de ces limitations - l'entrée d'impuretés sous l'oxyde pendant la diffusion, le rongement de l'oxyde sous la résine photosensible pendant la gravure et l'érosion des couches déjà déposées pendant les processus thermiques.

Les méthodes de solution sont également partiellement décrites.

La diffusion a été remplacée par une implantation ionique. De plus, pour les plus petites couches, le matériau d'impureté a été changé - au lieu du phosphore, de l'arsenic est utilisé, au lieu du gallium bore. Leurs atomes sont plus gros et plus lourds, donc ils se dissolvent moins bien dans le silicium aux mêmes températures (et surtout, il leur est plus difficile de diffuser!). Pour l'implantation ionique, ce n'est pas important, mais lors d'un chauffage ultérieur, ces couches s'érodent beaucoup plus faiblement.

La production d'oxyde par chauffage a remplacé le dépôt catalytique à basse température du gaz. Le chauffage est utilisé, mais seulement au tout début, tandis que le cristal est propre. Dans certaines opérations, du nitrure de silicium (Si

3 N

4 ) ou des couches successives d'oxyde et de nitrure sont utilisés à la place de l'oxyde.

La gravure à l'acide liquide a été remplacée par la gravure ionique. L'acide est utilisé uniquement pour éliminer l'oxyde de toute la zone.

Un autre problème était la production d'oxyde ultra pur pour un diélectrique de grille. Cet oxyde reste un élément de travail sur la puce et a des exigences élevées de pureté et d'uniformité. L'épaisseur d'oxyde par endroits est inférieure à 10 couches atomiques. Un petit défaut entraîne une crevaison ou une panne. Cela donne une fermeture électrique de l'obturateur à la base et la défaillance de l'élément. Pendant un certain temps, une alternance d'une couche d'oxyde et de nitrure de silicium a été utilisée. Dans la technologie à 90 nm, l'oxyde d'hafnium HfO

2 a été utilisé comme diélectrique de grille.

Soit dit en passant, pendant l'URSS, ce sont précisément les problèmes d'obtention d'oxyde de haute qualité qui ont ralenti la transition vers le CMOS. D'où la recherche de voies alternatives et le décalage général en microélectronique numérique.

L'opération la plus critique est la photolithographie. Tant et si bien que jusqu'à présent, beaucoup ont mis un signe égal entre la résolution de l'ensemble du processus technique et la résolution de la photolithographie. Et le principal problème de la photolithographie depuis la fin des années 1980 est la diffraction de la lumière. Plus précisément, le rayonnement ultraviolet, bien que le principe soit le même. Il ne serait pas exagéré de dire que pendant 30 ans, la lutte pour réduire la taille des processus technologiques a été avant tout une lutte contre la diffraction.

La diffraction de la lumière a été découverte au XVIIIe siècle par les pères des fondateurs de l'optique:

En pénétrant dans le trou, les rayons de lumière et tout autre rayonnement électromagnétique (EMP) s'écartent de la trajectoire rectiligne, divergent et pénètrent dans la zone d'ombre. Le phénomène est observé à des tailles de trous proches de la longueur d'onde. Plus le trou est petit par rapport à l'onde, plus la dispersion est forte. La règle est valable jusqu'à des écarts d'un quart de longueur d'onde. Le trou fait moins d'un quart de la longueur d'onde, le faisceau EMP «ne voit tout simplement pas» et est réfléchi à partir de la surface avec des espaces aussi petits que solides.

La longueur d'onde des LED en silicium est d'environ 1 μm (proche infrarouge), la longueur d'onde de la lumière visible de 780 nm (rouge) à 380 nm (violet). Moins de 380 nm, le rayonnement ultraviolet (UV) commence. Les émetteurs utilisés aujourd'hui en photolithographie ont une longueur d'onde de 248 nm et 193 nm, c'est le rayonnement des lasers excimères (par exemple

sur XeF 2 ). En conséquence, les problèmes de diffraction ont atteint leur pleine hauteur après avoir surmonté la barre technologique de 3 microns, et après 800 nm, ils sont devenus dominants. En raison de la diffraction pendant l'exposition, l'UVI pénètre dans la zone sous un masque opaque et illumine la résine photosensible dans l'ombre. En conséquence, au lieu d'un carré clair, nous obtenons une crêpe floue.

En plus de l'érosion des fenêtres, il y a l'effet de chevauchement (interférence) des ondes latérales pour les fenêtres rapprochées. Les pics de lumière parasite apparaissent bien en dessous de la partie réfléchissante du photomasque.

Optique - vous sans cœur ...Quelles méthodes sont utilisées pour lutter contre ce phénomène?

Optique - vous sans cœur ...Quelles méthodes sont utilisées pour lutter contre ce phénomène?La première étape a été d'utiliser la photolithographie par projection. Si elle est grandement simplifiée, une lentille est installée entre le masque photoélectrique et la plaque, qui recueille les rayons divergents et les concentre sur la résine photosensible.

Une autre méthode consistait à réduire la longueur d'onde du rayonnement d'exposition. À un moment donné, ils ont commencé avec des lampes à arc au mercure avec une longueur d'onde de rayonnement de 436 nm - c'est la lumière bleue. Puis 405 nm (violet), 365 nm (proche ultraviolet). Sur ce, l'ère des lampes au mercure terminée, l'utilisation des lasers à excimère a commencé. D'abord, 248 nm (ultraviolet moyen), puis 193 nm (ultraviolet profond). Sur ce processus et au point mort.

Le fait est qu'ils ont atteint les limites de transmission de l'optique à quartz. Les ondes plus courtes absorbent le quartz. Il fallait soit passer à des systèmes de miroirs, soit utiliser des lentilles en d'autres matériaux. Des installations expérimentales à 157 nm ont été réalisées sur la base de l'optique au fluorure de calcium. Cependant, ils ne sont jamais entrés dans la série. Puisqu'il y avait des moyens d'optimiser la lithographie à 193 nm.

Infographie visuelle sur les lasers.

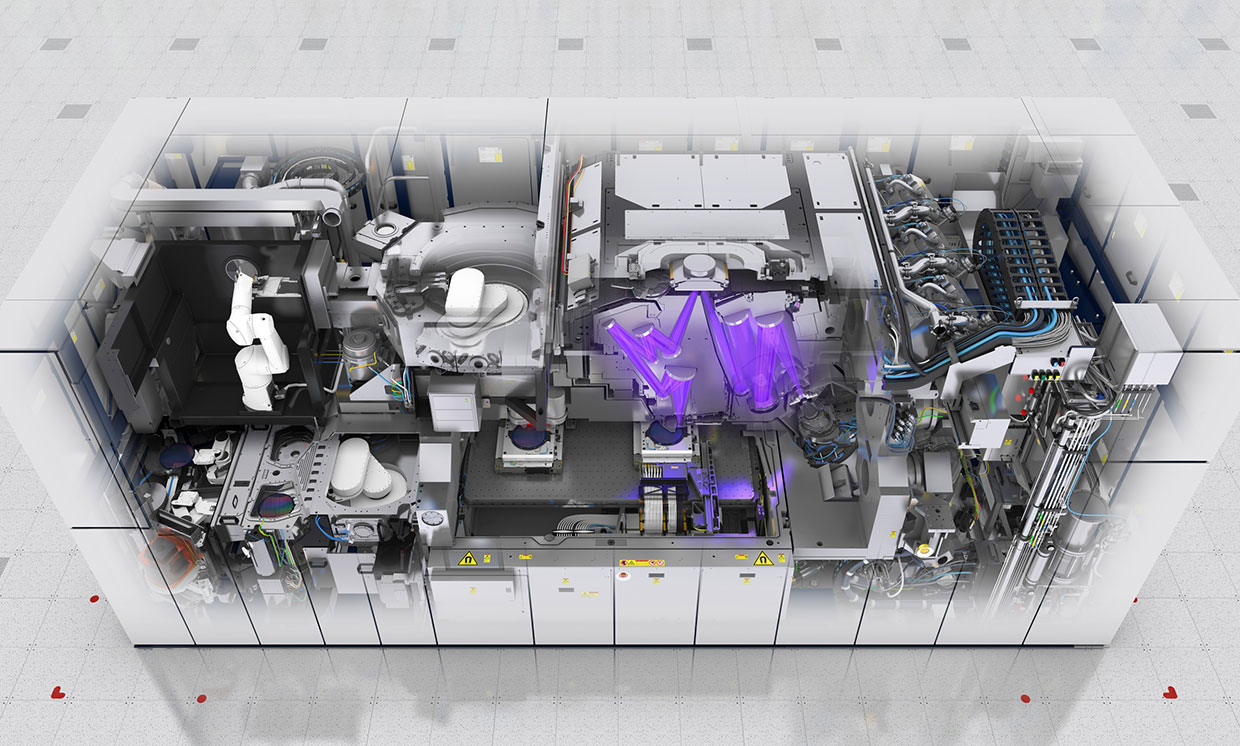

SourceLithographie EUV

Au milieu des années 1990, ils ont développé une photolithographie standard sur ultraviolet extrême (

lithographie EUV ) avec une longueur d'onde de 13,5 nm. Cette longueur d'onde a permis de donner une résolution en unités de nm.

Au début des années 2000, les premiers échantillons expérimentaux sont apparus.

À la fin des années 2000, la technologie devait entrer dans une série. Et enfin, la nouvelle est venue qu'en 2019, Samsung et TSMC taïwanais passeront à la lithographie EUV. Moins de 15 ans se sont écoulés (

sic! ). Intel est devenu le principal antagoniste de la lithographie EUV, bien qu'il soit à l'origine l'un des initiateurs. Reconnaissant que tout ce qui était possible a été évincé des UVI à 193 nm, ils ont annoncé le passage à 126 nm (ha ha!).

Quelle est la raison de ce rejet?Le fait est que 13,5 nm sont déjà pratiquement des rayons X. La limite entre UVI et rayons X est classiquement considérée comme 10 nm, mais les ultraviolets ne sont pas différents des rayons X doux dans le comportement de 13,5 nm. Par conséquent, la lithographie EUV ressemble plus à des rayons X. Les lentilles pour une telle longueur d'onde

n'existent pas dans la nature, il est donc nécessaire de passer aux miroirs de couches métalliques hétérogènes.

En plus de produire une structure très mince et complexe, les miroirs métalliques absorbent la majeure partie du rayonnement. Des unités de pourcentage de la puissance de rayonnement initiale atteignent la résine photosensible. Si nous prenons en compte que l'efficacité de l'émetteur lui-même est également de quelques pour cent, alors pour obtenir un temps d'exposition normal, une puissance élevée et une consommation d'énergie élevée sont

nécessaires (

ooops! ).

Ceci est le scanner ASML EUV

Ceci est le scanner ASML EUVLa source de rayonnement est le plasma. Une substance très capricieuse, à partir de laquelle il est difficile d'obtenir un flux uniforme sans pulsations. Même l'air absorbe activement 13,5 nm, donc l'exposition ne peut être effectuée que sous vide.

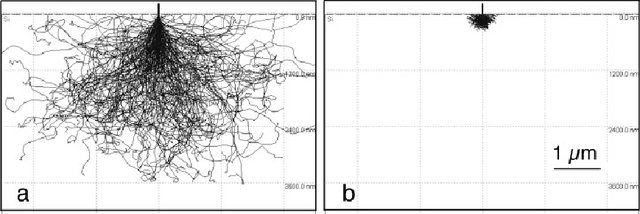

Le problème avec la sélection de la résine photosensible. Plus la longueur d'onde est courte, plus l'énergie photonique est élevée. Les sources précédentes donnaient de l'énergie en unités d'électrons volts, c'est l'énergie habituelle des réactions chimiques. L'énergie photonique pour une onde de 13,5 nm est de 92 électrons volts. Il s'agit de l'énergie de liaison des électrons profonds. En absorbant un tel photon, l'électron devient très "chaud", commence à se précipiter, rayonne un excès d'énergie et provoque une exposition secondaire loin de la fenêtre. Par conséquent, la sélection d'une résine photosensible avec l'ensemble de paramètres souhaité est également une tâche difficile.

Résultats de la simulation de Monte Carlo du voyage des électrons dans le silicium avec des énergies de 20 et 5 eV. Source

Résultats de la simulation de Monte Carlo du voyage des électrons dans le silicium avec des énergies de 20 et 5 eV. SourceCes difficultés ont déterminé les raisons pour lesquelles elles ont reporté la transition vers EUV jusqu'au dernier.

Méthodes réelles de lutte contre la diffraction

Ainsi, jusqu'à récemment, le même UVI avec une longueur d'onde de 193 nm était utilisé comme source de rayonnement. Jusqu'à la technologie de 10 nm et 7 nm. Et maintenant, nous rappelons que le rayonnement ne peut pas pénétrer dans l'espace si sa largeur est inférieure au quart de la longueur d'onde. Pour 193 nm, c'est 48 nm. La question se pose -

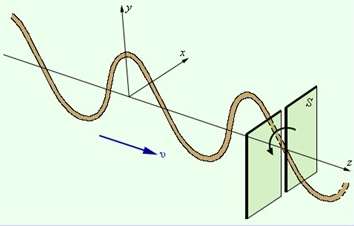

COMMENT?!C'est le petit miracle que les ingénieurs ont fait. Ils ont utilisé la méthode de polarisation de rayonnement.

Nous prenons un espace étroit rectangulaire (d'une largeur inférieure à un quart de la longueur d'onde) et dirigons la lumière vers lui, polarisée le long de l'axe. La lumière passera à travers l'espace; même la diffraction dans le sens transversal sera négligeable.

Et maintenant, nous prenons 2 fentes perpendiculaires: horizontale et verticale. Tout d'abord, nous irradions une résine photosensible à deux composants avec de la lumière polarisée à travers une fente verticale, puis à travers une horizontale. Seule la zone irradiée 2 fois apparaît. Comme tout ingénieux.

Certes, vous devrez utiliser 2 fois plus de modèles de photos et 2 processus d'exposition pour créer une seule fenêtre. Mais vous pouvez utiliser les bonnes vieilles optiques à quartz et les résines photosensibles éprouvées pendant des années.

C'est une torsion!Il existe d'autres moyens de lutter contre la diffraction ...

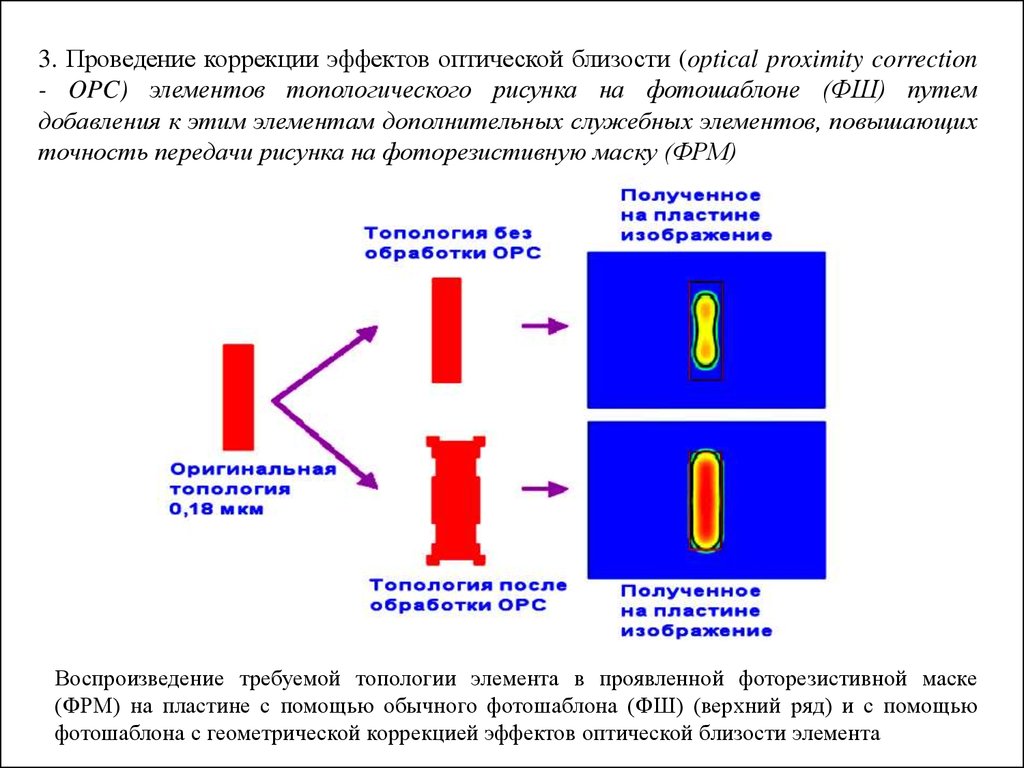

Correction de proximité optique. La forme des fenêtres du photomasque est rendue non rectangulaire pour compenser les défauts lors de la diffraction.

La méthode de correction optique de proximité est schématique ...

L'utilisation de masques déphaseurs. Sur les côtés de la fenêtre principale du photomasque, faites du matériel auxiliaire, dont le matériau décale la phase de l'onde. Lorsque des ondes sont appliquées (

interférence ), elles coupent partiellement les déplacements latéraux les uns des autres.

Éclairage hors axe.

Éclairage hors axe. Le faisceau ne tombe pas perpendiculairement à la surface de la plaque, mais à partir de deux sources légèrement inclinées. Lors de l'application des sources, les déplacements latéraux sont partiellement compensés.

Exposition multiple. Par exemple, nous devons exposer six fenêtres voisines. Nous conduisons d'abord l'exposition de 1, 3 et 5 fenêtres. Et puis 2, 4 et 6. Cela augmente le nombre de cycles d'exposition et de modèles de photos de 2 fois, mais toujours mieux que rien. Compte tenu de la polarisation horizontale et verticale, nous obtenons 4 cycles d'exposition pour créer une couche.

Ainsi, si nous regardons le masque photographique moderne, nous ne verrons pas les zones du microcircuit sous une forme explicite. Il y aura un ensemble de figures horizontales et verticales qui, superposées, donneront une image. En fait, des caractères chinois solides: c'est peut-être pour cela que les Chinois ont occupé la production de microélectronique?!

Après 45 nm, ils sont passés à la photolithographie par immersion. C'est lorsque l'espace entre la lentille extrême et la résine photosensible est rempli de liquide. Au début, c'était de l'eau. Maintenant des fluides spéciaux avec un indice de réfraction élevé (jusqu'à 1,8). Le liquide réduit la longueur d'onde effective et neutralise la réfraction de la lumière à l'interface du média.

C'est ainsi qu'ils ont atteint la résolution de ~ 10 nm. Mais cela semble être la limite pour la lithographie à 193 nm.

Photo de la première couche de métallisation pour la technologie 24 nm. A gauche, créé par lithographie à 193 nm, à droite expérimental 13,5 nm (EUV). Comme vous pouvez le voir, à partir des formes rectangulaires claires précédentes, il n'y a que des souvenirs. Fonctionne toujours.

Photo de la première couche de métallisation pour la technologie 24 nm. A gauche, créé par lithographie à 193 nm, à droite expérimental 13,5 nm (EUV). Comme vous pouvez le voir, à partir des formes rectangulaires claires précédentes, il n'y a que des souvenirs. Fonctionne toujours.À propos des limitations physiques, comment elles affectent et comment elles ont changé la production

dans la deuxième partie en quelques jours - restez à l'écoute!

N'oubliez pas de vous abonner au

blog : ce n'est pas difficile pour vous - je suis content!

Et oui, veuillez écrire sur les lacunes notées dans le texte du MP.