Dans la

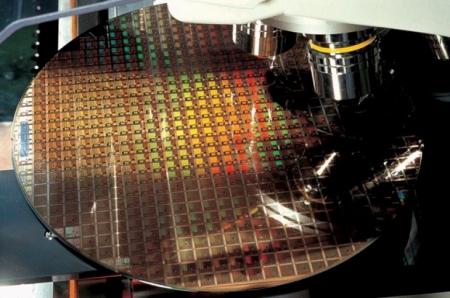

première partie, nous avons brièvement examiné la physique du silicium, la technologie microélectronique et les limites technologiques. Parlons maintenant des limitations physiques et des effets physiques qui affectent la taille des éléments d'un transistor. Il y en a beaucoup, alors passons en revue les principaux. Ici, vous devez entrer dans la physique, sinon rien.

Avertissement: Il

était une fois j'ai essayé d'écrire des articles sur

la fabrication de puces , et

dans la série d'articles "Inside Look", j'ai même regardé à l'intérieur, c'est-à-dire Le sujet est extrêmement intéressant pour moi. Naturellement, j'aimerais que

l' auteur de l'article original le publie sur Habré, mais en ce qui concerne l'emploi, il m'a permis de le transférer ici. Malheureusement, les règles Habr ne permettent pas le copier-coller direct, j'ai donc ajouté des liens vers des sources, des images et un petit gag et j'ai essayé de redresser un peu le texte. Oui, et je connais et respecte les articles (

1 et

2 ) sur ce sujet de l'

amartologie .

Effets physiques en microélectronique

L'ordre des quantités de base pour le silicium

La concentration des atomes de silicium dans le cristal est de 10

22 cm

-3Concentration d'électrons intrinsèques et de trous à température ambiante - 10

10 cm

-3Concentration d'atomes d'impuretés provenant de régions légèrement dopées - 10 16-10

18 cm

-3Concentration d'atomes d'impuretés provenant de régions fortement dopées - 10 19-10

20 cm

-3La concentration d'atomes d'impuretés dans les régions très fortement dopées est de 10

21 cm

-3 . Dans ce cas, on parle déjà d'un

semi -

conducteur dégénéré , car une telle concentration (un atome d'impureté pour 10 atomes de silicium ou moins) modifie la structure énergétique du cristal.

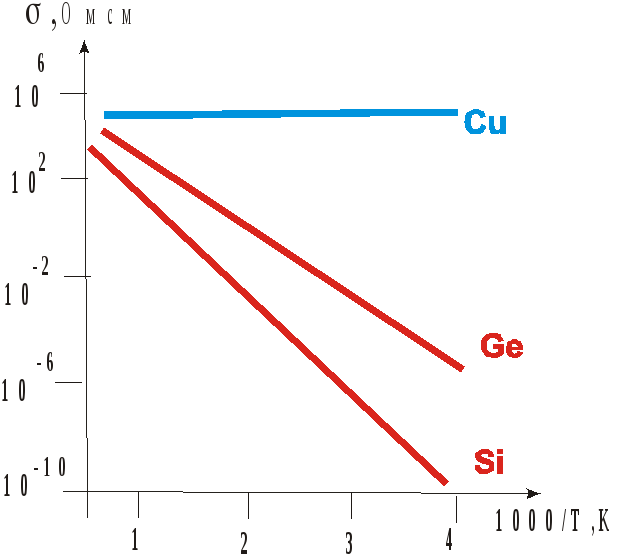

Dépendances en température des caractéristiques du silicium

De la première partie, nous rappelons qu'à température ambiante, le silicium pur est un diélectrique. Une paire électron-trou apparaît dans un seul cas sur un billion, mais cette fraction augmente de façon exponentielle avec l'augmentation de la température. Il y a une telle chose - la température de doubler la concentration de propres porteurs de charge. Pour le silicium, c'est environ 9 degrés.

C'est-à-dire augmenter la température de 9 degrés, le pourcentage d'atomes de silicium en décomposition augmente de 2 fois; 18 degrés - 4 fois; 27 degrés - 8 fois; 36 degrés - 16 fois; 45 - 32 fois; 90 - 1024 fois; 180 - 10

6 fois; 270 - 10

9 fois.

Comparaison de la conductivité thermique du cuivre, du silicium et du germanium. Source

Comparaison de la conductivité thermique du cuivre, du silicium et du germanium. SourceNous obtenons que lorsqu'elle est chauffée à 200 degrés (~ 2,1 dans le graphique ci-dessus), la concentration intrinsèque des paires électron-trou devient 10

16 , ce qui est égal à la concentration en impuretés des couches légèrement dopées. À 300 degrés (~ 1,75) déjà 10

19 , c'est la concentration de couches fortement dopées (n + et p +). À cette température, le silicium se transforme en fait en conducteur et les transistors perdent leur contrôlabilité.

Les problèmes commenceront beaucoup plus tôt. La température dans la puce est inégale. Il y a des zones de chauffage locales, généralement au milieu de la puce. Si la température dans une petite zone dépasse 200 degrés, alors en raison d'une augmentation de la conductivité intrinsèque du silicium, le courant de fuite commence à augmenter. Cela conduit à encore plus de chauffage, ce qui augmente encore le courant de fuite et élargit la zone de surchauffe. Le processus devient irréversible et ... boom. Et irrévocablement. Par conséquent, sur tous les grands microcircuits, une protection automatique contre la surchauffe est définie.

C'est pourquoi il est si important de ne pas permettre un fort réchauffement du cristal.

A titre de comparaison, la concentration d'électrons intrinsèques et de trous dans le nitrure de gallium à température ambiante est inférieure de plusieurs ordres de grandeur, et la température de doublement du nombre de porteurs de charges intrinsèques est d'environ 25 degrés. Les problèmes décrits ci-dessus dans le nitrure de gallium commencent à environ 600-700 degrés.

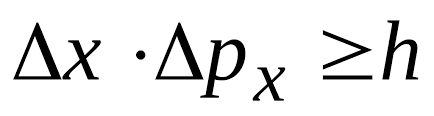

Courant du tunnel

Ce phénomène est à la fois complexe et simple à la fois. Les racines se trouvent dans la nature quantique de l'électron. Un électron vit selon les lois de la mécanique quantique, qui ne sont pas toujours comprises du point de vue de la physique classique. Selon ces lois, un électron n'est pas seulement une particule, mais aussi une onde, et son comportement ne peut être calculé qu'avec une certaine probabilité. Il existe une telle formule Heisenberg:

On l'appelle également

la relation d'incertitude de Heisenberg . Il résulte de la formule que les paramètres spatiaux de l'électron ne peuvent pas être déterminés avec une précision supérieure à une certaine valeur (constante de Planck). Dans les cas extrêmes de l'équation, si nous connaissons l'emplacement exact de l'électron, nous ne saurons rien de sa vitesse et de sa direction de mouvement. Si vous connaissez exactement la vitesse et la direction, rien ne saura où il se trouve. Il s'avère que l'électron est une telle particule floue dans l'espace avec des pics de probabilité d'être. À tout moment, un électron peut être n'importe où dans l'Univers sans aucune influence extérieure. Certes, la probabilité de son apparition est très loin de l'emplacement actuel est extrêmement faible.

Imaginez maintenant la structure du type métal - diélectrique - semi-conducteur n (MIS). Dans un métal, la concentration d'électrons libres est approximativement égale à la concentration d'atomes (10

22 / cm

3 ). Ils ne peuvent pas pénétrer dans un diélectrique, car pour les électrons d'un métal, c'est une région d'énergies interdites. À l'intérieur du diélectrique, une onde électronique avec de l'énergie comme dans un métal va commencer à interférer (s'autodétruire). Mais ils peuvent se matérialiser dans un semi-conducteur de type n, où il y a pour eux une zone d'énergies autorisées. Les électrons passent d'un métal à un semi-conducteur à travers une couche d'oxyde sans aucune influence extérieure, simplement en raison de leur nature probabiliste. Ceci est le

courant du

tunnel . Le processus lui-même est appelé tunneling, ou tunnel quantique (ça sonne plus cool!).

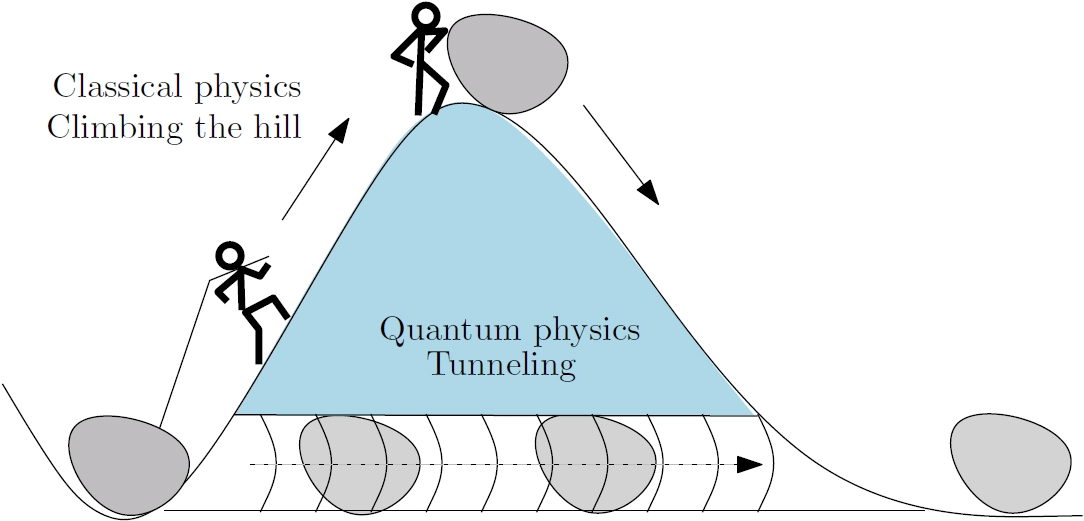

L'énergie supplémentaire qui devrait être ajoutée à l'électron pour une pénétration «classique» dans l'oxyde s'appelle la barrière de potentiel. Schématiquement, un électron ronge un tunnel à travers une barrière de potentiel.

Il y a un flux dans la direction opposée - d'un semi-conducteur à un métal. Mais comme la concentration d'électrons libres dans le semi-conducteur est inférieure de plusieurs ordres de grandeur, le flux inverse est proportionnellement plus petit.

Un semi-conducteur de type p pour les électrons d'un métal est également une bande d'énergies interdites. Cependant, le processus inverse est possible ici - la tunnellisation des électrons de valence d'un semi-conducteur à un métal avec l'apparition de trous dans le silicium. Il semble que les trous creusent un tunnel en métal. L'intensité, toutes choses étant égales par ailleurs, est environ 10 fois inférieure à la tunnelisation des électrons libres.

Le courant tunnel pour des distances supérieures à 1 μm peut être négligé. Probabilité trop faible et transitions trop rares. À mesure que la distance diminue, la probabilité de transitions spontanées augmente fortement. À des distances d'unités de nm, le courant de tunnel augmente 10 fois à l'approche de 0,2 nm.

Un mécanisme similaire fonctionne pour les couches de silicium npn. Pour un électron libre de la région n, la région p est une bande d'énergies interdites, aucune transition ne se produit. Mais si la largeur de la base p est trop étroite, les électrons commencent à se creuser un tunnel directement de la source au puits. Cela limite la largeur de base maximale théorique à 8 nm. À des tailles plus petites, en raison du courant tunnel, le transistor source-drain devient en principe incontrôlable.

Pour les structures pnp, la situation est similaire, mais les trous (électrons de valence) tunnelent.

Dans les semi-conducteurs dégénérés (fortement dopés) dans la bande des énergies interdites, il existe des îlots d'énergies autorisées. Pour eux, l'option de creuser des tunnels à travers ces îles est possible. Comment surmonter un ruisseau en sautant sur des rochers collants.

Région de charge spatiale (SCR)

La région de charge d'espace (SCR), c'est aussi la région d'épuisement, c'est aussi la région de charge d'espace - c'est une couche chargée électriquement qui se forme à la frontière des régions n et p.

Connectez mentalement 2 morceaux de silicium, l'un de type n, l'autre de type p. Dans la couche n il y a beaucoup d'électrons libres, dans la couche p il y a beaucoup de trous, ils se déplacent de manière aléatoire. Une partie des électrons libres va à la couche p, une partie des trous à la couche n. En conséquence, les ions positifs non compensés restent dans la couche n et les ions négatifs ne sont pas compensés dans la couche p. Un champ électrique local apparaît le long de la frontière des régions, ce qui commence à entraver de nouvelles transitions. L'intensité du champ est maximale à la frontière et diminue progressivement avec la distance. En fin de compte, l'intensité du champ devient telle que le transfert des trous et des électrons cesse et qu'un état d'équilibre s'établit. Pour le silicium, la tension d'un tel champ interne est d'environ 0,5 volt. Dépend de la concentration d'impuretés des deux côtés. La dépendance est faible, environ 0,1 volt lorsque la concentration change de 10 fois.

En plus de l'apparition d'un champ électrique à la frontière, il y a une diminution de la concentration d'électrons libres et de trous. Directement à la limite des couches à zéro. D'où le deuxième nom - «région appauvrie». La largeur de cette région dépend de la tension à la transition et de la concentration d'impuretés. La dépendance à la concentration d'impuretés est inversement quadratique, c'est-à-dire avec une augmentation de la concentration d'un facteur 100, la largeur du SCR diminue d'un facteur 10 (en fait, légèrement moins, car la tension à la jonction augmente).

Il s'agit d'un état dans lequel aucune tension externe n'est appliquée à la structure.

Si vous appliquez une tension externe, elle est vectorisée avec la tension interne.

Nous appliquons une petite tension directe à la jonction, c'est-à-dire plus (+) à la couche p, moins (-) à la couche n. Les champs externes et internes sont dirigés dans des directions différentes et commencent à se compenser. La tension de transition et la largeur du SCR sont réduites. Lorsque la tension du champ externe devient supérieure à celle interne, le SCR disparaît, la jonction pn s'ouvre complètement. Pour les diodes semi-conductrices, il existe même un tel paramètre - tension de seuil. Il s'agit de la tension directe à laquelle la diode s'ouvre complètement.

Appliquez maintenant la tension inverse: moins (-) à la couche p, plus (+) à la couche n. Les champs externes et internes s'additionnent, la tension à la jonction et la largeur du SCR augmentent.

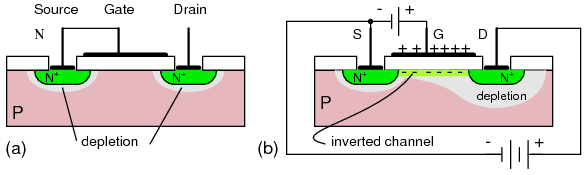

Si nous transférons ce modèle sur notre transistor à effet de champ, nous obtenons l'image ci-dessous:

Le rose clair indique les zones appauvries (SCR). Nous obtenons que la largeur réelle de la

base active , qui est contrôlée par la tension de grille, est inférieure à la distance source-drain. Autrement dit, la taille de la base moins la largeur des transitions SCR. En l'absence de tension d'alimentation, la largeur du SCR de la source et du drain est la même. Si vous appliquez la tension de fonctionnement, la largeur du SCR du drain augmente, car elle est sous polarisation inverse. La base active se rétrécit encore plus:

Si la base est trop courte, le SCR du drain et de la source sont connectés. La largeur de la base active devient 0, un courant traversant s'écoule du drain vers la source, le transistor s'ouvre. Quelle que soit la tension sur l'obturateur. Le transistor devient incontrôlable. L'effet est appelé «piqûre de base» (

note: comme F376 l'a correctement noté , il s'agit très probablement de «panne de base»).

Il existe toujours une option intermédiaire lorsque le SCR ne se ferme pas, mais la distance de la source à la limite du SCR du ruissellement est inférieure à 8 nm. Ensuite, dans le SCR, les électrons commencent à tunneler depuis la source. Une fois dans le SCR, ils sont jetés dans le drain par un champ électrique. Autrement dit, un courant tunnel décent circulera de la source au drain.

Panne d'avalanche

Si le champ électrique à l'intérieur du SCR devient trop élevé, alors un électron qui y vole accidentellement accélère tellement qu'il enlève l'électron d'un atome neutre. 2 électrons apparaissent, ils accélèrent à nouveau et retirent les électrons des éléments suivants, etc. Le processus ressemble à une avalanche, d'où le nom. Un canal conducteur apparaît dans le SCR à travers lequel le courant passe. Le transistor s'ouvre spontanément.

Une situation similaire peut se produire dans le diélectrique de grille. Si l'intensité du champ est supérieure au seuil, un électron «rapide» sortant du métal accélère et provoque une avalanche.

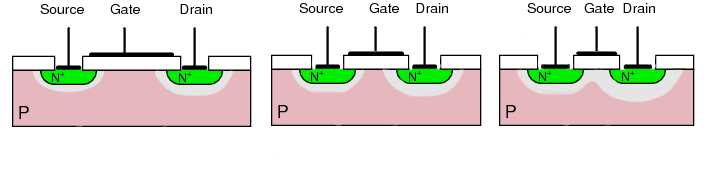

Une comparaison claire des différents types de pannes. Source

Une comparaison claire des différents types de pannes. SourcePour éviter une telle panne d'avalanche, il est nécessaire d'éviter des intensités de champ excessives supérieures à la valeur de panne. Intensité du champ = Contraintes / Longueur. C'est-à-dire il est nécessaire de réduire la tension et d'augmenter la largeur du SCR (ou l'épaisseur du diélectrique).

Zones de résistance électrique

C'est déjà un génie électrique classique. Et le drain, et la source, et le canal, et même les pistes métalliques conductrices ont leur propre résistance électrique. La résistance est plus élevée, plus la longueur de la parcelle est grande et plus la section transversale est petite.

Supposons que tous les éléments du transistor soient réduits proportionnellement de 2 fois. En réduisant la longueur, la résistance de la section

est réduite de 2 fois , et en réduisant la largeur et la hauteur

augmente de 4 fois . Au total, cela donne une

augmentation de la résistance de l'élément de 2 fois . Avec le passage du courant, la résistance provoque une chute de tension. Pour des tensions de transistor de l'ordre de 1 V et moins, même une petite chute de tension sera critique.

Pour la métallisation, cette question a été résolue simplement - la première couche étroite de métal relie uniquement les éléments à l'intérieur de la cellule. Tout le reste est porté aux niveaux supérieurs de métallisation: là, la couche d'oxyde est rendue plus épaisse et les pistes plus larges. Néanmoins, la taille des fenêtres de contact et des pistes de métallisation ne peut pas être infiniment réduite.

Pour les zones de silicium, une augmentation de la résistance a été compensée par une augmentation de la concentration d'impuretés. Du moins jusqu'à récemment, jusqu'à ce que les effets du tunneling et de la panne commencent à affecter.

Un autre moyen était la technologie du «silicium étiré» ou «silicium contraint». Son essence est qu'une couche de germanium est déposée sur un substrat de silicium. Le germanium est un élément du même groupe que le silicium, de structure cristalline similaire. Cependant, les atomes de germanium sont plus grands, respectivement, la distance entre eux dans le réseau cristallin est plus grande. Ensuite, un mince film de silicium épitaxial se forme sur le germanium. Le silicium dans le film commence à répéter la structure cristalline du germanium, l'étape du réseau cristallin sera à la fois dans le germanium et plus grande que dans le silicium ordinaire. Il s'avère que le silicium est, pour ainsi dire, étiré dans toutes les directions. D'où le nom. Cela donne une augmentation de la mobilité des électrons et des trous.

L'effet combiné des effets physiques

Examinons maintenant ensemble les effets de ces effets.

La principale menace dans la miniaturisation des transistors est une base de perforation. Pour le retirer, vous devez réduire la largeur du SCR. Il peut être réduit en réduisant les contraintes externes et en augmentant la concentration d'impuretés dans la base.

La tension d'alimentation n'a nulle part à réduire, elle est déjà de l'ordre de 1V - environ deux seuils. Si nous en faisons encore moins, nous risquons alors d'obtenir une ouverture «brouillée» des transistors en raison de la résistance électrique.

Vous pouvez augmenter la concentration d'impuretés dans la base de données, mais nous obtenons alors:

- une forte augmentation du courant de fuite tunnel du drain à la base;

- risque accru de rupture d'avalanche de la transition;

- augmenter le seuil de tension pour induire le canal, avec le risque d'obtenir une panne du diélectrique de grille.

En raison de ces limitations, la

concentration d'impuretés dans la base est fixée à 10 18-10 19 .

Tous ces facteurs et des facteurs non nommés limitent la

largeur de base minimale des transistors MOS au silicium dans la région de 25 nm . C'est moins possible, mais le courant de fuite devient insuffisant et la probabilité de défaillance augmente de façon exponentielle.

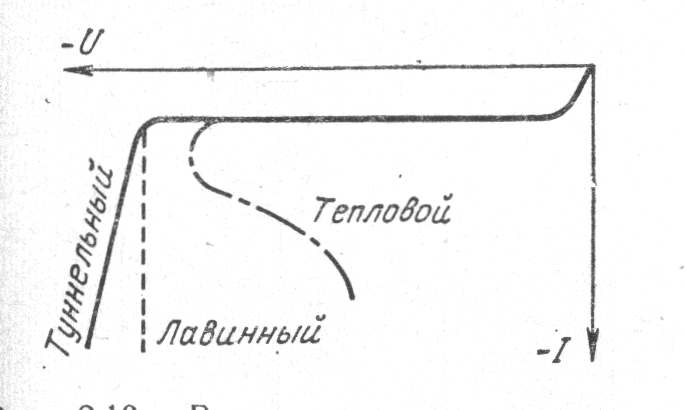

Micrographie de transistors réalisée sur une technologie de processus à 90 nm et 32 nm. Le zoom et l'échelle sont identiques. Source

Micrographie de transistors réalisée sur une technologie de processus à 90 nm et 32 nm. Le zoom et l'échelle sont identiques. SourceComme nous pouvons le voir, la taille des contacts métalliques est devenue beaucoup plus petite, mais la largeur de la base n'a pas changé. Tout de même 25 nm. De plus, pour les transistors utilisant la technologie du 14 nm, 10 nm et 7 nm, c'est la même chose (

ooops! ).

Cela a été rencontré pour la première fois lors du passage de 130 nm à la première série de 90 nm. Ensuite, pour la première fois, ils n'ont pas pu réduire la largeur de la base proportionnellement à toutes les autres tailles, elle est restée d'environ 35 nm. Plus tard, il était encore réduit à 25 nm, mais depuis lors, la largeur de la base n'a plus été soumise aux proportions de la technologie. Et plus les transistors devenaient petits, plus cela se manifestait.

Il fallait changer les critères des processus techniques. Qu'avez-vous fait? La plupart n'ont rien fait. Ils ont continué à délivrer l'autorisation de photolithographie comme la norme du processus technologique. Ou la largeur minimale du chemin de métallisation comme manifestation de l'opération la plus simple et intuitive. Et puis nous passons au marketing ...

Les spécialistes du marketing les plus créatifs venaient d'Intel. Ils ont commencé à calculer le taux de processus technique à partir de la taille des éléments, par exemple, sur la base de la zone de la cellule à six transistors de la mémoire statique. Dans la technologie avec une résolution de lithographie de 65 nm, elle était de 0,77 μm

2 , et à une résolution de 40 nm, elle est devenue de 0,37 μm

2 . Si la taille des transistors a été réduite proportionnellement comme auparavant, cela correspond à la technologie de 45 nm. Nous supposerons donc que nous avons la technologie 45 nm. C'est de là que viennent les écarts entre la technologie Intel et les autres - 28 nm pour tous, 32 nm pour Intel; 20 nm pour tous, 22 nm pour Intel; 10 nm pour tous, 14 nm pour Intel.

Comme l'histoire ultérieure l'a montré, Intel a fini par être plus honnête que ses concurrents.

Effet des courants de fuite

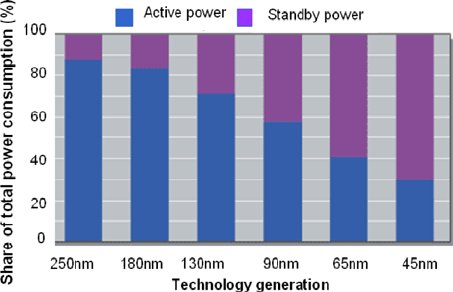

Il y a un merveilleux calendrier d'un article déjà en 2010:

Source

SourceLe graphique montre le pourcentage de consommation d'énergie de travail et parasite. Bleu - dégagement d'énergie dû aux courants de recharge (courant de fonctionnement), violet - résultat de courants de fuite (courant parasite). Cela tient compte des mesures qui ont été prises pour réduire les courants vagabonds.

La raison pour laquelle la croissance des vitesses d'horloge du processeur s'est arrêtée est clairement visible. Les premiers processeurs à 3 GHz (

Pentium 4 par exemple) sont apparus au début des années 2000. Donc, à ce niveau et est resté. Habituellement, cela s'explique par le fait que le nombre de cœurs a augmenté, la logique est devenue plus compliquée, le pipelining s'est approfondi, de sorte que les exigences de stabilité et, en général, de bonheur en gigahertz ont augmenté. En partie vrai.

Mais! - .

, . , 2 , 4 , 6-7 . , , -. . , .

.

180 130 . , , .

. - , , . , 45 .

, 2000- .

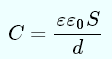

, — .High-k . , NiSi. - .

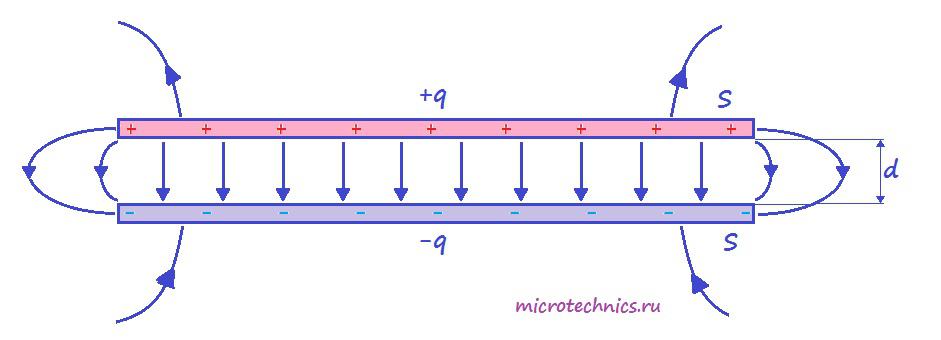

High-k. . , . , , . – – .

— . . , . . . :

S – ,

d – ,

ԑ – , 1, 1,

ԑ

0 – .

, . , . 1,2 (

sic! ). 6

(!!!) . . 5 , .. 1 , 10 (

!!! ) ( 10 0,2 ). .

– . — High-k . HfO

2 Ta

2 O

5 . 3.9, High-k 25-30. , , - .

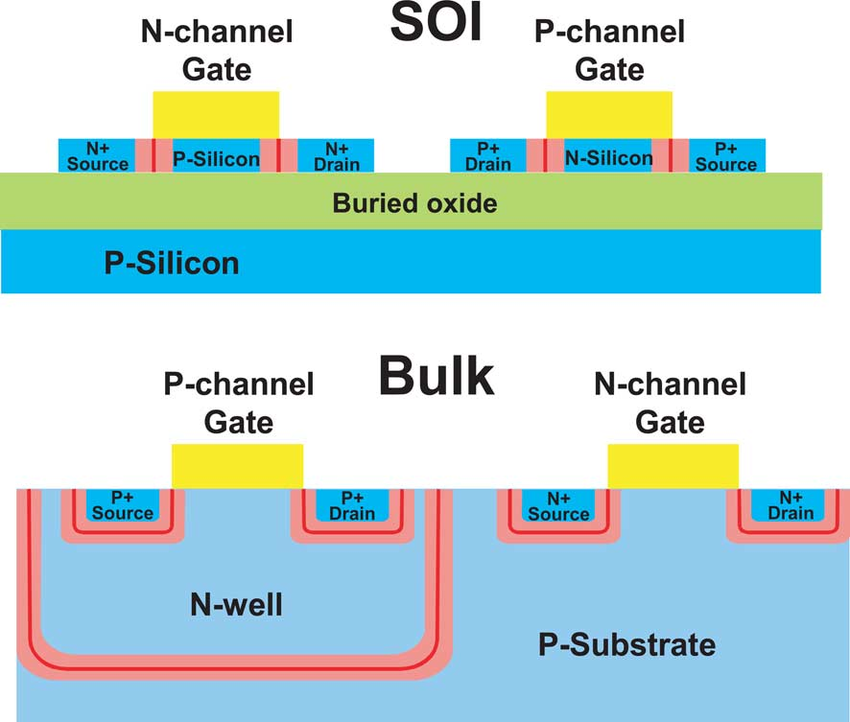

(SOI)

, , SOI, . : , (

UPD: , ,

SIMOX Smart Cut ).

SOI-

SOI-.

. . , - , . . . , .

Al

2 O

3 , . , . High-k 15 . .

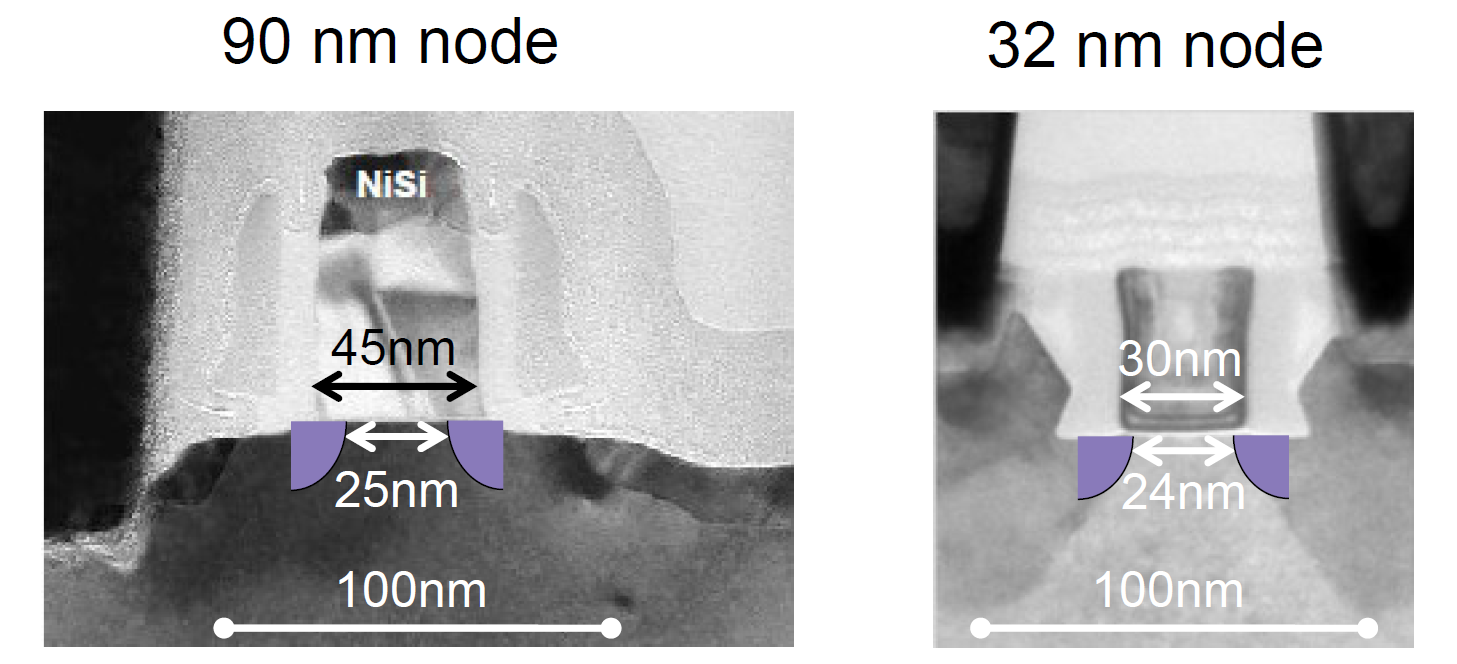

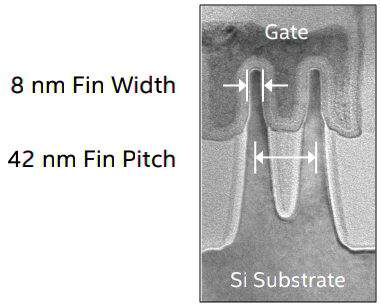

FinFET

Fin – , . 22 . , , .

UPD: FinFET

a5b , «».

, . Source

, . Source — . Source

— . Source. , () , . , , , . , .

- () . , .

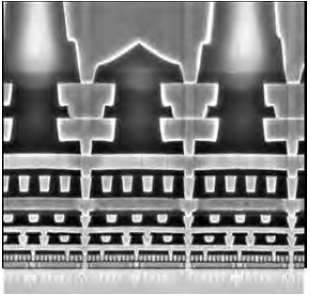

. 6 , 3 n-, 3 p- ( Fin ), (Gate), . , , ( 25 ), . . , 22 54 , 14 – 42 , 10 – 34 . .

3 , . Intel, Samsung TSMC. AMD – GlobalFoundries – . AMD TSMC Samsung.

, . , --. . , . . . , – , . , .

?! , . FinFET . High-k , , . . . C'est-à-dire .

C'est-à-dire . , 7 22 . FinFET 22 , 7 3 , . , , 10 7 1,8 . …

? . , Samsung GAAFET 5 .

CMOS, FinFET GAAFET . Source

CMOS, FinFET GAAFET . SourceC'est-à-dire

le peigne ne doit pas être continu, mais divisé en fils séparés. Question: Le jeu en vaut-il la chandelle? - reste ouvert. UPD: comme F376 l'a correctement noté , FinFet fournit une entrée d'un champ électrique de deux parties. Le FET Gate-All-Around permet une entrée dans toutes les directions, ce qui est plus efficace.Il existe également des options pour volets roulants, verticaux, etc. Il existe des combinaisons de FinFET et SOI. En général, les processus chimiques de l'épitaxie sont plus complexes, mais plus linéaires et prévisibles que la lithographie. Il fournit utilisé pour une plus grande précision et la capacité de créer plus subtile structure en trois dimensions.La situation sur le marché moderne des fabricants de microprocesseurs et les perspectives

Ainsi, les trois leaders se sont démarqués - Intel, Samsung et TSMC. Intel produit sous ses propres marques, le reste est principalement sur commande. Sous les marques AMD, NVIDIA, Qualcomm, Apple, IBM se cachent des puces fabriquées dans les usines TSMC ou Samsung. Certains anciens chefs sont tombés ou se sont heurtés à une barrière. Les Chinois tentent de percer dans la ligue, mais jusqu'à présent avec peu de succès: ils manquent de leur propre base technologique, et les leaders mondiaux de la production d'équipements gardent les dernières lignes technologiques pour les Chinois.

L'optimisme des experts est associé à la transition vers des structures en vrac et au début de l'utilisation de la lithographie EUV. Samsung et TSMC ont commencé à l'utiliser dans une mesure limitée, pour les structures les plus délicates. Cela leur donne la possibilité de faire rapport sur la réalisation de normes de 7 nm et à l'avenir jusqu'à 5 nm. Bien que, comme déjà décrit, ces chiffres aient en fait peu d'effet. Le même Intel a généralement abandonné EUV. Apparemment, ils ne croient pas que cela améliorera considérablement les performances.

D'un autre côté, les personnes concernées comprennent que l'ère Moore est révolue et chaque nouvelle étape de la croissance de la productivité nécessitera plus d'efforts et de temps. La croissance rapide de la microélectronique prend fin (

sanglot! ). Comment cela s'est-il produit une fois dans l'industrie automobile et l'aviation? Après une croissance explosive, un développement lent s'ensuit.

Parmi les percées prometteuses, on peut distinguer la transition vers un autre matériau (pas le silicium) et la création de microcircuits multicouches (intégration 3D - salut aux idées d'AMD). Pour l'intégration 3D, vous devrez réduire considérablement la génération de chaleur ou améliorer la dissipation thermique.

C'est tout pour les tailles de transistor. Il existe d'autres réserves de croissance de la productivité dans un autre. Dans l'optimisation de l'architecture, par exemple. Vous pouvez même faire un pas de marketing en disant qu'un nouveau processeur avec une architecture améliorée fonctionne comme s'il était un ancien avec la technologie 0,5 nm. Par conséquent, nous le marquons comme 0,5 nm. Et je pense avec lui que les dimensions des transistors sont les mêmes.

Il est possible de créer de nouveaux types de cellules à partir de combinaisons de transistors. Par exemple, au lieu de 6 cellules de mémoire à transistor, faites 2 structures de transistor avec une physique complexe d'influence mutuelle. Les structures volumétriques offrent ici de nombreuses opportunités.

Limites physiques

Quelqu'un peut dire que le pessimisme de l’auteur n’est pas justifié. Ils trouvent des moyens de contourner les restrictions. Peut-être pas aussi vite qu'avant, mais néanmoins.

Le fait est qu'il existe encore des processus physiques qui ne peuvent pas être contournés. Les principaux sont la matière composée d'atomes et les porteurs de charge sont les électrons. Créer un transistor plus petit qu'un atome ne fonctionne pas. Cela ne fonctionnera pas pour créer encore moins de 1000 atomes. Parce qu'il y a un électron et la relation d'incertitude de Heisenberg. Un électron est une particule très instable, un comportement plus ou moins stable n'est possible que pour un réseau de milliers et de millions d'électrons. Sur un électron, vous ne pouvez détruire que le chat Schrödinger.

Remarque: bien qu'il y ait des développements sur les transistors à électron unique (

1 ,

2 et

3 )

Même aux tailles actuelles, des collisions se produisent en raison du fonctionnement spontané des transistors. Si la probabilité d'une collision est de 10

-9 (une par milliard), alors avec le nombre d'éléments en milliards et les fréquences en GHz, cela donne en moyenne 1 collision par cycle, ou plusieurs milliards de collisions par seconde. Pour les détecter, il existe des systèmes de surveillance de l'intégrité des opérations et une opération suspecte est envoyée pour réexécution.

Avec la miniaturisation, le nombre de collisions commence à augmenter très fortement. En conséquence, nous arrivons à une situation d'effet nul, voire négatif, de la miniaturisation. C'est-à-dire les transistors ont fait moins, ils s'insèrent davantage dans le cristal, mais en raison de la croissance des collisions et des cycles de retraitement, la productivité totale n'a pas augmenté. Ou peut-être même tombé. Et ce seuil est tout à fait à l'horizon.

Quelques mots sur la microélectronique numérique domestique

Contrairement à la croyance populaire, jusqu'en 1985, le retard de l'URSS par rapport aux dirigeants n'était pas si important. Environ 3-4 ans. C'est le cas si nous prenons les

principales entreprises de Zelenograd (note:

BarsMonster a écrit sur Micron

à l'époque ). Selon la loi de Moore, même un décalage de 3 à 4 ans a considérablement affecté les performances. Il y avait des problèmes pour obtenir de l'oxyde de haute qualité, avec la clarté des jonctions pn. Si nous ajoutons à cela une politique conservatrice avec l'emballage des puces dans un boîtier (les longues lignes de contact n'ont pas augmenté la productivité des appareils), ainsi que les normes soviétiques pour la production de cartes et de boîtiers avec un tas de fer (ceux qui ont démonté les magnétophones soviétiques comprendront), nous obtenons une blague sur la puce soviétique avec de la fonte poignées pour le transport.

Il y a plusieurs raisons à l'arriéré. Startanuli plus tard, ressources limitées, ressources de pulvérisation. Lorsque les Américains se sont concentrés sur le CMOS, le nôtre a continué d'expérimenter diverses technologies. Ils ont travaillé assez activement avec des alternatives au silicium, principalement avec des matériaux A

3 B

5 . Eh bien, l'assouplissement général des derniers instituts de recherche soviétiques.

Après 1985, les Américains ont commencé brusquement et nous avons commencé à avoir des problèmes. Puis les années 1990, lorsque la vie dans l'industrie était chaude par inertie. En conséquence, ils sont entrés dans le 21e siècle avec la technologie 800 nm, alors que les dirigeants avaient déjà pris d'assaut 130 nm. La seconde vie de l'industrie a été donnée par la chipisation de masse des cartes et des commandes gouvernementales. La principale production d'acier: puces pour cartes SIM, cartes bancaires, cartes de paiement, cartes de transport et de réduction et autres biens de consommation. De gros gigahertz et de petits nanomètres n'y sont pas nécessaires.

Remarque: à propos, alors qu'à Moscou il y a des billets uniques (achetés-jetés, chargés dans une usine), dans la même Chine, ils promeuvent activement les technologies économes en ressources, en particulier, l'utilisation réutilisable du "jeton" dans le métro (même pour un court voyage) .

Vidéo sur le métro de Shenzhen

Néanmoins, il y a une tentative d'entrer dans la «grande ligue» de la microélectronique. Le développement va dans quatre directions principales.

- Processus techniques "souverains". Une tentative de créer un cycle de production complet sur les équipements domestiques et nos propres processus technologiques. Nous suivons la même voie que les dirigeants ont empruntée il y a 20 ans, mais en tenant compte du rake trouvé et des solutions. Parmi ces derniers, ce qui était dans les sources ouvertes est de 250 nm dans la série et 150 nm dans le processus de mise en œuvre. Cela comprend également une tentative de créer nos propres installations de lithographie EUV à 13,5 nm et ainsi de sortir immédiatement sinon dans les grandes ligues, puis à proximité d'eux.

- Achat de lignes technologiques auprès de grands fabricants. Le problème ici est que les installations les plus modernes ne nous ont pas été vendues même dans les meilleures années. Habituellement, ils vendent des lignes obsolètes qui ont été abandonnées. Maintenant, à propos des sanctions, encore plus. Ici, nous pouvons rappeler l'épopée avec l'achat par Angstrom des équipements de l'usine AMD de Dresde en 2007, dans le cadre du processus de fabrication à 180 nm. Ou l'achat d'une ligne Micron 90 nm auprès de STMicroelectronics français suivi d'une mise à niveau à 65 nm. Bien qu'il s'agisse du processus de fabrication le plus fin en Russie, ils ont réussi à arracher avant les sanctions. Certes, il existe désormais une solution de contournement: l'approvisionnement via la Chine.

- Commandez la production dans des usines en Chine ou à Taiwan. En même temps, l'architecture et la topologie sont entièrement développées avec nous,

maintenant nous fabriquons même nos propres masques photo . Les Chinois ne peuvent reproduire les processus technologiques que dans leurs usines. Nous obtenons des processeurs productifs plus avancés et développons des compétences dans le développement des systèmes de processeurs les plus modernes. Ici, pas un groupe de scientifiques Kulibin n'est impliqué, mais de grandes équipes de conception. Seule la dernière section, la production, est retirée du cycle complet.

Remarque: le Baïkal est fabriqué uniquement selon les normes de 28 nm à l'usine TSMC. Un article sur la sortie du Baïkal et son analyse.

- Le développement de technologies alternatives. Il s'agit du développement de technologies prometteuses qui pourraient se généraliser à l'avenir. Cela comprend des travaux sur les composés A 3 B 5 et les hétérostructures, principalement l'arséniure et le nitrure de gallium. Ainsi que des tentatives d'optimiser la lithographie par faisceau d'électrons et rayons X pour la production de masse, ce qui supprime généralement les limites de la lithographie.

Remarque: nous avons hérité d'une solide école sur les hétérostructures de feu Alferov, mais même avec le soutien de l'État, OptoGaN ne l'a pas étirée , le marché et les conditions du marché échouent.

En général, la situation n'est pas brillante pour la microélectronique russe. Mais il y a de l'espoir que les dirigeants ralentiront inévitablement en raison de limitations physiques, et ici, nous nous dépêchant lentement, nous nous glissons derrière.

L'accord final sur la mémoire et les fenêtres d'opportunité dans la troisième partie dans quelques jours - restez à l'écoute!

N'oubliez pas de vous abonner au

blog : ce n'est pas difficile pour vous - je suis content!

Et oui, veuillez écrire sur les lacunes notées dans le texte du MP.